Fターム[5F140BB02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901)

Fターム[5F140BB02]の下位に属するFターム

段差部に形成されたもの (818)

Fターム[5F140BB02]に分類される特許

21 - 40 / 83

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加して、チャネル領域に歪みを与えるための新たな手法を提供する。

【解決手段】基板と、前記基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極の側面に設けられた側壁絶縁膜と、前記基板のソースドレイン領域に埋め込まれており、前記基板のチャネル領域に応力を印加する応力印加層であって、前記基板と前記応力印加層との界面の上端の高さが、前記基板と前記ゲート絶縁膜との界面の下端の高さよりも高いような応力印加層と、を備えることを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】溝の形状を維持しながらバリを除去するとともに、溝内壁におけるシリコン表面のダメージを除去することが可能な半導体装置の製造方法、及び該製造方法によって製造された半導体装置を提供する。

【解決手段】基板1に埋設領域Mを形成して素子分離を行なう工程と、基板1に溝7a,7b,7cのパターンを形成する工程と、溝7a,7b,7c内壁に保護膜8を形成する工程と、異方性の強い条件でエッチバックすることにより、溝7a,7b,7cのゲート垂直方向側壁7dの一部に保護膜8を残しながら、溝7a,7b,7cのゲート平行方向内壁7eの保護膜8を除去する工程と、保護膜8の除去によってシリコンが露出した領域に水素ベーク処理を行って、溝7a,7b,7cのパターン形成の際に副生されたバリ1a,1aを除去する工程と、を少なくとも有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

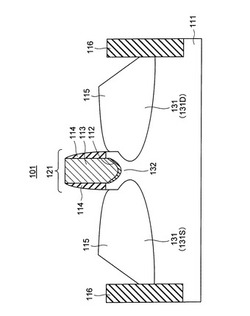

【課題】駆動能力に優れたPMOSトランジスタを実現する。

【解決手段】半導体装置は、半導体基板101における素子分離領域102によって分離された活性領域104上に形成されたPMOSトランジスタであって、このPMOSトランジスタは、活性領域104上に形成されたゲート絶縁膜105bと、ゲート絶縁膜上に形成されたゲート電極106bと、サイドウォール108bと、ソース・ドレイン拡散層領域107bとを備える。ソース・ドレイン拡散層領域107bは、半導体基板101の主面に対して傾斜面101Bを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】電界効果トランジスタのオン電流を小さくすることなく、微細化を実現することのできる技術を提供する。

【解決手段】半導体基板の主面に素子分離領域2によって周囲を規定された活性領域3が配置され、この活性領域3は、周辺部3aに凹状の段差3cを有する断面形状となっており、活性領域3の周辺部3aの半導体基板の上面は、活性領域3の中央部3bの平坦な半導体基板の上面よりも低く形成されている。活性領域3の周辺部3aに凹状の段差3cを設けることにより、この活性領域3に形成されるMIS・FETの実質的なゲート幅を増加させて、MIS・FETのドレイン電流を増加させる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に形成された拡散層および拡散層間分離絶縁膜の一部がリセスされた溝ゲート構造を有する半導体装置において、拡散層間分離絶縁膜の埋設性とチャネル抵抗の低減を両立する。

【解決手段】溝ゲート構造となる溝内において、拡散層間分離絶縁膜を拡散層に対して選択的にウェットエッチングして拡散層が突出部した構造を形成し、さらに突出した拡散層を選択エピタキシャル成長させることで拡散層の突出部に庇状の構造を形成する。

(もっと読む)

スプリット仕事関数ゲートを含むMOSFETを有する集積回路

【課題】ゲート誘起ドレインリーク電流が少ない電界効果トランジスタ、および、ゲート電極とソース/ドレイン領域との間に薄い絶縁体構造物を含む集積回路を提供する。

【解決手段】トランジスタ542のゲート電極は、ゲート電極とチャネル領域512との間の第1のフラットバンド電圧を決定する主部532と第1の側部535とを含む。この第1の側部は、上記主部に接触すると共に、上記ゲート電極と第1のソース/ドレイン領域514,516との間の第2のフラットバンド電圧を決定する。上記第1のフラットバンド電圧および上記第2のフラットバンド電圧は、少なくとも0.1eVだけ異なる。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域及び素子分離領域に形成される複数のゲートトレンチの溝幅がほぼ設計通りであり、素子の微細化が可能な半導体装置及びその製造方法を提供する。

提供する。

【解決手段】ハードマスク105hを形成する前に第1のポリシリコン膜104を形成し、且つハードマスク105hを除去する前に第1及び第2のゲートトレンチ106及び107内にゲート電極となる第2のポリシリコン膜109を埋め込む。その後、ハードマスク105hを除去するための熱リン酸によるウェットエッチングを行う。このとき、第1のゲートトレンチ106内は第2のポリシリコン膜109で保護され、半導体基板100上は第1のポリシリコン膜104で保護された状態となっている。

(もっと読む)

半導体装置とその製造方法

【課題】 高駆動能力横型MOSトランジスタにおいて、単位面積当りのゲート幅を増大させつつ、素子特性の安定した高駆動能力横型MOSトランジスタの構造を提供する。

【解決手段】 MOSトランジスタにおいて、ゲート長方向に対し水平に配置するトレンチもしくはフィンの構造をゲート幅方向に階段状に形成することで半導体基板表面とトレンチ底部もしくはフィン頭頂部の段差が緩和されるため、単位面積当りの駆動能力を上げるために深いトレンチもしくは高いフィンを有している場合においても、イオン注入法を用いてチャネル領域、ソース拡散層およびドレイン拡散層の不純物濃度を均一に形成することができる構造と成る。これにより、チャネルが形成される面による特性の変動が現れない安定した特性が得られ、単位面積当りのオン抵抗が低減された高駆動能力横型MOSトランジスタを提供することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲートトランジスタにおいて、溝に埋め込まれたゲート電極とゲート絶縁膜との界面にボイドが形成されることを防止する。

【解決手段】半導体基板1に埋め込まれた素子分離絶縁膜3により絶縁分離された活性領域4と、ゲート絶縁膜5を介して活性領域4上を跨ぐように形成されたゲート電極6と、ゲート電極6を挟んだ両側の活性領域4に形成されたソース領域7a及びドレイン領域7bとを有し、活性領域4に溝8が設けられて、この溝8の内側にゲート絶縁膜5を介してゲート電極6の一部が埋め込まれてなるトレンチゲートトランジスタ51を備える半導体装置であって、溝8が少なくとも上端開口部よりも下部側において幅広となる形状を有し、溝8に埋め込まれたゲート電極6内に外殻層13aで覆われた中空部(ボイド)14が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型トランジスタとPNゲートで構成されるプレーナ型トランジスタとが共存する半導体装置において、溝型トランジスタの溝ゲートの空乏化現象によるオン電流の低下を抑制し、溝型トランジスタと異なる導電型のP又はNゲートで構成されるプレーナ型トランジスタの閾値電圧のバラツキ増加を防止する。

【解決手段】溝型トランジスタのゲート電極であるポリシリコン膜中に高濃度不純物拡散材料9が埋設された構造を有する。

(もっと読む)

半導体装置

【課題】高耐圧および高ESD耐性を有し、かつ、他のMOSトランジスタとの混載が容易なMOSトランジスタを備える、半導体装置を提供する。

【解決手段】半導体基板2の表層部には、ソース領域13とディープN型ウェル8、N型ウェル10およびコンタクト領域11からなるドレイン領域とが間隔を空けて形成されている。半導体基板2上には、ゲート絶縁膜14が形成されている。そして、ドレイン領域とゲート絶縁膜14との間には、ドレイン−ゲート分離部9が介在されている。このドレイン−ゲート分離部9によって、ドレイン領域とゲート絶縁膜14とは、それらの間に間隔を空けた非接触な状態に分離されている。

(もっと読む)

溝ゲート型SiC半導体装置の製造方法

【課題】均一な厚さのゲート絶縁膜を形成することを可能とした溝ゲート型SiC半導体装置の製造方法を提供する。

【解決手段】六方晶SiCの(0001)Si面に形成した溝ゲート型SiC半導体装置の製造方法において、

ゲート絶縁膜を形成する処理が、下記の工程:

SiC基板のSi面に形成した溝の底面および側面と溝以外のSiC基板面全体に、堆積法によりSiO2層を形成する工程、および

1000〜1300℃での熱酸化により上記SiO2層を成長させて上記ゲート絶縁膜を完成させる工程

を含むことを特徴とする溝ゲート型SiC半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】本発明の課題は、オン抵抗や寄生容量を極力、増大させることなく、オフ状態の耐圧を向上させることができる半導体装置を提供することである。

【解決手段】本発明の半導体装置10は、P型半導体基板101と、その所定領域に形成されたN+型ドレイン埋め込み層103と、そのN+型ドレイン埋め込み層103を含むP型半導体基板101上に形成されたN−型エピタキシャル層102と、それを貫通して、N+型ドレイン埋め込み層103に接続するN+型ドレイン取り出し領域104と、N−型エピタキシャル層102表面に形成されたP型ベース領域105と、P型ベース領域105表面に形成されたN+型ソース領域106とを備え、N−型エピタキシャル層102表面に、N−型エピタキシャル層102と同導電型でN−型エピタキシャル層102よりも低い不純物濃度のN−−型低濃度領域11をP型ベース領域105の外周に沿って設けた。

(もっと読む)

リセスチャネル構造を有するトランジスタを含む半導体装置およびその製造方法

【課題】特性異常の発生を低減することのできるリセスチャネル構造を有するトランジスタを含む半導体装置およびその製造方法を提供すること。

【解決手段】半導体シリコン基板の活性領域に設けられた第一のリセスおよび素子分離領域に設けられた第二のリセスと、リセスチャネル構造を有するトランジスタと、を少なくとも有する半導体装置であって、

前記トランジスタは、前記第一のリセス内部に設けられたゲート電極を有し、

前記ゲート電極は、前記第一のリセス内部に設けられた部分に加えて、前記第二のリセス内部に設けられた部分を有し、

前記第一のリセス内部に設けられた前記ゲート電極の部分と、前記第二のリセス内部に設けられた前記ゲート電極の部分とは、前記活性領域と前記素子分離領域との境界面と同一の面で互いに電気的に接続されていることを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAM等に代表される半導体装置の高集積化、微細構造化が進展した場合であっても、量産に適した構造を有するリセスチャネル構造を有するトランジスタを含む半導体装置を提供すること。

【解決手段】半導体シリコン基板の一部の表面上に成長された選択エピタキシャルシリコン層と、ゲート電極に対応したソース領域およびドレイン領域とを少なくとも有し、

前記ソース領域は、前記半導体シリコン基板の表面領域に形成され、

前記ドレイン領域は、前記選択エピタキシャルシリコン層および前記選択エピタキシャルシリコン層下部の前記半導体シリコン基板の表面領域に形成されているリセスチャネル構造を有する非対称型トランジスタ、を含むことを特徴とする半導体装置。

(もっと読む)

3次元チャネル電界効果トランジスタを備えた集積回路およびその製造方法

【課題】3次元チャネル構造トランジスタのゲート長とゲート幅を拡大した集積回路及びその製造方法を提供する。

【解決手段】ソース領域161、ドレイン領域162、上記ソース領域と上記ドレイン領域との間に配置されるチャネル領域163、ゲート電極165と、上記チャネル領域と上記ゲート電極との間に配置されるゲート誘電体164と、上記ゲート電極と上記ソース領域の少なくとも一部との間に配置される第1絶縁体構造物146と、上記ゲート電極と上記ドレイン領域の少なくとも一部との間に配置される第2絶縁体構造物147とを含み、上記ゲート電極の下端部は、上記ソース領域および上記ドレイン領域の少なくとも1つの領域の下端部よりも下に形成され、上記第1絶縁体構造物および上記第2絶縁体構造物の少なくとも1つは、上記ゲート誘電体よりも大きな層厚を有し、上記第1絶縁体構造物および上記第2絶縁体構造物は、互いに非対称である。

(もっと読む)

半導体装置

【課題】ピンチオフを抑制する構造を有することによって、駆動電流を向上させることのできる電界効果トランジスタを含む半導体装置を提供する。

【解決手段】ソース領域111およびドレイン領域121と、このソース領域111とドレイン領域121との間に存在し、相対する主面を有するチャネル領域101と、主面にゲート絶縁膜103、104を介して設けられた一対のゲート電極107、108を具備し、相対する主面の間隔が、ドレイン領域121側においてソース領域111側よりも大きい電界効果トランジスタを含むことを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置を形成するためのウエハ表面の窒化にあたり、基板主面と平行な面方向及び交差する面方向の何れについても同様な窒化速度を得る。

【解決手段】窒化処理チャンバー22内に複数のウエハ23を収容する。プラズマ生成チャンバー21内に反応ガスとしてN2ガス及びNH3ガスを供給し、プラズマ24を発生させる。また、窒化処理チャンバー22の下流で真空ポンプによる排気を行い、プラズマ生成チャンバー21内で生成された窒素ラジカルを窒化処理チャンバー22内に流す。これにより、ウエハ表面に窒素ラジカルを供給して窒化処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート構造の半導体装置及びその製造方法の提供を課題とする。

【解決手段】本発明の半導体装置は、半導体基板に形成された溝と、前記溝の内部側にゲート絶縁膜を介して形成されたゲート電極と、前記ゲート電極の近傍の半導体基板に前記ゲート絶縁膜を介して配置されたソース及びドレインとを具備してなるトレンチゲートトランジスタを備えるとともに、前記ゲート絶縁膜において、前記ソース及びまたはドレインに接する領域のゲート絶縁膜の厚さが、前記溝の内部側に形成されているゲート絶縁膜の厚さよりも厚くされたことを特徴とする。

(もっと読む)

立体的形状の活性領域を含むCMOS構造体

【課題】 複数の結晶方位の半導体基板領域を有するCMOSデバイス及びCMOS構造体、及び、そのようなCMOSデバイス及びCMOS構造体を製造するための方法を提供する。

【解決手段】 CMOS構造体は、半導体基板内の第1の活性領域を用いて配置された第1のデバイスを含み、第1の活性領域は、平坦であり、第1の結晶方位を有する。CMOS構造体はまた、半導体基板内の第2の活性領域を用いて配置された第2のデバイスを含み、第2の活性領域は、立体的形状であり、第1の結晶方位の存在しない第2の結晶方位をもつ。第1の結晶方位及び第2の結晶方位は、典型的には電荷キャリア移動度に関して、第1のデバイス及び第2のデバイスの性能を最適化することを可能にする。立体的形状の第2の活性領域はまた、単一厚さを有する。CMOS構造体は、立体的形状の第2の活性領域を形成するための結晶学的特異性エッチャントを用いて製造することができる。

(もっと読む)

21 - 40 / 83

[ Back to top ]