Fターム[5F140BB05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901) | 段差部に形成されたもの (818) | VSHC(垂直表面水平電流) (437)

Fターム[5F140BB05]に分類される特許

421 - 437 / 437

半導体装置

【課題】 低抵抗でゲート空乏化が起こらず、高温において安定であるとともに、仕事関数が制御されたゲート電極を有するCMISデバイスを提供する。

【解決手段】 素子分離領域を有する半導体基板と、前記半導体基板に形成されたソース/ドレイン領域、前記半導体基板上に形成されたゲート絶縁膜、および前記ゲート絶縁膜上に形成されたゲート電極を有するp型MISトランジスタと、前記半導体基板に形成されたソース/ドレイン領域、前記半導体基板上に形成されたゲート絶縁膜、および前記ゲート絶縁膜上に形成されたゲート電極を有するn型MISトランジスタとを具備するCMISデバイスである。前記p型MISトランジスタにおける前記ゲート電極は、少なくとも前記ゲート絶縁膜との界面に第1の金属を有し、前記n型MISトランジスタにおける前記ゲート電極は、少なくとも前記ゲート絶縁膜との界面に、前記第1の金属のホウ化物を有することを特徴とする。

(もっと読む)

強化された遮蔽構造を備えた金属酸化膜半導体デバイス

【課題】強化された遮蔽構造を備えた金属酸化膜半導体(MOS)デバイスを提供すること。

【解決手段】MOSデバイスは、基板上に形成された半導体層を含み、その基板は水平面とその水平面に垂直な方向の法線とを画定する。第1のソース/ドレイン領域および第2のソース/ドレイン領域が、半導体層内で、その上面近傍に形成され、第1のソース/ドレイン領域と第2のソース/ドレイン領域は互いに離隔されている。ゲートが、半導体層の上面近傍に形成され、少なくとも部分的には第1のソース/ドレイン領域と第2のソース/ドレイン領域との間に配置される。第1の誘電領域が、MOSデバイス内に形成され、半導体層の上面から下方に第1の距離まで半導体層の中へ延在するトレンチの境界を画定し、第1のソース/ドレイン領域と第2のソース/ドレイン領域との間に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】フェルミ・レベル・ピンニング効果を抑制するとともに、トランジスタの微細化を図ること。

【解決手段】シリコン基板または支持基板11上に形成された島状のチャネル層13と、チャネル層13上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、チャネル層13の一方向に対向する両側面上に形成されたシリコン窒化膜14と、シリコン窒化膜14の側面上に形成された金属材料からなるソース電極及びドレイン電極19とを具備する。

(もっと読む)

トランジスタ、メモリセルアレイ、および、トランジスタ製造方法

【課題】トレンチ型DRAMメモリセルの形成において、垂直型トラジスタとトレンチ型キャパシタの接続を容易化し、高集積化する。

【解決手段】第1および第2ソース/ドレイン領域と、該第1および第2ソース/ドレイン領域を接続する、半導体基板の中に配置されたチャネル領域と、ゲート電極とを含み、該ゲート電極は、上記第1および第2ソース/ドレイン領域間に流れる電流を制御するために、上記チャネル領域に沿って配置され、該チャネル領域から電気的に絶縁されている。また、上記チャネル領域では、該チャネルがリッジ状の形をなしたフィン領域を有している。この「リッジ状」とは、1つの上面と、第1ソース/ドレイン領域と第2ソース/ドレイン領域とを接続する線に対して(断面図では)垂直である2つの側面とからなる。この上面は、半導体基板の表面よりも下に配置されており、ゲート電極は、この上面および2つの側面に沿って設けられる。

(もっと読む)

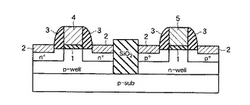

トレンチ構造を利用した横型半導体装置及びその製造方法

【課題】 長さ方向がゲート長方向と平行なトレンチに形成されたゲート電極を有し、単位平面積当たり大きなゲート幅を有する高駆動能力横型のMOSトランジスタの駆動能力を、平面的な素子面積を増加させずに向上させる半導体装置を提供する。

【解決手段】 半導体基板の表面に長さ方向がゲート長方向と平行なトレンチが形成された第1トレンチ領域013と、前記第1トレンチ領域の凹部底面と同一平面に設けられた第2トレンチ領域014および第3トレンチ領域015と、前記第1,第2,第3トレンチ領域の少なくとも1領域に形成された第2導電型のウェル領域と、前記第1トレンチ領域に設けられたゲート絶縁膜とゲート電極と、前記第1,第2と3トレンチ領域に前記ウェル領域より浅く設けられた第1導電型のソース領域とドレイン領域を有する半導体装置。

(もっと読む)

メモリデバイス、トランジスタ、メモリセル並びにそれらの製造方法

メモリデバイスはメモリセルのアレイと周辺デバイスを含んでいる。少なくとも一部の個別メモリセルはSiCを含む炭酸化部分を含んでいる。少なくとも一部の周辺デバイスは炭酸化部分を含まない。トランジスタは第1ソース/ドレーン、第2ソース/ドレーン、第1ソース/ドレーンと第2ソース/ドレーンとの間にSiCを含む半導体基板の炭酸化部分を含んだチャンネル、及びチャンネルの両側と作動式に関係するゲートを含んでいる。 (もっと読む)

横型トレンチMOSFET

【課題】 素子面積を増大させずにオン抵抗の低減を実現した横型MOSFETにおいて、更にオン抵抗を低減させる。

【解決手段】 トレンチ構造を用いることで素子面積を増大させずにチャネル幅を増大させ、オン抵抗の低減を実現した横型トレンチMOSFETにおいて、トレンチ008の両端付近に多方向イオン注入によりソース層004およびドレイン層005を形成する。このような構成にすることでソース層004およびドレイン層005がトレンチ008より深く形成され、電子がチャネル全域に広がって流れ、実効的なL長も短くなることで更なるオン抵抗の低減化が実現できる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】 高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタおよびその製造方法を実現する。

【解決手段】 シリコン基板1上に、フィン形状に突出して形成されたフィン部3、5を設ける。フィン部3、5のチャネル領域部を被覆したゲート誘電体8を設ける。ゲート誘電体8によってチャネル領域部から絶縁されて、上記チャネル領域部上に形成されたゲート電極4を設ける。シリコン基板1上を覆う絶縁体層2を設ける。フィン部3、5は、シリコン基板1から絶縁体層2を貫通して絶縁体層2の表面より突出して延びるように形成されている。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

半導体装置

【課題】 信頼性の高い半導体装置を実現するために、寄生容量の大きな半導体装置を提供する。

【解決手段】 半導体装置は、第1方向に延在する突出部1bを有する半導体基板1を含む。ゲート絶縁膜11は、突出部の上面上および第1方向に沿う側面上に配設される。ゲート電極12は、第1部分12aと第2部分12bを有する。第1部分は、突出部と交差し、且つ突出部の上面上のゲート絶縁膜上に配設される。第2部分は、突出部の側面上のゲート絶縁膜上に配設され、且つ第1方向における長さが第1部分の第1方向における長さより長い。1対のソース/ドレイン領域13が、ゲート電極の第1部分の下方の領域を挟むように突出部の表面に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 閾値の変動を回避するとともに、電気的ストレスに対する信頼性の高いMOSトランジスタを備えた半導体装置を提供する。

【解決手段】 素子領域を画定する素子分離領域(12)が設けられた半導体基板(11)と、前記半導体基板の前記素子領域に離間して設けられたソース/ドレイン領域(25)と、前記半導体基板の前記素子領域上に設けられたゲート絶縁膜(13,14)と、前記ゲート絶縁膜上に設けられ、半導体を含むゲート電極(15)とを具備する半導体装置である。前記ゲート絶縁膜は、金属および酸素を含有する第1の絶縁膜(13)と、この第1の絶縁膜上に形成され、シリコンおよび酸素を含有する第2の絶縁膜(14)とを含み、前記第2の絶縁膜は、前記ゲート電極との界面における前記金属の含有量が6.6atomic.%未満であることを特徴とする。

(もっと読む)

分離トレンチ

分離トレンチ(209)をウェハ(201)に形成するプロセスである。このプロセスでは、(例えば、異方性堆積法により)第1誘電体材料(307)をトレンチ(209)の中に堆積させ、次に第2誘電体材料(309)を(例えば、異方性堆積法により)トレンチ(209)内の第1誘電体材料(307)を覆うように堆積させる。第3材料(501)をトレンチ(209)内に、かつ第2誘電体材料(309)の上に堆積させる。第2材料(309)及び第3材料(501)の内の一方の材料は、他方の材料をエッチングしないように選択的にエッチングすることができる。一の例では、第1材料(307)は第2材料(309)よりも小さい誘電率を有する。  (もっと読む)

(もっと読む)

トライゲートトランジスタ及びその製造方法

本発明の実施形態は、均一なシリコンボディ高さをもたらすSOIトランジスタの製造方法を提供する。一実施形態では、犠牲酸化物層が半導体基板上に配置される。酸化物層はトレンチを形成するようにエッチングされ、トレンチは半導体材料で充填される。そして、半導体材料は酸化物層の残部を用いて平坦化され、その後、酸化物層の残部は除去される。こうして露出された半導体フィンは仕様の許容範囲内で均一な高さを有する。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

等方性エッチングプロセスを使ったショットキーバリアMOSFET製造方法

【課題】電流の流れを調整するトランジスタデバイスの組立て方法において、更なる駆動電流を可能にし、デバイスの動作を最適化するプロセスを提供すること。

【解決手段】本発明の一実施形態における方法は、チャンネル領域に対するショットキーバリア接合位置のより良い制御を与えるために、メタルソースドレイン接触の形成に先行して等方性エッチングプロセスを利用する。このショットキーバリア10接合の配置の制御性からの改善により、更なる駆動電流を可能にし、デバイスの動作を最適化する。

(もっと読む)

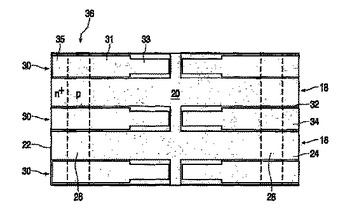

トレンチMOS構造

半導体装置はセル(18)に隣接するトレンチ(42)を有する。このセルは、ソース・コンタクト領域及びドレイン・コンタクト領域(26、28)と、それとは逆の導電型の中央本体(40)とを含む。この装置は双方向性であり、比較的低いオン抵抗で電流をいずれの方向にも制御する。好ましい実施形態は、ソース・ドリフト領域及びドレイン・ドリフト領域(30、32)と共に働いてRESURF効果を生み出す電位プレート(60)を含む。  (もっと読む)

(もっと読む)

絶縁トレンチゲート電極を有する横型電界効果トランジスタ

縦方向、横方向に交互に配置されたソース領域(22)、ソースボディ領域(26)、ドリフト領域(20)、ドレインボディ領域(28)、およびドレイン領域(24)をそれぞれ有するセル(18)を、減表面電界を達成するための構造とともに有する、電界効果トランジスタである。実施形態における構造は、ソースまたはドレイン領域(22、24)近傍にゲート領域(31)を定義する縦方向に離間された絶縁ゲートトレンチ(35)と、ドリフト領域(20)近傍に縦方向に延在する電位プレート領域(33)と、を含むことができる。代替的に、別個の電位プレート領域(33)または縦方向に延在する半絶縁フィールドプレート(50)をドリフト領域(20)近傍に設けてもよい。このトランジスタは、双方向切り替えに適している。  (もっと読む)

(もっと読む)

421 - 437 / 437

[ Back to top ]