Fターム[5F140BD02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 3層以上 (272)

Fターム[5F140BD02]に分類される特許

1 - 20 / 272

半導体装置の製造方法

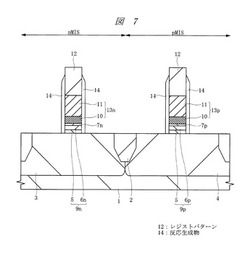

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

半導体装置及びその製造方法、電源装置、高周波増幅器

【課題】放置時間が長くても、化合物半導体積層構造の表面のダングリングボンドがフッ素で終端された状態が維持されるようにし、閾値電圧の変動を抑制して、信頼性を向上させる。

【解決手段】半導体装置は、化合物半導体積層構造6と、化合物半導体積層構造6の表面を覆うフッ素含有バリア膜9と、化合物半導体積層構造6の上方にフッ素含有バリア膜9を挟んで設けられたゲート電極8とを備える。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能する第1導電型の半導体層11、チャネル領域を囲み、半導体層11に活性領域を定義する素子分離絶縁膜21、活性領域の一方に設けられた第2導電型の第1主電極領域62、活性領域の他方に設けられた第2導電型の第2主電極領域63、活性領域の表面のゲート絶縁膜22、多結晶シリコン層を含んで、ゲート絶縁膜22の上に設けられたゲート電極54を備える。多結晶シリコン層は、第1主電極領域62,第2主電極領域63に接する部分は第2導電型の第1多結晶シリコン領域54-2、チャネル領域と素子分離絶縁膜21との境界領域の上部は第1導電型の第2多結晶シリコン領域54-1である。

(もっと読む)

半導体装置の製造方法及び基板処理システム

【課題】EOTの低減及びリーク電流の低減を両立できる半導体装置の製造方法を提供すること。

【解決手段】被処理体上に第1の高誘電率絶縁膜を成膜する第1の成膜工程と、前記第1の高誘電率絶縁膜を、650℃以上で60秒未満の間熱処理する結晶化熱処理工程と、前記第1の高誘電率絶縁膜上に、前記第1の高誘電率絶縁膜の金属元素のイオン半径よりも小さいイオン半径を有する金属元素を有し、前記第1の高誘電率絶縁膜よりも比誘電率が大きい、第2の高誘電率絶縁膜を成膜する第2の成膜工程と、を含む、半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域のゲート絶縁膜への酸化剤の進入を防止しつつ、第2の領域の複数の第1の配線間に設けられた酸化アルミニウム膜を選択的に除去する。

【解決手段】第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線を覆うように形成した第1の絶縁膜をマスクとして、第1の領域に第1のイオン注入を施す。その後、第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線間を埋設するように形成した、酸化アルミニウムを主体とする第2の絶縁膜をマスクとして、第1の領域に第2のイオン注入を施す。第2の絶縁膜を、第1の絶縁膜に対して選択的に除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETのしきい値を調整する目的でLaなどが導入された高誘電率膜を含むゲート絶縁膜と、その上部のメタルゲート電極との積層構造を有する半導体装置において、ゲート電極のゲート幅を縮小した際、基板側からメタルゲート電極の底面に酸化種が拡散してnチャネル型MISFETの仕事関数が上昇することを防ぐ。

【解決手段】HfおよびLn含有絶縁膜5bとその上部のメタルゲート電極である金属膜9との間に、酸化種の拡散を防ぐためにAl含有膜8cを形成する。

(もっと読む)

半導体装置の製造方法

【課題】界面準位密度およびフラットバンド電圧がともに良好な界面特性を有する半導体装置の製造方法を提供すること。

【解決手段】まず、炭化珪素基板1の表面を洗浄する(ステップS1)。つぎに、原料ガスをECRプラズマ化し、原料ガスに含まれる原子を炭化珪素基板1に照射することで、炭化珪素基板1の表面にシリコン窒化膜2を成長させる(ステップS2)。つぎに、ECRプラズマ化学気相成長法により、シリコン窒化膜2の表面にシリコン酸化膜3を堆積する(ステップS3)。つぎに、窒素雰囲気中で、シリコン窒化膜2およびシリコン酸化膜3が形成された炭化珪素基板1のアニール処理を行う(ステップS4)。

(もっと読む)

高誘電性ナノシート積層体、高誘電性ナノシート積層体、高誘電体素子、および高誘電体薄膜素子の製造方法

【課題】コンデンサなどに好適な、非常に薄くしても高い誘電率と良好な絶縁特性を同時に実現する高誘電体薄膜を提供する。

【解決手段】上記課題は、ペロブスカイト構造を有する酸化物ナノシートなどの高誘電体により構成される薄膜により達成される。

(もっと読む)

半導体装置及びその製造方法

【課題】下地絶縁膜の膜厚精度の向上とトランジスタ特性の変動抑制との両立が図られたMISトランジスタを備えた半導体装置、及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100における活性領域103a上に形成されたゲート絶縁膜108aと、ゲート絶縁膜108a上に形成されたゲート電極111aとを有するMISトランジスタ170を備えている。ゲート絶縁膜108aは、活性領域103a上に形成された板状の下層ゲート絶縁膜210aと、下層ゲート絶縁膜210a上に形成された断面形状が凹状の上層ゲート絶縁膜211aとを有する。下層ゲート絶縁膜210aは、活性領域103a上に形成された下地絶縁膜104aと、第1の高誘電率絶縁膜106aとで構成され、上層ゲート絶縁膜211aは、第1の高誘電率絶縁膜106a上に形成された第2の高誘電率絶縁膜107aで構成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【目的】水素終端よりも強い界面終端構造を有する半導体装置を提供することを目的の1つとする。

【構成】実施形態の半導体装置は、絶縁膜とSi半導体部とを備えている。絶縁膜は、酸化物と窒化物と酸窒化物とのいずれかを用いて形成される。Si半導体部202は、前記絶縁膜下に配置され、硫黄(S)とセレン(Se)とテルル(Te)とのうち少なくとも1種の元素が前記絶縁膜との界面に存在する、シリコン(Si)を用いて形成される。

(もっと読む)

半導体装置及び半導体基板の重水素処理装置

【課題】シリコンカーバイド領域を含む半導体基板上に形成された金属-絶縁膜-半導体構造を有する半導体装置(電界効果型トランジスタ(MISあるいはMOSFET))に対して、高温に加熱された熱触媒体表面での重水素を含んだガスの熱触媒作用によって生成された活性化した重水素を用いることにより、600°C以下の低温においてゲート絶縁膜/シリコンカーバイド半導体界面近傍に存在するダングリングボンドの重水素終端を図り、界面準位密度の低い良好なゲート酸化膜/半導体界面が形成された半導体装置、およびそれを形成する重水素処理装置およびその作製方法を提供する。

【解決手段】半導体基板とゲート絶縁膜、層間絶縁膜、配線層、保護絶縁膜等の半導体装置に形成される膜又は層の界面近傍での重水素元素濃度が1x1019cm-3以上であることを特徴とする金属−絶縁膜−半導体(MIS)構造を有する半導体装置。

(もっと読む)

半導体装置、試験装置、および製造方法

【課題】閾値変動を抑えつつ、ゲートリーク電流を低減させた窒化物半導体HEMT。

【解決手段】窒化物系半導体で形成された半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、を備え、ゲート絶縁膜は、酸窒化膜で形成された第1絶縁膜と、タンタル、ハフニウム、ハフニウムアルミニウム、ランタン、およびイットリウムの少なくとも1つを含む第2絶縁膜と、を有する半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】用途によって異なるしきい値電圧を有するトランジスタを有する半導体装置、及び工程数の増加を抑えた当該半導体装置を製造する方法を提供する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1のゲート絶縁膜110aと、第1のゲート絶縁膜110a上に形成された第1のゲート電極109aと、第1のゲート絶縁膜110aの側面上及び第1のゲート電極109aの側面上に形成された第1のサイドウォール絶縁膜140aとを有する第1導電型の第1のMISFET150を備えている。第1のサイドウォール絶縁膜140aの少なくとも一部には、第1のゲート絶縁膜110aに正または負の固定電荷を誘起するための元素が含まれている。

(もっと読む)

半導体装置

【課題】トンネルトランジスタにおいて、その寄生容量を低減したゲート電極を提供する。

【解決手段】ゲート絶縁膜201を介して形成されたゲート電極202を挟むように形成された、第1導電型のソース領域121及び前記第1導電型とは逆導電型の第2導電型のドレイン領域122と、基板101内において前記ソース領域121と前記ドレイン領域122との間に形成された、第2導電型のチャネル領域123とを備える。そして、前記ゲート絶縁膜201は、前記ソース領域上に位置し、チャネル幅方向に平行な第1のエッジE1と、前記チャネル領域上又は前記ソース領域上に位置し、チャネル幅方向に平行な第2のエッジE2とを有し、第1の膜厚を有する第1の絶縁膜部分を有する。さらに、前記ゲート絶縁膜201は、前記第1の絶縁膜部分に対して前記ドレイン領域側に位置し、前記第1の膜厚よりも厚い第2の膜厚を有する第2の絶縁膜部分を有する。

(もっと読む)

コンデンサ及びその製造方法

【課題】金属−絶縁体−金属コンデンサや、内部接続構造の金属間誘電体として使用して、その素子や構造の平均故障寿命を改善できる誘電体構造を提供すること。

【解決手段】酸化膜層、誘電体材料層及び誘電体材料層の上に第2酸化膜層を有する、炭化ケイ素用のコンデンサ及び内部接続構造が提供される。酸化膜層の厚みは、酸化膜層と誘電体材料層の約0.5から約33パーセントであってよい。誘電体構造として酸窒化ケイ素層を有する炭化ケイ素用のコンデンサおよび内部接続構造もまた提供される。こうしたコンデンサ及び構造を作製する方法もまた提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタと、抵抗素子とを同一基板に有する半導体装置において、安定したHK/MGトランジスタの動作特性を得ることのできる技術を提供する。

【解決手段】TiN膜と多結晶Si膜との積層膜からなるHK/MGトランジスタのゲート電極を形成し、同様に、TiN膜と多結晶Si膜との積層膜からなる抵抗素子を形成した後、抵抗素子の側壁に形成したオフセットサイドウォール9aおよびサイドウォール9の一部を除去し、そのオフセットサイドウォール9aおよびサイドウォール9が除去された箇所から薬液を浸入させることによりTiN膜を除去して空洞18を形成し、多結晶Si膜のみからなる抵抗部RESを形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置の製造方法

【課題】複雑な工程を回避すると共に、高い有効仕事関数値を得ることにより、高歩留まり及び高性能の半導体装置を実現できるようにする。

【解決手段】ダミー電極22をマスクとして、n型活性領域13にp型の不純物イオンを導入することにより、n型活性領域13におけるダミー電極22の両側方にp型のソースドレイン領域25pを形成し、形成されたソースドレイン領域25pに熱処理を施す。熱処理を施した後に、n型活性領域13の上に、ダミー電極22を覆うように層間絶縁膜26を形成し、形成された層間絶縁膜26からダミー電極22を露出し、露出したダミー電極22を除去する。続いて、層間絶縁膜26におけるダミー電極22が除去された凹部26aに、第2の金属電極27を選択的に形成する。

(もっと読む)

1 - 20 / 272

[ Back to top ]