Fターム[5F140BF25]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 3層目より上層の材料 (915) | 金属 (751)

Fターム[5F140BF25]の下位に属するFターム

合金 (20)

高融点金属 (221)

金属シリサイド (290)

金属化合物(窒化物、酸化物) (127)

Fターム[5F140BF25]に分類される特許

81 - 93 / 93

低抵抗窒化チタン膜

導電性の窒化チタン層を形成するための原子層堆積(ALD)の利用は、種々の電子デバイスにおける使用のために信頼性の高い構造を生み出す。この構造は、TDEATなどのチタン含有前駆体化学物質を用いた基板表面上への原子層堆積によって窒化チタンを堆積させ、その後アンモニアと一酸化炭素の混合物、もしくは一酸化炭素のみを使い、そしてこの工程を連続的に堆積されたTiN構造を形成するために繰り返すことによって形成される。そのようなTiN層は、アルミニウムもしくは銅などの別の導電体の下にある拡散障壁として、もしくはアルミニウム導電体の最上位にあるエレクトロマイグレーション防止層(electro-migration preventing layer)として用いられる可能性がある。ALD堆積TiN層は低い抵抗性、平坦な地勢、大きな堆積速度、および優れた段差被覆性と導電性を有する。 (もっと読む)

CMOS半導体装置

【課題】CMOS半導体装置において、pチャネルMOSトランジスタの動作速度を向上させる。

【解決手段】第1の素子領域と第2の素子領域とを含む基板と、前記第1の素子領域上に第1のゲート絶縁膜を介して形成されたn型半導体材料よりなる第1のゲート電極と、前記第1の素子領域中、前記第1のゲート電極の両側に形成された一対のn型拡散領域と、前記第2の素子領域上に第2のゲート絶縁膜を介して形成されたp型半導体材料よりなる第2のゲート電極と、前記第2の素子領域中、前記第2のゲート電極の両側に形成された一対のp型拡散領域とよりなるCMOS半導体装置において、前記第2の素子領域は、前記第1の素子領域のホール移動度よりも大きなホール移動度を有する。

(もっと読む)

ゲート絶縁膜の製造方法および半導体装置の製造方法

【課題】 薄膜化しても、半導体装置に優れた電気的特性を付与できる良質なゲート絶縁膜を製造する。

【解決手段】 プラズマ処理装置の処理室内で、被処理体表面のシリコンに酸素含有プラズマを作用させてシリコン酸化膜を形成する酸化処理工程を含むゲート絶縁膜の製造方法であって、前記酸化処理工程における処理温度は600℃超1000℃以下であり、前記酸素含有プラズマは、少なくとも希ガスと酸素ガスとを含む酸素含有処理ガスを前記処理室内に導入するとともに、アンテナを介して該処理室内に高周波またはマイクロ波を導入することによって形成される前記酸素含有処理ガスのプラズマであることを特徴とする、ゲート絶縁膜の製造方法。

(もっと読む)

半導体素子を形成する方法

【課題】 ゲートリーク電流の低減。

【解決手段】 本発明による半導体の製造方法は、基板を設ける工程と、誘電体層を基板の上に形成する工程と、アモルファス半導体層を誘電体層の上に成長させる工程と、アモルファス半導体層に不純物をドープする工程と、そして高温処理工程をアモルファス層に施して前記アモルファス半導体から結晶化層を形成する工程とを備える。

(もっと読む)

分離層を備える半導体デバイス

本発明は、半導体本体(1)内に配置された半導体デバイスであって、それぞれ第1導電型である少なくとも1つのソース領域(4)および少なくとも1つのドレイン領域(5)と、ソース領域(4)とドレイン領域(5)との間に配置された第2の導電型の少なくとも1つの本体領域(8)と、分離層(9)によって半導体本体(1)に対して分離されている少なくとも1つのゲート電極(10)とを備えるデバイスに関する。前記分離層(9)は、それぞれナノ粒子の分離したコアおよび分極可能な陰イオンまたは分極可能な陽イオンのシースからなる分極可能な粒子を含む。分離層(9)は、高い誘電率εを示す。  (もっと読む)

(もっと読む)

CMOSプロセス用金属ゲート・トランジスタ及びその製造方法

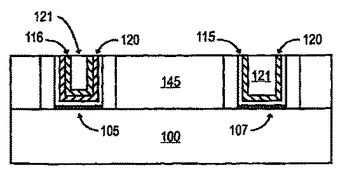

半導体装置(100)を形成する方法は、第一領域(104)を備える半導体基板と、第一領域上にゲート誘電体(108)を形成するステップと、ゲート誘電体上に導電性金属酸化物(110)を形成するステップと、導電性金属酸化物上に耐酸化バリア層(111)を形成するステップと、耐酸化バリア層上にキャッピング層(116)を形成するステップとを含む。一実施形態において、導電性金属酸化物はIrO2,MoO2及びRuO2であり、耐酸化バリア層はTiNを含む。  (もっと読む)

(もっと読む)

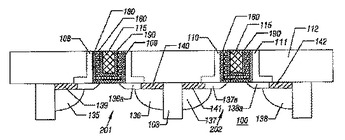

高誘電率ゲート誘電体および金属ゲート電極をもつ半導体デバイスの作成方法

半導体デバイスを作成する方法に関する。該方法は、基板上で二酸化ケイ素層に窒素を加えて窒化二酸化ケイ素層を形成することを含む。窒化二酸化ケイ素層の上に犠牲層を形成したのち、犠牲層が除去されて溝が生成される。窒化二酸化ケイ素層の上で溝の中に高誘電率ゲート誘電体層が形成され、該高誘電率ゲート誘電体層の上に金属ゲート電極が形成される。

(もっと読む)

(もっと読む)

半導体装置の製造方法および半導体製造装置

シリコンウエハ101上のゲート酸化膜102上に、ポリシリコンを成膜して、ポリシリコン電極層103(第一電極層)を形成する。このポリシリコン電極層103上に、タングステン層105(第二電極層)を形成する。なお、タングステン層105を形成する前に、予め導電性のバリア層104をポリシリコン電極層103の上に形成しておく。その後、窒化シリコン層106をエッチングマスクとして、エッチング処理を行う。そして、剥き出しとなったポリシリコン層103の露出面に、プラズマ酸化処理により、酸化絶縁膜107を形成する。これにより、タングステン層105を酸化させずに、ポリシリコン電極層103に対して選択的な酸化処理を行うことができる。  (もっと読む)

(もっと読む)

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

多層ゲートスタック

プラズマによりパターン形成された窒化層を形成するために窒化層をエッチングすることからなる半導体構造体を製造する方法。窒化層は半導体の基板上にあり、フォトレジスト層は窒化層上にあり、プラズマは、少なくとも圧力10ミリトルでCF4及びCHF3のガス混合物から形成される。 (もっと読む)

PMOSを具備する半導体素子の形成方法

【課題】本発明はPMOSを具備する半導体素子を形成する方法を提供する。

【解決手段】前記方法によると、半導体基板の全面上にポリシリコン膜を形成する。前記ポリシリコン膜にP型不純物をドーピングする。熱処理工程を進行する。そして、前記P型不純物がドーピングされたポリシリコン膜の上部を第1厚さだけ除去する。これによって、漏洩電流を防止して、素子の速度を向上させることができるPMOSを具備する半導体素子を形成することができる。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

81 - 93 / 93

[ Back to top ]