Fターム[5F140BF25]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 3層目より上層の材料 (915) | 金属 (751)

Fターム[5F140BF25]の下位に属するFターム

合金 (20)

高融点金属 (221)

金属シリサイド (290)

金属化合物(窒化物、酸化物) (127)

Fターム[5F140BF25]に分類される特許

41 - 60 / 93

半導体装置とその製造方法

【課題】

メタルゲートを有するpチャネルMISトランジスタとメタルゲートを有するnチャネルMISトランジスタとを、少ない工程数で形成する。

【解決手段】

半導体装置は、シリコン層を有する半導体基板と、半導体基板に画定されたn型活性領域とp型活性領域と、n型活性領域の上方に形成され、酸化シリコンより高い誘電率を有し、表面にAlを含有する第1高誘電率ゲート絶縁膜と、p型活性領域の上方に形成され、酸化シリコンより高い誘電率を有する第2高誘電率ゲート絶縁膜と、第1高誘電率ゲート絶縁膜および第2高誘電率ゲート絶縁膜の各々の上に形成され、nチャネルトランジスタに適した仕事関数を有する金属又は金属化合物を含む材料で形成された、第1ゲート電極および第2ゲート電極と、を有することを特徴とする。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】化合物半導体と絶縁性材料との界面に形成される界面準位が低減した半導体装置を提供する。

【解決手段】閃亜鉛鉱型の結晶構造を有する3−5族化合物半導体と、3−5族化合物半導体の(111)面、(111)面と等価な面、または、(111)面もしくは(111)面と等価な面から傾いたオフ角を有する面に接する絶縁性材料と、絶縁性材料に接し、金属伝導性材料を含むMIS型電極とを備える半導体装置を提供する。

(もっと読む)

チャネル領域の下方にデルタドープ層を有するIII−V族デバイス

III−V族材料のデバイスは、チャネル領域の下方にデルタドープ領域を有する。これは、ゲートとチャネル領域との間の距離を短縮することによって、デバイスの性能を向上させ得る。  (もっと読む)

(もっと読む)

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域7b及びp+型半導体領域8bを形成してから、半導体基板1上にNi1−xPtx合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域7b及びp+型半導体領域8bとを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層41aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で第1の熱処理を行ない、かつ、金属シリサイド層41a上に合金膜の未反応部分が残存するように、第1の熱処理を行なう。これにより、y>xとなる。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層41aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層41bを形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲートラストプロセスで作製するトランジスタにおいて、活性領域と素子分離領域の高さばらつきのためゲートのポリシリコンを抜くことができないことにより、ゲートの抵抗にばらつきが生じるのを防ぐことを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、第1のゲート部30及び第2のゲート部31の上面が共に露出するように、酸化膜16、PMD19、及び第1のゲート部30又は第2のゲート部31の一部を研磨除去する工程、露出された部分より、ポリシリコン12を抜く工程、第1のゲート部30及び第2のゲート部31を覆うメタルを形成する工程を備える。また、第1のゲート部30及び第2のゲート部31の上面が共に露出するようにメタルを研磨除去し、第1のゲート部30と第2のゲート部31で厚みの異なるメタルを残す工程を備えて構成される。

(もっと読む)

アルミニウムがドープされた金属炭窒化物ゲート電極の作製方法

半導体デバイス用のアルミニウムがドープされた金属(タンタル又はチタン)炭窒化物ゲート電極の作製方法が記載されている。当該方法は、上に誘電層を有する基板を供する工程、及びプラズマが存在しない状態で前記誘電層上に前記ゲート電極を作製する工程を有する。前記ゲート電極は、金属炭窒化物を堆積する堆積工程、及び前記金属炭窒化物上にアルミニウム前駆体の原子層を吸着させる吸着工程によって作製される。前記堆積工程及び前記吸着工程は、前記アルミニウムがドープされた金属炭窒化物ゲート電極が所望の厚さを有するまで、必要な回数だけ繰り返されて良い。  (もっと読む)

(もっと読む)

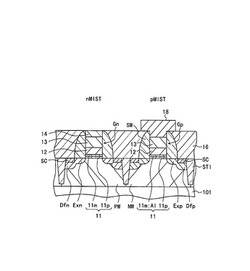

半導体装置及び半導体装置の製造方法

【課題】従来に比べて製造工程を簡易化することができ、かつ、絶縁膜が損傷を受けることを防止することができ、製造コストの低減と信頼性の向上を図ることのできる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】P型半導体層11上に、下側から順に第1ゲート絶縁膜2a、第2ゲート絶縁膜2b、第1金属膜3a、第2金属膜3b、第3金属膜3cが形成されたNチャンネルMISトランジスタ21、及び、N型半導体層10上に、下側から順に第1ゲート絶縁膜2a、第2ゲート絶縁膜2b、第1金属膜3a、第3金属膜3cが形成されたPチャンネルMISトランジスタ20を具備した半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造を有するRC型トランジスタにおいて、しきい値電圧の低下を防止でき、さらに、しきい値電圧の制御や調整が容易にできる。

【解決手段】電界効果トランジスタを備えた半導体装置であって、電界効果トランジスタは、半導体基板1に形成された素子分離領域3によって仕切られた拡散層領域と、

その拡散層領域と交差するように設けられ、少なくとも一部が半導体基板1に形成されたゲート溝内に埋め込まれたゲート電極5と、拡散層領域内において、一方の側面がゲート電極5のうちゲート溝内に埋め込まれた部分と対向し、他方の側面が素子分離領域3の側面と接触するように形成されたSOI構造のチャネル層4とを有し、ソース・ドレイン領域として機能する不純物拡散層5がチャネル層4よりも上部に配置され、不純物拡散層5とチャネル層4とが離間して形成されている。

(もっと読む)

二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みゲート電極脇の材料層の後退が防止され、これによって特性の向上が図られた半導体装置を提供する。

【解決手段】半導体基板1上に溝パターンaを有して設けられた絶縁膜100と、溝パターンaの内壁を覆う状態で設けられたゲート絶縁膜9と、ゲート絶縁膜9を介して溝パターンa内を埋め込むと共に、絶縁膜100上における溝パターンaの両側に溝パターンaよりも幅広に張り出して形成されたゲート電極101とを備えたことを特徴とする半導体装置104。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電率ゲート絶縁膜とメタルゲート電極を用いたメタルゲートCMOSの製造方法を簡略化する。

【解決手段】 高誘電率ゲート絶縁膜6上にシリコン膜7を形成し、PMOS領域のシリコン膜7のみを選択的に窒化してSiN膜9に置換する。そしてNMOS領域上のシリコン膜7及びPMOS領域上のSiN膜9上にキャップ膜としてのLa(O)膜11及びメタル電極のW膜12を形成した後、加熱処理して、La(O)膜11のLa元素をNMOS領域の高誘電率ゲート絶縁膜に拡散させる。この際、PMOS領域においては、SiN膜9によりLa元素の拡散をブロックする。これにより、NMOSFETとPMOSFETの作りわけを容易に行える。また、窒化されやすい高誘電率ゲート絶縁膜6であれば、シリコン膜7を省略して、窒化処理によりPMOS領域の高誘電率ゲート絶縁膜6だけを選択的に窒化してもよい。

(もっと読む)

GaN系電界効果トランジスタ

【課題】簡易な製造工程によって形成可能なノーマリーオフ型のGaN系FETを提供すること。

【解決手段】本発明においては、ソース電極S直下およびドレイン電極D直下にそれぞれn−AlGaN層16を形成し、さらにn−AlGaN層16の間に位置するチャネル層であるp−GaN層14上に形成される絶縁膜17の上にゲート電極Gを形成することによって、ソース電極Sおよびドレイン電極Dとn−AlGaN層16との接触抵抗を低下させたノーマリーオフ型のGaN系のFET1を実現することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲートラストプロセスで形成されたゲート構造において、ソース・ドレイン領域に接続するコンタクトとゲート電極とのショートを防ぐ。

【解決手段】半導体装置100は、ゲートラストプロセスで形成された第1のゲート210を含む。第1のゲート210は、絶縁膜中に形成された第1の凹部内の底面に形成されたゲート絶縁膜、当該第1の凹部内のゲート絶縁膜上に形成されたゲート電極、および当該第1の凹部内のゲート電極上に形成された保護絶縁膜140を含む。また、半導体装置100は、第1のゲート210の両側方のN型不純物拡散領域116aに接続され、第1の凹部よりも径が大きい第2の凹部内に埋め込まれたコンタクト134を含む。

(もっと読む)

選択的酸化プロセスの酸化物成長速度の改良方法

【課題】 半導体デバイスにおいてシリコン含有物質を選択的に酸化する方法の提供。

【解決手段】 一態様において、急速熱処理装置を用いて、水素を多く含む雰囲気中で高圧においてインサイチュで水蒸気を生成させることによって基板を選択的に酸化する。基板における金属やバリヤ層のような他の物質は酸化されない。

(もっと読む)

半導体デバイスを形成する方法

【課題】 ボイドフリーかつシームフリーの金属ゲート導体層が比較的薄い高kゲート誘電体層の上に位置決めされている少なくとも1つの高アスペクト比ゲート構造を有する相補型金属酸化膜半導体(CMOS)デバイスを形成する方法を提供する。

【解決手段】 これらの方法実施形態は、高アスペクト比ゲート・スタック開口部を下から上に金属ゲート導体層で充填するために電気メッキ・プロセスを使用するゲート交換戦略を取り入れている。電気メッキ・プロセス用の電子の発生源は、基板の裏面を直接通過する電流である。これは、シード層の必要性を排除し、ボイドまたはシームなしで金属ゲート導体層が形成されることを保証するものである。さらに、実施形態次第で、電気メッキ・プロセスは、所与の領域への電子流を増強するために(すなわち、メッキを増強するために)照明を受けて実行され、所与の領域への電子流を防止するために(すなわち、メッキを防止するために)暗闇で実行される。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETにおいて、従来のFinFETの構造に比してさらにチャネルに応力を印加することができる半導体装置を提供すること。

【解決手段】Si基板1と、フィン11、フィン11の延在方向に平行な面上にゲート絶縁膜13を介して形成される所定の幅のゲート電極14、およびフィン11の延在方向に平行な面上のゲート電極14の両側に形成されるソース/ドレイン領域を含むFinFET10n,10pと、を備え、ゲート電極14上に形成され、応力印加層31,32の形成温度と室温での線膨張係数の差が、フィン11の形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層31,32と、応力印加層31,32上に形成され、フィン11よりもヤング率の大きい導電性材料からなるプラグ層33,34と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高速高周波動作に適した信頼性の高い半導体装置を得ること。

【解決手段】シリコン基板11の表面層に拡張ドレイン領域12とウェル領域13を形成し、拡張ドレイン領域12上に絶縁層20を形成する。その絶縁層20の側壁に犠牲スペーサー領域を形成し、犠牲スペーサー領域をマスクとしてウェル領域13の表面層に自己整合的に窒素を注入し熱処理を行う。犠牲スペーサー領域を除去した後に熱酸化を行ってゲート酸化膜21,22を形成する。窒素が注入された部分のシリコンの酸化速度は、窒素が注入されていない部分のシリコンの酸化速度と同じか、それよりも低下する。窒素は、絶縁層20の側壁の犠牲スペーサー領域の下には注入されないので、厚い絶縁層20に接続する部分のゲート酸化膜21の厚さが、それ以外の部分のゲート酸化膜22の厚さと同じか、それよりも厚くなる。

(もっと読む)

多重チャネルを有する半導体素子及びその製造方法

【課題】本発明は、ゲート電極を形成する以前に半導体基板の活性領域の形態を変化させて多数のチャネルを有するようにする。

【解決手段】本発明は、素子分離膜が形成された半導体基板、半導体基板の活性領域内に形成された多数のトレンチ及びそれぞれのトレンチ領域内の対向する側壁を連結し、表面がチャネル領域として用いられるチャネル活性領域を含む多重チャネルを有する半導体素子からなる。

(もっと読む)

半導体装置の製造方法及びトランジスタの製造方法

【課題】溝の埋め込み性を改善することと、溝の埋め込み高さを確保することを両立させることができる半導体装置の製造方法を実現する。

【解決手段】半導体装置の製造方法として、半導体基板1上の層間膜2に幅の異なる溝3,4を形成する工程と、溝3,4が形成された層間膜2上にバリアメタル層5を形成する工程と、バリアメタル層5を覆いかつ溝3,4の形成部位に開口部を有するレジストマスク7を形成する工程と、レジストマスク7を用いてバリアメタル層5をエッチングすることによりオーバーハング部6を除去する工程と、レジストマスク7を除去した後、半導体基板1上で溝3,4に配線材料を埋め込む工程と、半導体基板1上で配線材料とバリアメタル層5の余剰部を研磨により除去する工程とによって溝配線を形成する。

(もっと読む)

41 - 60 / 93

[ Back to top ]