Fターム[5F140BF26]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 3層目より上層の材料 (915) | 金属 (751) | 合金 (20)

Fターム[5F140BF26]に分類される特許

1 - 20 / 20

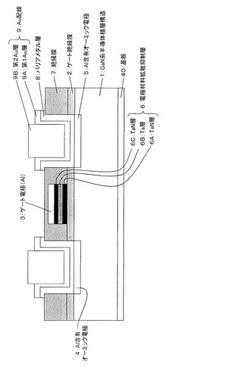

半導体装置及びその製造方法、電源装置

【課題】電極材料が拡散するのを抑制し、特性の向上を実現する。

【解決手段】半導体装置を、ゲート電極3とゲート絶縁膜2との間、Al含有オーミック電極4、5とAu配線9との間、及び、ゲート電極3の下方及びAl含有オーミック電極4、5の上方、のいずれかに設けられ、第1TaN層6A、Ta層6B、第2TaN層6Cを順に積層した構造を有する電極材料拡散抑制層6を備えるものとする。

(もっと読む)

金属ゲート電極を有する半導体素子の製造方法

【課題】 収率が低下することなくCMOS集積回路の特性を最適可能な半導体素子の製造方法を提供する。

【解決手段】 半導体基板1の上の第1領域A内及び第2領域B内に各々形成された第1グルーブ15a及び第2グルーブ15bを有する層間絶縁膜15を形成する。次に、半導体基板1上に積層金属膜22を形成し、積層金属膜22上に非感光性を有する平坦化膜23を第1グルーブ15a及び第2グルーブ15bを充填するように形成する。第1領域A内の平坦化膜23を乾式エッチングによって選択的に除去し、第1領域A内の積層金属膜22を露出させ、第2領域B内の積層金属膜22を覆う平坦化膜パターン23pを形成する。これにより、第1領域A内の最上部金属膜を容易に除去することができるので、収率が低下することなく異なる仕事関数を有する第1金属ゲート電極及び第2金属ゲート電極を形成できる。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

ダイヤモンド半導体素子及びその製造方法

【課題】耐電圧、耐熱性、耐放射線性、及び高速性が優れ、かつ、チャネル領域を短くでき、素子の応答性が高いダイヤモンド半導体素子を高精度で製造できる半導体素子の製造方法を提供する。

【解決手段】第1のダイヤモンド半導体領域1の表面上に、絶縁膜2と多層金属電極層3と犠牲層4とを積層し、犠牲層4上に、局所的にレジスト5をパターン形成する。多層金属電極層3の最上層は、Pt又はPt合金により形成する。そして、レジスト5をマスクとして第1の犠牲層、多層金属電極層及び絶縁膜をエッチングした後、レジスト5を除去して、第1のダイヤモンド半導体領域1上に絶縁膜2と金属電極層3と第1の犠牲層4との積層体をパターン形成する。その後、第1のダイヤモンド半導体領域1上に、不純物の高濃度ドープ層7を形成する。その後、犠牲層4をエッチング除去し、高濃度ドープ層7上に金属電極8を形成する。

(もっと読む)

GaN系MOS型電界効果トランジスタ

【課題】ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るGaN系MOSFETを提供する。

【解決手段】p−GaNからなる電子走行層13とゲート電極18との間にゲート絶縁膜15が形成されたGaN系MOSFET10である。ゲート電極18は、AlGaInP混晶からなる。ゲート電極18は、p型AlGaInP混晶からなる第1のゲート層19と、この上に形成されたp型GaAsからなる第2のゲート層20と、この上に形成された金属層(AuGe/Au電極)21とを有する。AlGaInP混晶の混晶比を変化させることにより、しきい値電圧を制御することが出来る。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】容易に製造できる半導体装置を提供する。

【解決手段】半導体装置は、PMOSトランジスタのゲート電極1pの仕事関数値が、High-kゲート絶縁膜16(16a)、及び、High-kゲート絶縁膜16・酸化シリコン膜15界面へのAlの拡散により調整されており、NMOSトランジスタのゲート電極1nの仕事関数値が、High-kゲート絶縁膜16・金属ゲート膜19間に挿入された、数原子層程度のAl層18により調整されている構成を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート誘電体層108と、ゲート誘電体層108上に形成された酸素を含む合金層110と、酸素を含む合金層110上に形成されたRe層112と、ゲート誘電体層108と酸素を含む合金層110との間に位置するRe酸化物層502を含むp 型電界効果トランジスタを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】特性の劣化を効果的に抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaNを含む半導体層1と、電極とを備えている。電極は、電極本体6と、半導体層1から見て電極本体6よりも離れた位置に形成され、かつAlを含む接続用電極8と、電極本体6と接続用電極8との間に形成されたW、TiW、WN、TiN、Ta、およびTaNよりなる群から選ばれる少なくとも1種を含むバリア層7とを含んでいる。バリア層7の表面粗さRMSが3.0nm以下である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みゲート電極脇の材料層の後退が防止され、これによって特性の向上が図られた半導体装置を提供する。

【解決手段】半導体基板1上に溝パターンaを有して設けられた絶縁膜100と、溝パターンaの内壁を覆う状態で設けられたゲート絶縁膜9と、ゲート絶縁膜9を介して溝パターンa内を埋め込むと共に、絶縁膜100上における溝パターンaの両側に溝パターンaよりも幅広に張り出して形成されたゲート電極101とを備えたことを特徴とする半導体装置104。

(もっと読む)

半導体装置およびその製造方法

【課題】金属シリサイド膜の膜厚が薄くなってきたり、拡散層幅が小さくなってくると、拡散層上の金属シリサイドが凝集反応を起こしやすくなる、という問題があった。

【解決手段】半導体装置100は、半導体基板2と、半導体基板内に設けられた拡散層4と、半導体基板上に設けられたゲート絶縁膜12と、ゲート絶縁膜上に設けられたゲート電極14と、拡散層上に選択的に設けられたNiシリサイド層8と、を含み、Niシリサイド層8上にはCoを主成分とするメタルキャップ膜18が選択的に設けられている。

(もっと読む)

洗浄方法及び半導体装置の製造方法

【課題】シリサイドゲート上の微小突起物を除去することにより、ゲート電極とコンタクトプラグとのショート不良の発生を抑制した洗浄方法及び半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、ゲート電極3上及びソース/ドレイン領域の拡散層6,7上にTi膜を形成する工程と、このTi膜に熱処理を施すことにより、ゲート電極上及びソース/ドレイン領域の拡散層上にTiシリサイド膜9a〜9cを形成するシリサイド化工程と、このシリサイド化工程でシリサイド化されずに残留するTi膜を除去する洗浄工程であって、アンモニア水及び過酸化水素水を含む洗浄液に超音波を加えながら洗浄する工程と、Tiシリサイド膜上に層間絶縁膜10を形成する工程と、この層間絶縁膜をエッチングすることにより第1の接続孔及び第2の接続孔を形成する工程と、を具備する。

(もっと読む)

半導体装置

【課題】 製造プロセスの複雑化や製造コストの増大を招くことなく、デュアルメタルゲートCMOS構造を実現する。

【解決手段】 基板上にn,pチャネルの各MISトランジスタ100,200を有する半導体装置であって、nMISトランジスタ100は、基板10上に形成されたp型半導体領域101と、p型半導体領域101上にゲート絶縁膜104を介して形成され、1モノレイヤー以上3nm以下の下層ゲート電極111と、下層ゲート電極111上に形成され、平均的な電気陰性度が下層ゲート電極111のそれより0.1以上小さい上層ゲート電極112とを含み、pMISトランジスタ200は、基板10上に形成されたn型半導体領域201と、n型半導体領域201上にゲート絶縁膜204を介して形成され、上層ゲート電極111と同一金属材料からなるゲート電極210とを含んで形成されている。

(もっと読む)

電界効果トランジスタ、集積回路、及びメモリ

【課題】 微細化が進んだ場合でもゲート・リーク電流の低減を図ることのできる電界効果トランジスタを実現すること。

【解決手段】 半導体基板1と、磁化方向が第1方向に固定された第1強磁性体電極3と、磁化方向が前記第1方向と実質的に同じ方向に固定された第2強磁性体電極4と、第1強磁性体電極3と第2強磁性体電極4との間のチャネル2と、チャネル2上にゲート絶縁層5を介して設けられ磁化方向が前記第1方向と実質的に反対の方向に固定された強磁性体層6を備えたゲート電極とを具備することを特徴とする電界効果トランジスタ。ゲート電極の強磁性体層6の磁化方向が、第1強磁性体電極3及び第2強磁性体電極4のそれぞれの磁化方向と実質的に反対の方向に固定されているので、トンネル磁気抵抗効果によりゲート・リーク電流を低減化することができる。

(もっと読む)

ゲート酸化物の漏れを抑えたリプレースメントゲートトランジスタ

ゲート酸化物層(12)とメタルゲート電極(60)との間に保護層(70)を形成することによって、リプレースメントゲートトランジスタに対してリーク電流を抑えた実効的なゲート酸化膜厚を得ることができ、これにより、応力を減らすことができる。実施形態においては、金属ゲート電極(60)から保護層を通じてゲート酸化物層(12)に向かうに従って濃度が低下する金属炭化物を含む非晶質炭素層(70)の保護層が形成される。方法の実施形態では、リムーバブルゲートを除去するステップ、ゲート酸化物層へ非晶質炭素層を蒸着するステップ、メタルゲート電極(60)を形成するステップ、を含み、さらにその後、メタルゲートからの金属を非晶質炭素層に拡散して金属炭化物を形成するように、高温に加熱するステップ、を含む。さらに、一実施形態では、高誘電定数を有するゲート酸化物層(82)と、金属ゲート電極(100)と基板(10)との界面において高濃度のシリコンと、を含むメタルゲートトランジスタが含まれる。  (もっと読む)

(もっと読む)

低抵抗窒化チタン膜

導電性の窒化チタン層を形成するための原子層堆積(ALD)の利用は、種々の電子デバイスにおける使用のために信頼性の高い構造を生み出す。この構造は、TDEATなどのチタン含有前駆体化学物質を用いた基板表面上への原子層堆積によって窒化チタンを堆積させ、その後アンモニアと一酸化炭素の混合物、もしくは一酸化炭素のみを使い、そしてこの工程を連続的に堆積されたTiN構造を形成するために繰り返すことによって形成される。そのようなTiN層は、アルミニウムもしくは銅などの別の導電体の下にある拡散障壁として、もしくはアルミニウム導電体の最上位にあるエレクトロマイグレーション防止層(electro-migration preventing layer)として用いられる可能性がある。ALD堆積TiN層は低い抵抗性、平坦な地勢、大きな堆積速度、および優れた段差被覆性と導電性を有する。 (もっと読む)

半導体装置の製造方法および半導体製造装置

シリコンウエハ101上のゲート酸化膜102上に、ポリシリコンを成膜して、ポリシリコン電極層103(第一電極層)を形成する。このポリシリコン電極層103上に、タングステン層105(第二電極層)を形成する。なお、タングステン層105を形成する前に、予め導電性のバリア層104をポリシリコン電極層103の上に形成しておく。その後、窒化シリコン層106をエッチングマスクとして、エッチング処理を行う。そして、剥き出しとなったポリシリコン層103の露出面に、プラズマ酸化処理により、酸化絶縁膜107を形成する。これにより、タングステン層105を酸化させずに、ポリシリコン電極層103に対して選択的な酸化処理を行うことができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板4上にシリコン酸化膜5を介して例えばゲ−ト電極2を形成するに際し、このゲ−ト電極2を複数の多結晶シリコン層6の積層体で構成する。ゲ−ト電極2の部分は、非晶質層の堆積工程とこの非晶質材料の結晶化(再結晶化)工程とを有する薄膜の製造方法により形成する。この際、1回に成膜する非晶質層の厚さが不良事象に応じて決定される臨界応力値によって規定される厚み以下であるように非晶質層の堆積を複数回に分割して行い、各非晶質層の堆積工程後毎に非晶質材料を結晶化させ、かつ非晶質層堆積工程と非晶質材料結晶化工程を繰り返すことにより必要な膜厚の多結晶層6の積層構造体を得る。

【解決手段】 半導体装置の電気特性の劣化と、層間剥離,層内での割れ等の不良を防止し、かつ多結晶材料層の積層により、所望厚さで小粒径の多結晶層が得られる。

(もっと読む)

半導体装置

【課題】 低抵抗でゲート空乏化が起こらず、高温において安定であるとともに、仕事関数が制御されたゲート電極を有するCMISデバイスを提供する。

【解決手段】 素子分離領域を有する半導体基板と、前記半導体基板に形成されたソース/ドレイン領域、前記半導体基板上に形成されたゲート絶縁膜、および前記ゲート絶縁膜上に形成されたゲート電極を有するp型MISトランジスタと、前記半導体基板に形成されたソース/ドレイン領域、前記半導体基板上に形成されたゲート絶縁膜、および前記ゲート絶縁膜上に形成されたゲート電極を有するn型MISトランジスタとを具備するCMISデバイスである。前記p型MISトランジスタにおける前記ゲート電極は、少なくとも前記ゲート絶縁膜との界面に第1の金属を有し、前記n型MISトランジスタにおける前記ゲート電極は、少なくとも前記ゲート絶縁膜との界面に、前記第1の金属のホウ化物を有することを特徴とする。

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

1 - 20 / 20

[ Back to top ]