Fターム[5F140BF40]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 複数種類を用い単純多層でないもの (119)

Fターム[5F140BF40]に分類される特許

81 - 100 / 119

半導体装置及びその製造方法

【課題】半導体プロセスの微細化に伴い、信頼性の高い微細なゲート電極の形成がより困難なものとなっている。

【解決手段】ゲート電極105の上面に加え、ゲート電極105の側面に対しても金属シリサイド110を形成することで、ゲート電極105を所望の太さの幅に拡大しなくても、信頼性の高いゲート電極105を形成することができる。

(もっと読む)

MOSトランジスタの製造方法およびMOSトランジスタ

【課題】内部回路の保護と高応答性の両立を図ることのできるMOSトランジスタの製造方法およびMOSトランジスタを提供する。

【解決手段】MOSトランジスタ20のソース28、ドレイン30、ゲート26の各端子を形成した後、MOSトランジスタ20の表面にレジストを塗布するとともに、その後各端子上のレジストを除去しレジストが除去された各端子上にシリサイド膜32を形成する。この際、レジストを除去する範囲をソース28の全域と、ゲート26の表面をソース28側とドレイン30側とに2分割したソース28側とに設定し、これら表面にシリサイド膜32を形成するようにすれば金属配線の溶融が防止され外部サージによる内部回路22の保護をなすことができる。一方ソース28およびゲート26にはシリサイド膜32が形成され寄生抵抗の低下により低電圧動作、および高速化、小型化を達成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート絶縁膜に接するゲート電極の空乏化を抑制しながら、ゲート電極の仕事関数の調整を効率的に行うことが可能な半導体装置およびその製造方法を提供する。

【解決手段】 p型シリコン基板1、埋め込み酸化膜2、及び単結晶シリコン層3から構成されるSOI基板4において、単結晶シリコン層3にソース領域10およびドレイン領域11を備える。また、ソース領域10とドレイン領域11との間の単結晶シリコン層3の表面側はチャネル層3aとして機能する。単結晶シリコン層3(チャネル層3a)の上にはゲート絶縁膜5が形成される。ゲート絶縁膜5上には、窒化チタン(TiN)からなる金属粒子6a,6b、及びポリシリコン膜7から構成されるポリシリコンゲート電極8が設けられる。ここで、TiNからなる金属粒子は、ゲート絶縁膜5に接する部分6aと接しない部分6bからなる。

(もっと読む)

半導体装置およびその製造方法

【課題】高いオン電流とソース/ドレイン拡散層における低い接合リーク電流を両立可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に設けられたゲート絶縁膜3を含む。ゲート電極21は、ゲート絶縁膜上に設けられ、第1部分を含む。第1部分は、半導体と金属との化合物からなり、下面がゲート絶縁膜に達する。第1部分内の金属元素の密度は第1値である。1対のソース/ドレイン拡散層11は、ゲート電極の下方のチャネル領域を挟む。導電膜23は、半導体基板のソース/ドレイン拡散層の部分に設けられ、半導体と金属との化合物からなる。導電膜内の金属元素の密度は、第1値より小さい第2値である。

(もっと読む)

改良された短チャネル効果制御を備えたMOSトランジスタおよびその製造方法

【課題】短チャネル効果を抑制するMOSトランジスタおよびその製造方法を提供する。

【解決手段】集積回路がゲート酸化膜に接触する底部を持つゲートを有する少なくとも1つのMOSトランジスタを備える。 該底部は、ソース領域とドレイン領域との間のゲートの長さに沿った不均一な仕事関数を有し、該ゲートの端部における該仕事関数の値は、該ゲートの中央部における該仕事関数の値より大きい。ゲートは、該中央部において第1の材料を含み、残りの部分において第2の材料を含む。このような構成は、例えばシリサイド化によって得られる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】半導体装置10において、ソース領域40およびドレイン領域50が形成された半導体基板30と、ソース領域40およびドレイン領域50に挟まれた半導体基板30上に形成された絶縁膜60と、絶縁膜60上に形成されたゲート電極80と、絶縁膜60とゲート電極80との界面に形成された金属含有粒子70と、金属含有粒子70のうち界面の縁部60aからはみ出していた金属含有粒子が変化した絶縁粒子72と、を備える。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】半導体装置のソース/ドレインとゲートおよびウェル間の漏洩電流を低減する。

【解決手段】電界効果トランジスタ2は、ゲート電極4のいずれかの側面に配置された第1および第2ソース/ドレイン領域28を備え、第1および第2ソース/ドレイン領域28に挟まれた、ゲート電極4の直下に位置する半導体基板24内に、チャネル領域26が形成される。基板上にゲート酸化物層22が形成される。ゲート電極4は、ゲート酸化物層22の表面と接触しており、少なくとも第1導電体層10および第2導電体層12を備える。第1導電体層10および第2導電体層12は互いに異なる仕事関数を有する材料から構成されている。ゲート電極4の第1導電体層10はゲート酸化物層22表面の第1部分40と接触しており、第2導電体層12はゲート酸化物層の表面の第2部分42と接触している。第1導電体層10は、さらに第2導電体層12と導電接続されている。

(もっと読む)

半導体素子の製造方法

本発明は、リソグラフィ工程を経たフォトレジストの特性を変化させてダミー構造物を形成し、これをゲート電極形成工程に適用した半導体素子の製造方法に関することで、半導体基板上の最上部にバッファー層を形成するステップと、前記バッファー層の上部に無機物フォトレジストを塗布してリソグラフィを通じてフォトレジストパターンを形成するステップと、前記形成されたパターンに特定ガスを使用して熱処理を行うステップと、前記熱処理された構造物の上部に均一な厚さの絶縁膜を蒸着した後に前記パターンが露出されるように前記蒸着された膜をエッチングするステップと、前記工程を経た構造物に絶縁膜を蒸着し、前記パターンが露出されるように前記絶縁膜をエッチングするステップと、前記露出されたパターンを除去するステップと、前記パターンが除去された位置にゲート酸化膜を形成するステップと、前記形成されたゲート酸化膜の上部にゲート電極を形成するステップと、を含む。本発明によれば、ナノ素子を製作するための構造を形成する時、リソグラフィを通じて形成された膜の特性が後続熱処理を通じて改善されるので、多様な素子を製作するための構造を容易に形成することができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート空乏化の抑制および低抵抗化を図った半導体装置およびその製造方法を提供する。

【解決手段】本実施形態に係る半導体装置は、基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成されたゲート電極4とを有し、ゲート電極4は、ゲート絶縁膜3上に形成されたシリサイド層5と、シリサイド層5上に形成された金属層6とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】フルシリサイド化されたゲート電極における容量を低減できるようにする。

【解決手段】半導体装置は、半導体基板11に形成された素子分離領域12と、該素子分離領域12に囲まれた半導体基板11からなる活性領域11aと、該活性領域11aの上に形成されたゲート絶縁膜13と、活性領域11a及び隣接する素子分離領域12の上に跨って形成されたゲート電極15とを備えている。ゲート電極15は、活性領域11a上にゲート絶縁膜13を介して設けられ、厚さ方向における全領域がシリサイド領域からなる第1の部分と、素子分離領域12の上に設けられ、シリコン領域及び該シリコン領域を覆うように形成されたシリサイド領域からなる第2の部分とを有している。

(もっと読む)

ゲート酸化物の漏れを抑えたリプレースメントゲートトランジスタ

ゲート酸化物層(12)とメタルゲート電極(60)との間に保護層(70)を形成することによって、リプレースメントゲートトランジスタに対してリーク電流を抑えた実効的なゲート酸化膜厚を得ることができ、これにより、応力を減らすことができる。実施形態においては、金属ゲート電極(60)から保護層を通じてゲート酸化物層(12)に向かうに従って濃度が低下する金属炭化物を含む非晶質炭素層(70)の保護層が形成される。方法の実施形態では、リムーバブルゲートを除去するステップ、ゲート酸化物層へ非晶質炭素層を蒸着するステップ、メタルゲート電極(60)を形成するステップ、を含み、さらにその後、メタルゲートからの金属を非晶質炭素層に拡散して金属炭化物を形成するように、高温に加熱するステップ、を含む。さらに、一実施形態では、高誘電定数を有するゲート酸化物層(82)と、金属ゲート電極(100)と基板(10)との界面において高濃度のシリコンと、を含むメタルゲートトランジスタが含まれる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】FUSI電極とポリシリコン抵抗体とを備え、簡便に製造できる半導体装置およびその製造方法を提供する。

【解決手段】FUSIゲート電極とポリシリコン抵抗体とを有するMISトランジスタを備えた半導体装置において、ポリシリコン抵抗体のうちコンタクト形成領域に設けられた部分は、ゲート電極または不純物拡散領域と同時にシリサイド化される。

(もっと読む)

ゲートに近接したコンタクト・ホールを有する半導体トランジスタ

【課題】 デバイス密度を増加させるために、S/Dコンタクト・ホールが、トランジスタ構造体のゲートに近接して形成されるが、ゲートから電気的に絶縁された、トランジスタ構造体(及びその製造方法)を提供すること。

【解決手段】 構造体、及びその製造方法である。この構造体は、(a)第1のS/D領域と第2のS/D領域との間に配置されたチャネル領域と、(b)チャネル領域上のゲート誘電体領域と、(c)ゲート誘電体領域上にあり、かつ、ゲート誘電体領域によりチャネル領域から電気的に絶縁されたゲート領域と、(d)ゲート領域上の保護アンブレラ領域であって、保護アンブレラ領域は第1の誘電体材料を含み、ゲート領域が完全に保護アンブレラ領域の影の中にある、保護アンブレラ領域と、(e)(i)第2のS/D領域の真上にあり、これと電気的に接続され、かつ、(ii)保護アンブレラ領域のエッジと位置合わせされた充填されたコンタクト・ホールであって、コンタクト・ホールは、第1の誘電体材料とは異なる第2の誘電体材料を含む層間誘電体(ILD)層によってゲート領域から物理的に分離された充填されたコンタクト・ホールと、を含む。

(もっと読む)

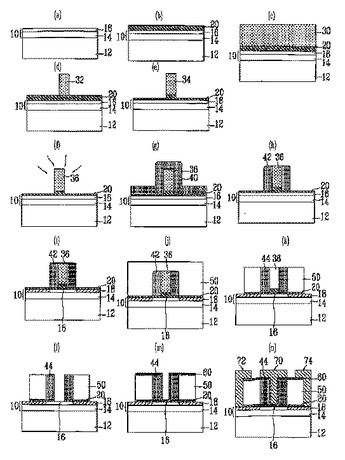

半導体構造の形成方法

【課題】ゲート金属層の側壁エッジ酸化を防止する半導体構造の形成方法を提供する。

【解決手段】ゲート電極は、ドープトシリコン層108と該ドープトシリコン層上の金属層112とからなり、側壁エッジに沿って第2シリコン層120を形成する過程であって、前記第2シリコン層120は、前記側壁エッジのドープトシリコン層領域108及び金属層領域112に沿っており且つ前記ドープトシリコン層より不純物が低濃度にドープされ、前記側壁エッジの金属層領域に沿ってシリサイドを形成するために、前記第2シリコン層のシリコンを前記金属層領域の金属と反応させる過程と、前記反応後、前記ドープトシリコン層のドープトシリコンに対して、前記第2シリコン層のシリコンを選択的に除去する過程と、前記第2のシリコン層のシリコンを選択的に除去した後、側壁エッジのドープトシリコン層領域を酸化する過程を具備することを特徴とする。

(もっと読む)

半導体装置

【課題】本発明は、Fin型MISFETにおいて、Finの下部で生じるパンチスルーを抑制できるようにする。

【解決手段】たとえば、Si基板11の表面上には、素子領域となるFin12が設けられている。Fin12には、ソース・ドレイン拡散層23a,23bが形成されている。ソース・ドレイン拡散層23a,23bの相互間には、チャネル部が形成されている。このチャネル部に対応する、上記Fin12の一部を覆うようにしてゲート電極部21が設けられている。ゲート電極部21は、第1の仕事関数を有する第1のゲート電極21a上に、第1のゲート電極21aとは異なる、第2の仕事関数を有する第2のゲート電極21bを積層してなる構成とされている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極上にシリサイド膜を有し、従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極62及びLDD層63が形成された半導体基板60の上にシリサイドブロックとなるSiN膜64を形成し、このSiN膜64にゲート電極62に通じる開口部を設ける。この開口部を介してゲート電極66の表面をシリサイド化してシリサイド膜66を形成する。次に、SiO2からなる層間絶縁膜67を形成し、フォトリソグラフィ法により層間絶縁膜67の上面からLDD層63に到達するコンタクトホール67hを形成する。そして、このコンタクトホール67hを介してLDD層63に不純物を高濃度に導入して、ソース/ドレイン層63aを形成する。

(もっと読む)

ゲート電極構造及び製造方法

電界効果トランジスタ内に用いられるゲート電極構造及び集積回路及び製造方法が開示される。その方法と構造によって仕事関数と閾値調整が改善される。 (もっと読む)

半導体装置およびその製造方法

【課題】ショートチャネル効果を抑制すると共にキャリア移動度の向上を図る半導体装置およびその製造方法を提供する。

【解決手段】シリコン基板11中、ソース領域11Sおよびドレイン領域11Dに対応してトレンチ11−1A,11−1Bを形成し、トレンチ11−1A,11−1Bをp型の不純物元素を含むSiGe混晶層19A,19Bによりエピタキシャルに充填する際に、トレンチ11−1A,11−1Bの側壁面19bをファセットにより画成し、さらに第2側壁絶縁膜18A,18Bの底面の下側のシリコン基板11の表面にSiGe混晶層19A,19Bからなる延出部19Aa,19Baを形成し、ソースエクステンション領域11EAおよびドレインエクステンション領域11EBに接触させる。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させずにメタルゲート構造の加工性を向上した、45nm世代以降のSoCデバイスの製造に対応可能な半導体装置の製造方法を得る。

【解決手段】半導体基板上に高誘電率材料層を形成する高誘電率材料層形成工程と、前記高誘電率材料層上に該高誘電率材料層に接するとともに金属、金属合金、またはこれらの化合物からなる金属層を形成した後、該金属層をパターニングすることにより金属ゲート電極層を形成するゲート電極層形成工程と、前記金属ゲート電極層の側壁部にウエットエッチング耐性を有する保護膜を形成する保護膜形成工程と、前記高誘電率材料層をウエットエッチングによりパターニングして高誘電率ゲート絶縁膜を形成する高誘電率ゲート絶縁膜形成工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 しきい値電圧のばらつきの少ないゲート電極を有するCMOSデバイスを備えた半導体装置を提供することを可能にする。

【解決手段】 半導体基板に設けられた第1導電型チャネルMISトランジスタと、半導体基板に設けられた第2導電型チャネルMISトランジスタと、を備え、第2導電型チャネルMISトランジスタのゲート電極中の、ゲート絶縁膜との界面から膜厚方向に少なくとも1nm以下の領域での酸素濃度は1020cm−3以上、1022cm−3以下である。

(もっと読む)

81 - 100 / 119

[ Back to top ]