Fターム[5F140BF40]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 複数種類を用い単純多層でないもの (119)

Fターム[5F140BF40]に分類される特許

41 - 60 / 119

半導体装置およびその製造方法

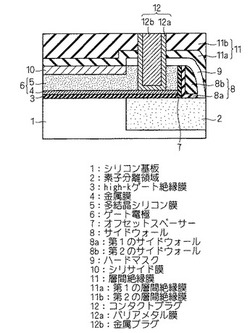

【課題】ゲート電極である金属膜/多結晶シリコン膜間の接触抵抗が大きい場合であっても、ゲートコンタクトプラグに印加した電界を十分な速度で十分に金属膜に伝えることができる半導体装置、およびその製造方法を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置は、半導体基板1と、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成された金属膜4、当該金属膜4上に形成された多結晶シリコン膜5、を有するゲート電極6と、ゲート電極6上に形成された層間絶縁膜11と、層間絶縁膜11および多結晶シリコン膜5を貫通して金属膜4と接触するように形成されたコンタクトプラグ12と、を備える。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13、チャネル形成領域12、ゲート電極423、ゲート絶縁膜430を備え、ゲート絶縁膜430はゲート絶縁膜本体部430A及びゲート絶縁膜延在部430Bから構成されており、ゲート電極を構成する第1層431はゲート電極の側面部の途中まで薄膜状に形成されており、第2層の外側層432Aは第1層431の上に薄膜状に形成されており、第2層の内側層432Bは第2層の外側層で囲まれた部分を埋め込んでおり、第3層の外側層433Aは第2層の内側層、外側層、ゲート絶縁膜延在部を覆い、ゲート電極の頂面まで薄膜状に形成されており、第3層の内側層433Bはゲート電極の残部を占めている。

(もっと読む)

パワー半導体装置およびパワー半導体装置の製造方法

【課題】ドレイン領域とドリフト領域との境界近傍における電界集中を緩和することにより、パワー半導体装置のドレイン耐圧を改善する。

【解決手段】パワー半導体装置10は、チャネル領域を含むボディ領域70と、チャネル領域の上にゲート絶縁膜50を介して形成されたゲート電極60と、ボディ領域に取り囲まれた領域に形成されたN型のソース領域130と、ゲート電極60から離間して形成されたドレイン領域140とを備える。ドレイン領域140の周りは、ドレイン領域より不純物濃度が低い拡散領域100により取り囲まれている。また拡散領域100とゲート電極60の下方領域との間に拡散領域100より不純物濃度が低いドリフト領域80が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜にHfを含むMOSトランジスタの特性のばらつきを抑制するために、Hf密度の面内ばらつきを少なくすることが必要である。

【解決手段】 半導体基板上に、熱酸化により酸化シリコンまたは酸窒化シリコンを含む絶縁膜(40)を形成する。絶縁膜の上にHfを含むガス(45)を供給して、絶縁膜の上にHf原子(41)を堆積させる。Hf原子が堆積している絶縁膜を、酸素雰囲気中(46)で熱処理する。酸素雰囲気中で熱処理した後、絶縁膜の上に、ゲート電極(50P,50N)を形成する。ゲート電極の両側に、ソース領域及びドレイン領域(52P,52N)を形成する。

(もっと読む)

半導体装置

【課題】体格を大きくせずに、スイッチング損失の増大を抑制しつつ、ラジオノイズの発生を抑制することのできる半導体装置を提供する。

【解決手段】半導体基板の表面上に対をなして設けられた第1電極及び第2電極と、第1制御電極とを有し、第1制御電極と第1電極との間に入力される制御信号によって、第1電極と第2電極との間を流れる電流が制御されるトランジスタ素子を備えた半導体装置であって、第1制御電極には、制御信号が入力される部位と、半導体基板におけるチャネル形成領域と対向する領域であって第1電極側の端部との間に第1電位障壁が設けられている。制御信号に応じて、第1制御電極と第1電極との間の容量部の少なくとも一部が、第1電位障壁を介して充放電される。

(もっと読む)

半導体素子及びその製造方法

【課題】チャネルが上下方向に形成されるトランジスタアレイ内における各トランジスタの駆動電圧の伝達効率を増大させるための半導体素子及びその製造方法を提供すること。

【解決手段】本発明の半導体素子は、複数の柱パターンと、各々の前記柱パターンを囲むゲート絶縁膜と、各々の前記ゲート絶縁膜を囲み、かつ、隣接する前記ゲート絶縁膜間を連接する導電膜とを備え、該導電膜は、ゲート電極及び配線として機能することを含む。

(もっと読む)

フィン型トランジスタ

【課題】フィン内部のチャネル部に垂直応力を与える事が可能なフィン型トランジスタを提供する。

【解決手段】基板と、前記基板上に形成される複数の半導体フィンと、前記半導体フィン内のチャネル領域を覆い金属または導電性を持つ化合物や、ポリシリコンで形成されるゲート電極と、前記ゲート電極の内部に含まれその両側に存在する前記半導体フィンに対し応力源となるよう格子定数の異なる材料や密度の異なるアモルファスシリコン、または線膨張係数の異なる材料で形成される埋め込み部材とを備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】電極の接触抵抗の低減によって高性能化した半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体基板上に第1の金属を堆積する工程と、第1の熱処理により第1の金属と半導体基板を反応させて、前記ゲート電極両側の前記半導体基板表面に金属半導体化合物層を形成する工程と、金属半導体化合物層中に、Siの原子量以上の質量を有するイオンをイオン注入する工程と、金属半導体化合物層上に第2の金属を堆積する工程と、第2の熱処理により、第2の金属を金属半導体化合物層中に拡散させることで、金属半導体化合物層と半導体基板の界面に、第2の金属を偏析させて界面層を形成する工程を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動能力を低下させることなく、半導体装置内部の高電界が与える影響によって生じるGIDLを低減する。

【解決手段】ゲート電極108は、ゲート電極108のチャネル長方向の中央部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第1の導電部108Aと、ゲート電極108のチャネル長方向の両端部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第2の導電部108Bとを含む。第1の導電部108Aの第1の仕事関数と第2の導電部108Bの第2の仕事関数とが異なっている。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETにおいて、従来のFinFETの構造に比してさらにチャネルに応力を印加することができる半導体装置を提供すること。

【解決手段】Si基板1と、フィン11、フィン11の延在方向に平行な面上にゲート絶縁膜13を介して形成される所定の幅のゲート電極14、およびフィン11の延在方向に平行な面上のゲート電極14の両側に形成されるソース/ドレイン領域を含むFinFET10n,10pと、を備え、ゲート電極14上に形成され、応力印加層31,32の形成温度と室温での線膨張係数の差が、フィン11の形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層31,32と、応力印加層31,32上に形成され、フィン11よりもヤング率の大きい導電性材料からなるプラグ層33,34と、を備える。

(もっと読む)

半導体装置

【課題】電流駆動能力が高いMOSFETを備えた半導体装置を提供する。

【解決手段】半導体装置1において、シリコン基板2の表面にNMOS3を形成し、NMOS3のチャネル領域7の直上域に、内部に圧縮応力を有する圧縮応力膜8を設け、シリコン基板2上における少なくともチャネル領域7の直上域の周囲に、内部に引張応力を有する引張応力膜9を設ける。

(もっと読む)

スプリット仕事関数ゲートを含むMOSFETを有する集積回路

【課題】ゲート誘起ドレインリーク電流が少ない電界効果トランジスタ、および、ゲート電極とソース/ドレイン領域との間に薄い絶縁体構造物を含む集積回路を提供する。

【解決手段】トランジスタ542のゲート電極は、ゲート電極とチャネル領域512との間の第1のフラットバンド電圧を決定する主部532と第1の側部535とを含む。この第1の側部は、上記主部に接触すると共に、上記ゲート電極と第1のソース/ドレイン領域514,516との間の第2のフラットバンド電圧を決定する。上記第1のフラットバンド電圧および上記第2のフラットバンド電圧は、少なくとも0.1eVだけ異なる。

(もっと読む)

半導体素子、高電圧トランジスタ及び半導体素子の製造方法

【課題】高い降伏電圧を持つ半導体素子及びその製造方法を提供する。

【解決手段】半導体素子は、半導体基板100に形成された第1導電型ウェル領域に相互離隔して形成される第2導電型ドリフト領域、ドリフト領域310上に突起されるバーティカル領域320、及びバーティカル領域上に形成される第2導電型ソース/ドレイン領域600を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲートトランジスタにおいて、溝に埋め込まれたゲート電極とゲート絶縁膜との界面にボイドが形成されることを防止する。

【解決手段】半導体基板1に埋め込まれた素子分離絶縁膜3により絶縁分離された活性領域4と、ゲート絶縁膜5を介して活性領域4上を跨ぐように形成されたゲート電極6と、ゲート電極6を挟んだ両側の活性領域4に形成されたソース領域7a及びドレイン領域7bとを有し、活性領域4に溝8が設けられて、この溝8の内側にゲート絶縁膜5を介してゲート電極6の一部が埋め込まれてなるトレンチゲートトランジスタ51を備える半導体装置であって、溝8が少なくとも上端開口部よりも下部側において幅広となる形状を有し、溝8に埋め込まれたゲート電極6内に外殻層13aで覆われた中空部(ボイド)14が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート長を増加させずにゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11上の絶縁膜12に形成されたゲート形成溝13の内部にゲート絶縁膜16を介してゲート電極17が形成され、前記ゲート電極17の一方側の前記半導体基板11にソース領域14が形成され、他方側の前記半導体基板11にドレイン領域15が形成された半導体装置1において、前記ゲート電極17は、前記ゲート形成溝13内から前記絶縁膜12表面より突出して形成されたゲート電極本体部30と、前記ゲート電極本体部30の前記絶縁膜12表面より突出した部分の側壁に形成された導電性のサイドウォール18とを有することを特徴とする。

(もっと読む)

二酸化窒素センサ

【課題】 固体電解質を用いたガスセンサは、検知電極と参照電極を必要とし、安定性に欠ける問題がある。また、補助相となるイオン導電体をゲート電極上に設けたFET型のガスセンサは、参照電極を用いないため小型化が可能であるが、NO2の選択性と応答速度に問題があった

【解決手段】 一導電型半導体層表面の一導電型の第1半導体領域の両側に、n型の第2半導体領域および第3半導体領域を設け、これらにそれぞれ接続する第2電極および第3電極を設ける。第1半導体領域とコンタクトする絶縁膜をp型半導体層上に設け、第1半導体領域に電圧を印加する第1電極を設ける。第1電極の一部を被覆し、第1半導体領域上の絶縁膜とコンタクトする補助相を設ける。補助相はイオン導電体(NaNO2)内に、貴金属(Ru)を担持した金属酸化物(WO3)を分散させてなり、これによりNO2の選択性、応答・回復特性が良好なNO2センサを得る。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート電極の上方にコンタクトプラグを形成するときに、ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13及びチャネル形成領域12、ゲート電極23、並びに、ゲート絶縁膜30を備えており、ゲート絶縁膜30は、ゲート電極23とチャネル形成領域12との間に形成されたゲート絶縁膜本体部30A、及び、ゲート絶縁膜本体部30Aからゲート電極23の側面部23Aの途中まで延在するゲート絶縁膜延在部30Bから構成されており、チャネル形成領域12の表面を基準としたゲート電極23の高さをHGate、ゲート絶縁膜延在部30Aの高さをHInsとしたとき、HIns<HGateを満足する。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置

【課題】電界緩和層領域におけるゲート電界の影響を抑制しながら、ゲート容量を小さくすることが可能な半導体装置を提供する。

【解決手段】この半導体装置100は、互いに所定の間隔を隔てて形成されたソース領域7およびドレイン領域9と、チャネル領域5aを含むボディ領域5と、電界緩和層3と、ボディ領域5と電界緩和層3との表面上に形成されたゲート絶縁膜13と、ゲート絶縁膜13の表面上に形成され、不純物領域14と、不純物領域14よりも低い不純物濃度を有する空乏層形成領域15とが形成されたポリシリコン層32からなるゲート電極16とを備えている。そして、空乏層形成領域15は、ゲート電極16のドレイン領域9側の端部16aから中央部の近傍の領域に渡って形成されている。

(もっと読む)

半導体装置

【課題】ゲート電極に電圧が印加されないときにも、ゲート電極とドレイン領域との間の電界を緩和し、ゲート絶縁膜に電界集中が発生するのを抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置100は、互いに所定の間隔を隔てて形成されたソース領域7およびドレイン領域9と、ソース領域7に接するように形成され、チャネル領域5aを含むボディ領域5と、電界緩和層3と、ボディ領域5と電界緩和層3との表面上に形成されたゲート絶縁膜13と、ゲート絶縁膜13の表面上に形成され、不純物領域14と不純物領域15とが接触するように形成されたポリシリコン層32を含むゲート電極16とを備えている。そして、不純物領域15は、ゲート電極16のドレイン領域9側に形成されている。

(もっと読む)

41 - 60 / 119

[ Back to top ]