Fターム[5F140BF40]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 複数種類を用い単純多層でないもの (119)

Fターム[5F140BF40]に分類される特許

101 - 119 / 119

半導体装置およびその製造方法

【課題】 本発明は、耐熱性に優れた半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 第1の発明の半導体装置は、第1導電型の半導体層と、第1導電型の半導体層上に形成された第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成され、Ruからなる第1の金属の結晶粒および第1の金属の結晶粒の粒界に偏析したW、Ni、Mo、Rh、Pd、Re、IrおよびPtからなる群から選ばれる第2の金属を有する第1のゲート電極と、第1のゲート絶縁膜をゲート長方向に挟む第1導電型の半導体層に形成された第1のソース・ドレイン領域と、を備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 ポリメタルゲート構造及びデュアルゲート構造のゲート電極を有する半導体装置において、ポリシリコン層中の不純物の相互拡散を防止すると共に、N型ポリメタルゲート電極とP型ポリメタルゲート電極の抵抗を共に低くすることが可能な半導体装置の製造方法を提供する。

【解決手段】 P型ポリメタルゲート電極10pが、P型ポリシリコン層104pと、P型ポリシリコン層104p上に不連続に配置された複数のタングステンシリサイド(WSi2)粒子105gからなるWSi2層105と、WSi2層105の不連続部分に露出したP型シリコン層104p上及びWSi2層105(WSi2粒子105g)表面に連続的に形成されたシリコン膜106と、窒化タングステン(WN)層107と、タングステン(W)層108とを備えて構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 MISFETを有する半導体装置の性能を向上させる。

【解決手段】 半導体基板1のp型ウエル7上にゲート絶縁膜8を介してゲート電極15が形成され、p型ウエル7にはソース・ドレインとしてのn+型半導体領域35が形成されている。ゲート電極15の両側壁上にはオフセットスペーサ23を介してサイドウォールスペーサ33が形成され、サイドウォールスペーサ33の側面34aには凹部34bが形成されている。ゲート電極15上およびn+型半導体領域35上に金属シリサイド膜43a,43bが形成され、金属シリサイド膜43aはゲート電極15の上面上だけでなく、サイドウォールスペーサ33の側面34aうちの凹部34bよりも上部の領域上にも延在している。金属シリサイド膜43bは、n+型半導体領域35の上に形成されている。

(もっと読む)

半導体装置

【課題】ゲート電極の空乏化を抑制しながら、電子移動度の劣化を低減することが可能な半導体装置を提供する。

【解決手段】この半導体装置は、pチャネル領域5aを挟むように所定の間隔を隔てて形成された一対のn型のソース/ドレイン領域6aと、pチャネル領域5a上にゲート絶縁膜7aを介して形成され、ポリシリコン層10aと、ポリシリコン層10aとゲート絶縁膜7aとの界面近傍に形成された金属含有層9aとを含むゲート電極8aと、nチャネル領域5bを挟むように所定の間隔を隔てて形成された一対のp型のソース/ドレイン領域6bと、nチャネル領域5b上にゲート絶縁膜7bを介して形成され、ポリシリコン層10bと、ポリシリコン層10bとゲート絶縁膜7bとの界面近傍に形成された金属含有層9bとを含むゲート電極8bとを備えている。また、金属含有層9aおよび9bは、PtおよびTaNを含む。

(もっと読む)

半導体装置

【課題】ゲート電極の空乏化を抑制しながら、電子移動度の劣化を低減することが可能な半導体装置を提供する。

【解決手段】この半導体装置では、nチャネルMOSトランジスタ50aのゲート電極8aは、ゲート絶縁膜7aを部分的に覆うようにドット状に形成された金属含有層9aと、金属含有層9a上に形成され、ゲート絶縁膜7aの金属含有層9aにより覆われていない部分に接触する下部ポリシリコン層10aとを含み、pチャネルMOSトランジスタ50bのゲート電極8bは、ゲート絶縁膜27aを部分的に覆うように形成された金属含有層29aと、金属含有層29a上に形成され、ゲート絶縁膜27aの金属含有層29aにより覆われていない部分に接触する下部ポリシリコン層30aとを含み、ゲート電極8aおよびゲート電極8bは、互いに異なる金属(HfおよびPt)を含む。

(もっと読む)

リセスチャネル構造を有するセルトランジスタを含む半導体装置およびその製造方法

【課題】動作電圧の変動が少なく、正常に動作する半導体装置を提供すること。

【解決手段】表面チャネル型nMOSFET構造を備えたトランジスタ構造および表面チ

ャネル型pMOSFET構造を有備えたトランジスタ構造を有するデュアルゲート型周辺

トランジスタと、リセスチャネル構造を備えたnMOSFET構造を有するセルトランジ

スタと、を含む半導体装置であって、前記セルトランジスタ中のゲート電極を構成するN

型ポリシリコン層に含まれるN型不純物の濃度が、略一定である半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極にシリサイドを使用し、ゲート絶縁膜に高誘電率ゲート絶縁膜を使用する半導体装置において、高誘電率ゲート絶縁膜近傍やゲートエッジに高誘電率ゲート絶縁膜/シリコン界面が生じない半導体装置の製造方法を得ること。

【解決手段】基板上にゲート絶縁膜と多結晶シリコン膜の積層体を形成する工程と、積層体の側壁に第1のサイドウォールを形成する工程と、第1のサイドウォールの周囲に第2のサイドウォールを形成する工程と、積層体の下方のチャネル領域を挟んだ領域にソース/ドレイン領域を形成する工程と、第1のサイドウォールを除去して、積層体と第2のサイドウォールとの間に空隙を生成する工程と、多結晶シリコン膜をシリサイド化させるための金属膜を、空隙を満たすように基板上に形成し、該金属膜を多結晶シリコン膜に拡散させて、多結晶シリコン膜全体をシリサイド膜にする工程と、を含む。

(もっと読む)

MOSトランジスタのためのゲート電極

一態様では、シリコン層(112')に第1の熱処理を施し、このシリコン層(112')上に金属積層体(110')を形成し、この金属積層体に第2の熱処理を施すことによって、トランジスタのゲートを形成する。第1の熱処理は、急速熱アニールステップを含み、第2の熱処理は、急速窒化ステップを含む。本発明により得られたるゲートは、シリコン層と金属積層体との間で比較的低い界面接触抵抗を示し、そのため、このゲートを高速デバイスで使用すると有利である。  (もっと読む)

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】集積回路の信頼性を損なうことなく、微細化を促進できる絶縁ゲート型電界効果トランジスタを備えた半導体集積装置およびその製造方法を提供できる。

【解決手段】半導体集積装置は、半導体基板21内から半導体基板上面に突出して設けられた、前記半導体基板に素子領域を区画する素子分離絶縁膜STIと、前記素子領域上に設けられたゲート絶縁膜31と、前記ゲート絶縁膜上に設けられたゲート電極32と、前記ゲート電極の両側に位置する前記半導体基板内に設けられたソース/ドレイン領域S/Dと、前記ゲート電極上に設けられた絶縁膜34と、前記絶縁膜を貫通し、前記ゲート電極に接触するコンタクト配線35とを備え、前記ゲート電極が有する側壁のうちの2つの相対した側壁が前記素子分離絶縁膜に接し、前記ゲート電極のゲート幅が前記素子分離絶縁膜によって規定されている絶縁ゲート型電界効果トランジスタTRを複数具備する。

(もっと読む)

加算素子及びその駆動方法

【課題】共通中間電極109の電位が、いわゆる電界効果型トランジスタのサブスレッショルド領域にある場合が多く発生するので、ソース101とドレイン103の間を流れる電流が大きくなり、結果として消費電力が増加する。

【解決手段】共通中間電極5と、共通中間電極5に複数のキャパシタを介して接続された複数の入力ゲート電極9と、共通中間電極5と接続された閾値素子53とからなる加算素子51であって、入力ゲート電極9の少なくとも一部が電圧発生器31に接続されているので、非使用時の電力消費を抑制することができる。

(もっと読む)

半導体装置

【課題】素子特性を向上させることができる半導体装置を提供する。

【解決手段】本発明の半導体装置は、凸形状の半導体素子領域23を有する基板21と、素子領域23の上面及び側面に形成されたゲート電極と、素子領域23を被覆し且つコンタクトホールが設けられた絶縁膜41と、コンタクトホールを埋め込み且つ素子領域23と接触した第1及び第2コンタクト配線43とを具備し、素子領域23内にはソース領域47とドレイン領域48とが互いから離間して及び第1及び第2コンタクト配線43とそれぞれ接触して設けられ、少なくとも一方のコンタクト配線43は素子領域23の上面の一部と側面の一部との双方に接触し、そのコンタクト配線43と接触したソース領域47またはドレイン領域48の厚さはコンタクト配線43と接触していない位置に比べコンタクト配線43と接触した位置でより厚い。

(もっと読む)

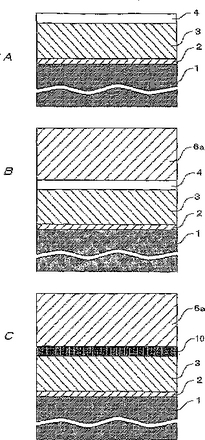

MIS型半導体装置およびMIS型半導体装置の製造方法

ゲート絶縁膜に高誘電率膜を用いるMOSFETにおいて、基板−高誘電率膜間の低誘電率層(シリコン酸化膜)を増大させないようにするために、基板(1)上に高誘電率膜(3)、拡散バリア層(4)を堆積した後、高誘電率膜(3)の膜質改善のための熱処理を行う。次に、ゲート電極材料膜を堆積し、これをパターニングしてゲート電極(6)を形成する。このエッチング工程において、高誘電率膜3)はその側面がプラズマに曝されることにより、電荷が注入されまたダメージを受ける。この電荷を逃がしダメージを修復するために拡散バリア層(8)でゲート部を含む全面を被覆して熱処理を行う。その後、ソース・ドレイン領域となる不純物拡散層を形成する。  (もっと読む)

(もっと読む)

半導体集積回路装置およびその製造方法

ポリメタルゲートを構成する高融点金属膜の洗浄工程における欠けを防止し、装置の特性を向上させ、また、洗浄効率を向上させるため、基板1上の低抵抗多結晶シリコン膜9a、WN膜9bおよびW膜9cを、窒化シリコン膜10をマスクにドライエッチングし、これらの膜よりなるゲート電極9を形成し、ウエットハイドロゲン酸化により薄い酸化膜9dを形成した後、RPN法を用いて窒化処理を行い、ゲート電極の側壁から露出したW膜9cをWN膜9eとする。その結果、その後の洗浄工程、例えば、n−型半導体領域11やp−型半導体領域12の形成時に行われる、1)レジスト膜のホトリソグラフィー工程、2)不純物の注入工程、3)レジスト膜の除去工程および4)基板表面の洗浄工程が繰り返し行われても、W膜9cの欠けを防止でき、また、洗浄液としてU洗浄液やフッ酸系の洗浄液のような強い洗浄液を用いることができる。  (もっと読む)

(もっと読む)

半導体装置のシリサイド膜の形成方法

【課題】 半導体装置のシリサイド膜の製造方法が開示される。

【解決手段】 まず、第1シリサイド膜を形成する。そして、前記第1シリサイド膜のうち、不連続部分がある場合、前記不連続部分に金属物質を選択的蒸着して、前記金属物質によって電気的に連結された第2シリサイド膜を形成する。前述した方法は、80nm以下のデザインルールを有する半導体ゲート電極上に不連続部分を含まないシリサイド膜を形成することができるのみならず、不連続部分を連結する工程で追加熱処理工程を行わなくても良いので、トランジスタの特性劣化を防止することができる。

(もっと読む)

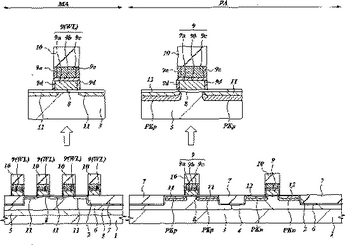

半導体装置の製造方法及び半導体装置

【課題】 低抵抗のゲート電極配線を形成することが可能な半導体装置の製造方法及び半導体装置を提供する。

【解決手段】 半導体基板上の所定領域にポリシリコン層を形成する工程と、前記ポリシリコン層の上面と、側壁の少なくとも一部が露出するように、第1の絶縁膜を形成する工程と、少なくとも露出した前記ポリシリコン層上に第1の金属膜を形成し、前記ポリシリコン層の少なくとも一部をシリサイド化する工程と、前記第1の絶縁膜を除去した後、前記ポリシリコン層の上面及び前記半導体基板の所定領域が露出するように第2の絶縁膜を形成する工程と、少なくとも露出した前記ポリシリコン層及び前記半導体基板上に、第2の金属膜を形成し、前記ポリシリコン層及び前記半導体基板の少なくとも一部をシリサイド化する工程を備える。

(もっと読む)

スタック状ヘテロドーピング周縁部及び徐々に変化するドリフト領域を備えた促進された表面電界低減化高耐圧P型MOSデバイス

基板(20)上に形成された高耐圧P型MOSデバイス(12)は、第2極性タイプのエピタキシャル層(22)内に形成された第1極性タイプのHVウエル(26)を有し、該基板上において少なくとも部分的にHVウエルの上部に1対のフィールド酸化領域(32、34)を有している。絶縁ゲート(40、42)が該基板上においてフィールド酸化領域の間に形成されている。スタック状のヘテロドーピングされた周縁部(50、52、60、62)がHVウエル内において両ゲートの外側端部に自己アラインメントして形成されている。第1極性タイプのバッファ領域(66)がHVウエル内において両ゲートの内側端部の間に自己アラインメントして形成されている。第2極性タイプのドリフト領域(68)がバッファ領域内において両ゲートの内側端部の間に自己アラインメントして形成されている。該ドリフト領域はドーパント濃度が徐々に変化する領域(104)を有し、これは第2極性タイプのドレイン領域(110)を含んでいる。  (もっと読む)

(もっと読む)

非対称なヘテロドープされた高電圧のMOSFET(AH2MOS)

非対称なヘテロドープされた金属酸化物(AH2MOS)半導体デバイスは基板と、前記基板の頂部にあってソース領域とドレイン領域との間に配置された絶縁ゲートと、からなる。ゲートの一方の側面には、ヘテロドープされたタブ及びソース領域が形成されている。タブ領域は第2極性のドーパントを有している。ソース領域が各タブ領域内に配置されており、第2極性と反対の第1極性のドーパントを有している。ゲートの他方の側面には、ヘテロドープされたバッファ及びドリフト領域が形成されている。バッファ領域は第2極性のドーパントからなる。ドリフト領域がバッファ領域内に配置され、第1極性のドーパントによってドーピングされている。ドレインn+タップ領域がドリフト領域内に配置されている。  (もっと読む)

(もっと読む)

半導体装置

【課題】 ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】 ソース/ドレイン領域の一方になり、かつビット線にもなる第1の不純物拡散層24の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

101 - 119 / 119

[ Back to top ]