Fターム[5F140BF45]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 形状、配置 (2,388) | 埋込みゲート、チャネルの下に埋込み (26)

Fターム[5F140BF45]に分類される特許

1 - 20 / 26

炭素ベース材料上の向上した結合界面を有する半導体構造体、その形成方法、及び、電子デバイス

【課題】 高密度で、構造部寸法がより小さく、より正確な形状の半導体構造体及び電子デバイスを提供する。

【解決手段】 炭素ベース材料の上面上に配置された少なくとも一層の界面誘電体材料を含む、半導体構造体及び電子デバイスが提供される。少なくとも一層の界面誘電体材料は、炭素ベース材料のものと同じである、典型的には六方晶短距離結晶結合構造を有し、従って、少なくとも一層の界面誘電体材料が、炭素ベース材料の電子構造を変えることはない。炭素ベース材料のものと同じ短距離結晶結合構造を有する少なくとも一層の界面誘電体材料の存在により、炭素ベース材料と、誘電体材料、導電性材料、又は誘電体材料及び導電性材料の組み合わせを含む、上にある任意の材料層との間の界面結合が改善される。その結果、改善された界面結合が、炭素ベース材料を含むデバイスの形成を容易にする。

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】駆動電流の増大を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に線状に形成された第2部分12bと、を有する第2半導体層12と、前記第2半導体層の前記第2部分の周囲に絶縁膜17を介して形成されたゲート電極18と、を具備し、前記第2半導体層の前記第2部分の膜厚は、前記第2半導体層の前記第1部分の膜厚より小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低下を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に形成された第2部分12bとを有する第2半導体層12と、前記第2半導体層の前記第1部分上に形成された第3半導体層13と、前記第2半導体層の前記第2部分の周囲に絶縁膜21を介して形成されたゲート電極22と、前記第1半導体層、前記第2半導体層の第1部分および前記第3半導体層内に形成されたコンタクトプラグ31と、を具備し、前記第2半導体層内における前記コンタクトプラグの径は、前記第1半導体層及び前記第3半導体層内における前記コンタクトプラグの径より小さい。

(もっと読む)

フィンタイプデバイスシステム及び方法

フィンタイプデバイスシステム及び方法が開示される。特定の実施形態において、表面を有する基板内にトランジスタのゲートを形成する段階と、前記基板内に、第1BOX層面において前記ゲートに隣接する埋込酸化物(BOX)層を形成する段階と、を含むトランジスタの製造方法が開示される。本方法はまた、レイズドソース−ドレインチャネル(フィン)を形成する段階であって、前記フィンの少なくとも一部が前記基板の表面から延長し、前記フィンが、前記BOX層の第2BOX層面に隣接する第1フィン面を有する段階を含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】ゲート・オール・アラウンドトランジスタの複数のチャネルそれぞれに流れる電流を均一にし、ゲート・オール・アラウンドトランジスタの信頼性を向上させる。

【解決手段】半導体基板と、半導体基板上に一定の間隔をおいて形成された第1の半導体層上に第2の半導体層を形成した積層構造が複数積み重なったソース・ドレイン領域と、第2の半導体層の同一レイヤ間をそれぞれ接続するようにワイア状に形成された複数のチャネル領域と、前記複数のチャネル領域をそれぞれ包み込むようにゲート絶縁膜を介して形成されたゲート電極とを具備し、チャネル領域のチャネル幅は、半導体基板から離れるほど狭く形成され、第2の半導体層及びチャネル領域の膜厚は、半導体基板から離れるほど広く形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、ゲート容量が大きく、スイッチング素子としての高速動作が実現し難いという問題があった。

【解決手段】本発明の半導体装置では、トレンチ9内にはゲート酸化膜10、絶縁スペーサー11及びゲート電極12が形成され、絶縁スペーサー11はトレンチ9の側面に沿って一環状に形成される。この構造により、絶縁スペーサー11の膜厚によりゲート容量が低減し、高集積化によるオン抵抗値も低減することで、スイッチング素子としての高速動作が実現される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の周囲、全周にわたってチャネル領域を形成することで、単位面積当たりの電流量を増加させることを可能にする。

【解決手段】半導体領域11と、前記半導体領域11中に配置されたゲート電極21と、前記ゲート電極21の周囲に形成されたゲート絶縁膜22と、前記ゲート電極21の一端に前記ゲート絶縁膜22を介して形成されたソース・ドレイン電極になる第1不純物領域23と、前記ゲート電極21を横切るように前記半導体領域11に前記ゲート絶縁膜22を介して形成されたソース・ドレイン電極になる第2不純物領域24と、前記ゲート電極21の他端に接続されたゲート引き出し電極25を有し、前記第1不純物領域23と前記第2不純物領域24との間の前記ゲート電極21周囲の前記半導体領域11にチャネル領域が形成される。

(もっと読む)

絶縁膜層分離IC製造

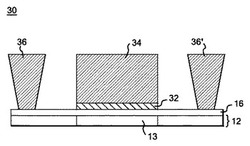

【課題】二酸化ケイ素や窒化ケイ素など非常に薄い低応力誘電体材料と半導体層とで形成された可とう性の膜で集積回路(24、26、28、...30)を製造する汎用手法を提供する。

【解決手段】膜(36)の半導体層中に半導体デバイス(24、26、28...30)を形成する。最初に、標準厚さの基板(18)から半導体膜層(36)を形成し、次いで、基板の薄い表面層をエッチングまたは研磨する。他のバージョンでは、ボンディングされた従来の集積回路ダイ用の支持および電気的相互接続として可とう性膜を使用し、膜中の複数の層に相互接続部を形成する。1つのそのような膜に複数のダイを接続することができ、膜は次いでマルチチップ・モジュールとしてパッケージされる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】SOI層の膜厚が薄膜化してもMOSトランジスタの駆動能力の向上を図ることができる半導体装置及びその製造方法を得る。

【解決手段】NMOS形成領域A1に形成されるNMOSトランジスタQ11において、ソース・ドレイン領域15は埋め込み酸化膜4を貫通して半導体基板1の閾値電圧制御拡散層18に達して形成される。PMOS形成領域A2に形成されるPMOSトランジスタQ21において、ソース・ドレイン領域25は埋め込み酸化膜4を貫通して半導体基板1の閾値電圧制御拡散層28に達して形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法並びにデータ処理システム

【課題】動作特性の制御が容易で微細化に有利なトランジスタを有する半導体装置およびその製造方法並びにデータ処理システムを提供する。

【解決手段】活性領域K内に設けられたトレンチ100と、トレンチ100と第1素子分離領域S1との間の活性領域Kに形成されたフィン型チャネル領域185と、第1素子分離領域S1に埋設され、第1ゲート絶縁膜141を介してフィン型チャネル185と接する第1ゲート電極151と、トレンチ100に埋設され、第2ゲート絶縁膜191を介してフィン型チャネル185と接する第2ゲート電極225と、フィン型チャネル185と接続され、活性領域K内において第2ゲート電極225を挟んでトレンチ100の両側に位置するソース/ドレイン拡散領域241とを具備してなるトレンチゲート型MOSトランジスタTrを有する半導体装置1を採用する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】チャネルのサイズおよび形状の揺らぎを可及的に抑制するとともに、チャネルの幅が可及的に小さい電界効果トランジスタを提供することを可能にする。

【解決手段】Siを含む半導体層を上面に備えた半導体基板4上に、絶縁膜のマスク9を形成する工程と、マスクを用いてエッチングを行うことにより半導体層を半導体基板の上面に平行な一方向に延在するメサ状に加工する工程と、水素雰囲気中での熱処理を行うことにより、半導体層の一方向に延在しかつ対向する一対の側面間の距離を狭くするとともに側面を平坦化する工程と、側面が平坦化された半導体層を覆うゲート絶縁膜12を形成する工程と、ゲート絶縁膜を覆うゲート電極13を形成する工程と、ゲート電極の両側の半導体層にソース/ドレイン領域を形成する工程と、を備えている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】超短チャネル長化でき、Si層厚一定によって閾値を変化させずにON電流を増加でき、さらにバックゲートにより閾値も動的に変更できる縦型トランジスタ構造を備えた半導体装置および半導体装置の製造方法を提供することを目的とする。

【解決手段】基板2上に、中心軸Mが基板2面と垂直方向に形成されてなる筒型の基柱3と、基柱3の上部と下部に、中心軸Mを中心とする同心形状に形成された第1導電型からなるソース・ドレイン拡散層4a,4bと、ソース・ドレイン拡散層4a,4bに挟まれた基柱3の中間部に形成された第1導電型からなるボディ層と、基柱3の側面にゲート絶縁膜6を介して形成されたフロントゲート電極7とを備えたことを特徴とする。また、第2導電型からなるバックゲート電極8が、基柱3の内側に上部から下部まで貫通する柱状に形成されてなることとする。

(もっと読む)

電界効果トランジスタ、集積回路素子、及びそれらの製造方法

【課題】Ge原子を含有するチャネル領域を具備するようなマルチゲート構造の電界効果トランジスタに関して、新規な電界効果トランジスタを提案すること。

【解決手段】Si原子を含有する半導体基板と、前記半導体基板上に形成され、Si原子とGe原子とを含有する突起構造と、前記突起構造内に形成されており、Ge原子を含有するチャネル領域と、前記チャネル領域の下部に埋め込まれている絶縁膜と、前記突起構造内に形成されており、前記突起構造を通じて前記半導体基板とつながっているソース・ドレイン領域と、前記チャネル領域上に形成されたゲート絶縁膜と、前記チャネル領域上に前記ゲート絶縁膜を介して形成されたゲート電極とを具備する電界効果トランジスタ。

(もっと読む)

MOSトランジスタ、そのMOSトランジスタの製造方法、そのMOSトランジスタを利用したCMOS型半導体装置、及び、そのCMOS型半導体装置を利用した半導体装置

【課題】

本発明の目的は、上記のストレッサーが発生する応力がより効率的にMOSトランジスタのチャネル部に印加されるように、ストレッサーを配置したMOSトランジスタ、そのMOSトランジスタの製造方法、及び、そのMOSトランジスタを利用したCMOS型半導体装置を提供することにある。

【解決手段】

本発明は、シリコン基板と、シリコン基板上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極の両側に形成されたソース・ドレイン領域と、シリコン基板表面から離間し、前記ソース・ドレイン領域に挟まれた領域であって、ゲート電極下部のシリコン基板内部に形成され、応力発生物質が埋め込まれた、応力発生物質埋込領域と、を備えるMOSトランジスタ、そのMOSトランジスタの製造方法、及び、そのMOSトランジスタを利用したCMOS型半導体装置を提供する。

(もっと読む)

半導体素子及びその製造方法

【課題】電流駆動能力とショートチャンネル效果(Short channel effect)の改善でトランジスタの制御能力を向上させ高速の低電圧半導体素子を提供する。

【解決手段】本発明は半導体素子及びその製造方法に関し、特にゲート電極でサラウンディングチャンネル構造を取り囲むよう素子を設計することにより、電流駆動能力とショートチャンネル效果の改善によってトランジスタの制御能力を向上させ、高速の低電圧半導体素子を形成することができる技術である。

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域の構造を最適化することにより、高いIon/Ioff比を達成する電界効果トランジスタを含む半導体装置を提供する。

【解決手段】第1のゲート電極107と第2のゲート電極108は、チャネル領域101の両側に対向するように、第1のゲート絶縁膜103と第2のゲート絶縁膜104を介して、それぞれ形成され、ソース領域111および前記ドレイン領域121は、第1のゲート電極107と第2のゲート電極108の両側に、チャネル領域101を挟んで形成され、第1のゲート絶縁膜103とチャネル領域104との界面に垂直な方向のソース領域111の厚さ(TSis)が、同じ方向のチャネル領域101の厚さ(TSic)よりも厚く、かつ、ソース領域111と、第1、第2のゲート電極107、108が、ゲート長方向に離間している電界効果トランジスタを含む半導体装置。

(もっと読む)

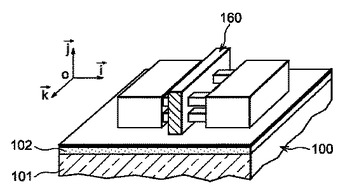

少なくとも1つの電子ビームによって前駆体材料を少なくとも1つの金属材料に分解することを含む、トランジスタゲートを製造する方法

本発明は、電子ビームに露出された後に少なくとも1つの金属材料に分解されることが可能な前駆体材料(150、250、350、450)からトランジスタゲート(160、260、360、460)を製造するマイクロエレクトロニクス法に関する。本発明は、特に、マルチチャネル、FinFET、懸架型チャネルトランジスタ、またはSONもしくはGAAタイプのトランジスタに適合する。  (もっと読む)

(もっと読む)

半導体装置

【課題】複数の半導体素子が集積された半導体装置にあって、それら半導体素子における電流分布の偏りを好適に抑制することのできる半導体装置を提供する。

【解決手段】半導体基板の上表面に延設されたトレンチ溝7A,7Bと、これらトレンチ溝7A,7Bの内部に埋め込まれたドレイン引出電極15A,15Bとを備えた半導体素子を複数併設して半導体装置を構成した。こうした半導体装置において、半導体素子の形成領域S全体の下方における半導体基板の内部に、半導体素子の形成領域Sの下方全体にわたる面状のN型埋込拡散層3をドレイン引出電極15A,15Bと接続された状態で埋込形成するようにした。

(もっと読む)

半導体装置

【課題】可及的に簡略な構成で、かつ高集積度、高性能の半導体装置を得ることを可能にする。

【解決手段】半導体基板1上に板状に設けられた第1導電型の第1半導体領域3と、第1半導体領域の第1側面に設けられた第1強誘電体絶縁膜4と、第1強誘電体絶縁膜の第1半導体領域と反対側の面に設けられた第1ゲート電極6と、第1半導体領域の第2側面に設けられた第2強誘電体絶縁膜5と、第2強誘電体絶縁膜の第1半導体領域と反対側の面に設けられた第2ゲート電極7と、第1及び第2ゲート電極に挟まれるように第1半導体領域に形成されるチャネル領域と、チャネル領域の両側の第1半導体領域に設けられた第2導電型の第1ソース・ドレイン領域8と、を備え、第1半導体領域の厚さが第1半導体領域の不純物濃度で決まる空乏層の最大厚さの二倍よりも薄い。

(もっと読む)

1 - 20 / 26

[ Back to top ]