Fターム[5F140BF47]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 形状、配置 (2,388) | 並列複数ゲート (130)

Fターム[5F140BF47]に分類される特許

1 - 20 / 130

半導体装置の製造方法

【課題】縦型トランジスタにおける上部拡散層の深さ方向のばらつきを低減することのできる半導体装置の製造方法を提供する。

【解決手段】本発明は表面が平坦なシリコン層からなる上部拡散層11を形成しようとするものであり、具体的には、ファセットを有するシリコン層を選択的に過剰成長させた後、層間絶縁膜7表面に形成されたシリコン層をCMPで擦り切ってシリコン層の表面を平坦化する。シリコン層の成長は、シリコン層を単結晶シリコンで選択的にエピタキシャル成長させる。この場合、ファセットが生じるので、最も成長が遅いファセットが層間絶縁膜表面より上方に位置するまで充分過剰に成長させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク基板上に形成されたフィン型トランジスタにおいて、ソース/ドレインボトム領域での接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上に形成されたシリサイドとの接触抵抗を低減する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

(もっと読む)

半導体装置およびその製造方法

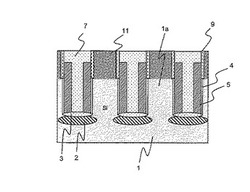

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置

【課題】特性の優れた半導体装置を提供する。

【解決手段】本発明の一態様にかかる半導体装置は、半導体基板1に設けられた第1導電型のN−型オフセット層8と、トレンチ12を有し、N−型オフセット層8の間に設けられた第2の導電型のチャネル領域13と、チャネル領域13の上に形成され、トレンチ12に埋設されたトレンチゲート10を有するゲート電極4と、を備えたトランジスタを含み、ゲート幅方向におけるトレンチゲート10の幅がゲート長方向の位置に応じて変化しているものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】閾値電圧のバラつきを抑制する溝トランジスタを提供する。

【解決手段】図1に示すように、表面に少なくとも一つ以上の溝部250を有している半導体基板40と、溝部250の側壁を覆うように形成されたゲート絶縁膜20と、溝部250に埋めこまれているゲート電極10と、半導体基板40の表面に形成され、ゲート電極10を介して互いに対向しているソースおよびドレイン150と、を含み、溝部250の側壁には、複数の凸凹100が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

半導体装置

【課題】放熱効率が高く低コストでの実装が可能な半導体装置を提供する。

【解決手段】第1の方向に延在するゲート電極を有する複数のトランジスタを有し、複数のトランジスタが第1の方向と交差する第2の方向に配置されたトランジスタアレイ54と、トランジスタアレイの第1の方向に配置され、複数のトランジスタのソース領域に電気的に接続されたパッド電極50とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置

【課題】MOSFETの耐圧を向上させる。

【解決手段】半導体基板上に形成された平面形状が円形の給電部1pと給電部1pを中心としたリング状のガードリング領域1gとの間に、給電部1pを中心として放射状に延在するゲート電極G1を給電部1pを中心とする円周上に並べて複数配置し、前記円周上で隣り合うゲート電極G1同士の間にソース領域S1またはドレイン領域D1を形成する。これにより、ゲート電極G1の下部のウエルとソース領域S1とドレイン領域D1との間に寄生バイポーラトランジスタが形成されることを防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧を向上した半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、第4半導体領域、ゲート領域、ゲート絶縁膜及び電界緩和領域を備える。第1導電形の第1半導体領域は、第1部分と第1方向に延出した第2部分とを有する。第1導電形の第2半導体領域は、第1部分上の第3部分と第2部分と隣接する第4部分とを有する。第2導電形の第3半導体領域は、第3部分上の第5部分と第4部分と隣接する第6部分とを有する。第1導電形の第4半導体領域は、第5部分上で第6部分と隣接する。ゲート領域は、第2半導体領域、第3半導体領域及び第4半導体領域を第2方向に貫通するトレンチ内に設けられる。ゲート絶縁膜は、トレンチ内壁とゲート領域との間に設けられる。第2導電形の電界緩和領域は、第3部分と第5部分との間に設けられ、第3半導体領域よりも不純物濃度が低い。

(もっと読む)

半導体装置

【課題】間接遷移型の半導体を用いた場合でも、単一の電子の転送により単一の光子が生成できるようにする。

【解決手段】p型領域102とn型領域103とに挾まれた領域の半導体層101に導入された第1不純物原子106および第2不純物原子107からなる不純物原子対を備える。ここで、不純物原子対は、p型領域102とn型領域103とが対向して配置されている方向(第1方向)で、p型領域102とn型領域103とに挾まれた領域(チャネル領域)に配置される。また、第1不純物原子106および第2不純物原子107は、上記チャネル領域のゲート電極105の側の界面より30nmの範囲に導入されている。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタが設計より低い閾値電圧で動作し始めるという寄生トランジスタ動作を抑制する。

【解決手段】半導体装置100は、基板102の素子形成領域に形成されたトレンチ162、トレンチ162の側壁および底面に形成されたゲート絶縁膜120、トレンチ162を埋め込むようにゲート絶縁膜120上に形成されたゲート電極122、基板102表面のゲート長方向の一方の側に形成されたソース領域112、およびゲート長方向の他方の側に形成されたドレイン領域113、を有するトランジスタを含む。ここで、ゲート電極122は、トレンチ162外部の基板102上にも露出して形成され、ゲート電極122は、ゲート長方向における、トレンチ162の両端部上部が覆われるとともに、中央部に少なくとも一つ深さが基板まで達する凹部が形成されるように設けられている。

(もっと読む)

スイッチング素子、高周波信号スイッチ及び高周波信号増幅モジュール

【課題】高周波信号経路を切り替えるために半導体基板上に形成された、小型でかつ低歪特性を実現するスイッチング素子を提供する。

【解決手段】スイッチング素子の一例であるFET100は半導体基板109上に形成された櫛型の2つのソース・ドレイン電極101と、2つのソース・ドレイン電極101の間を這うように配置された少なくとも2本のゲート電極102と、隣り合うゲート電極102の間に挟まれ、かつ、隣り合うゲート電極102に沿って配置された導電層103とを備え、ゲート電極102の2つのソース・ドレイン電極101の指状部と平行な部分である直線部108の直下に位置する層が、ゲート電極102の隣り合う一対の直線部108をつなぐ部分である屈曲部107の直下に位置する層から、電気的に分離されている。

(もっと読む)

半導体装置

【課題】MISFETにおけるAvt(Vtばらつき)のゲート幅依存性を考慮し、Vtミスマッチ及びVtばらつきを低減できるようにする。

【解決手段】半導体装置は、それぞれが半導体基板に形成され、ソースドレインを構成する拡散層205及び該拡散層205の上に形成されたゲート203を有し、且つ互いに並列接続された複数の単位MISFETから構成される複数のMISFET201、202を含む。MISFET201、202同士の間の閾値電圧のばらつきの標準偏差は、各MISFETにおける単位MISFETのそれぞれのゲート長とゲート幅との積の総和であるチャネル面積と同一の面積を有する単一のMISFET同士の間の閾値電圧のばらつきの標準偏差よりも小さい。

(もっと読む)

電界効果トランジスタ

【課題】スイッチング速度を向上でき、動作不良品を低減できる、横型の電界効果トランジスタを提供する。

【解決手段】ゲート配線43は、基部44と、基部44から突出する複数の指状部45と、隣接する指状部45の先端部46を接続する接続部47と、を有する。ゲート配線43の指状部45は、ソース配線23の指状部25とドレイン配線33の指状部35と、の間に配置されている。ゲート配線43の基部44は、ソース配線23の基部24とドレイン配線33の指状部35との間に配置され、かつ、ソース配線23の指状部25との間に絶縁膜を介在させて指状部25と交差している。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ構造を有するMOSトランジスタにおいて、チャネル領域のしきい値の適切な調整が可能となる半導体装置を提供する。

【解決手段】第1導電型半導体基板に作られたゲート幅方向に深さが変化する凹部領域と凸部領域の前記凹部領域はトレンチ構造で形成されているトレンチ構造を有するMOSトランジスタにおいて、前記第1導電型半導体基板表面に沿って成膜した犠牲酸化膜を介して形成された第1導電型ドープドポリシリコン膜を前記凹部領域のトレンチ構造に埋め込ませて熱処理をおこなうことで、前記トレンチ構造間の凸部領域上面およびトレンチ構造の凹部領域側面と底面に不純物拡散する。これにより、トレンチピッチが縮小されてもチャネルへの均一な不純物添加が可能になる。

(もっと読む)

半導体装置及び半導体装置の動作方法

【課題】トランジスタの閾値電圧を高くする。

【解決手段】フローティング電極110は半導体層102上に形成されており、絶縁層はフローティング電極110上に形成されている。バイアス電極134は、絶縁層を介してフローティング電極110の一部に対向することにより、フローティング電極110と容量結合し、かつフローティング電極110が半導体層102にチャネル領域を形成しない大きさの電圧が印加される。制御電極132は、絶縁層を介してフローティング電極110の他の部分に対向することにより、フローティング電極110と容量結合し、かつトランジスタのオン/オフを制御するための制御電圧が入力される。

(もっと読む)

窒化物半導体装置

【課題】エンハンメント型GaN系HFETの閾値電圧のバラツキを低減する。

【解決手段】窒化物半導体装置80では、第2のリセスエッチングによりアンドープGaN層3の上部に突起部51が設けられる。突起部51上には、上部が第1のリセスエッチングにより形成されたアンドープAlGaN層4aが設けられる。積層部7は、アンドープGaN層3の突起部51、アンドープAlGaN層4a、及び絶縁膜5から構成される。トレンチ部8は、絶縁膜5、アンドープAlGaN層4a、及びアンドープGaN層3表面がリセスエッチングされたものである。積層部7及びトレンチ部8上にはゲート絶縁膜6が設けられる。ゲート絶縁膜6上には、トレンチ部8を覆うようにゲート電極33が設けられる。絶縁膜5はゲート絶縁膜6よりも膜厚が厚く設定されている。

(もっと読む)

1 - 20 / 130

[ Back to top ]