Fターム[5F140BH10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 形状、配置 (1,748) | 複数ソース (72)

Fターム[5F140BH10]に分類される特許

1 - 20 / 72

半導体装置

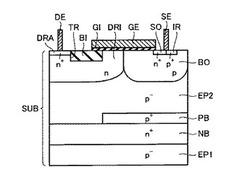

【課題】ハイサイド素子として用いても誤動作が少なく、かつオン耐圧およびオフ耐圧の双方を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が、その主表面側にはp-エピタキシャル領域EP2が、その主表面側にはn型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。p+埋め込み領域PBは、n型ドリフト領域DRIとp型ボディ領域BOとの接合部の少なくとも直下に位置し、かつn型ドリフト領域DRIと接するドレイン領域DRAの直下を避けて配置されている。

(もっと読む)

半導体装置

【課題】基板電位を安定化させることができる半導体装置を提供する。

【解決手段】半導体装置に含まれるFET素子1は、N角形をなす外周端部30pと貫通孔を形作る内周端部30iとを有する環状のゲート電極30を備える。またFET素子1は、貫通孔の直下方に形成された内側不純物拡散領域21と、ゲート電極30のN角形の辺の外側に形成された外側不純物拡散領域22A〜22Dと、ゲート電極30の頂点の外側に形成されたバックゲート領域23A〜23Dとを備える。バックゲート領域23A〜23Dは、ゲート電極30のN角形の辺のうちゲート電極30の頂点をなす2辺の延長線Ex,Eyの少なくとも一方を跨るように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の断線による縦型トランジスタの故障を改善すること。

【解決手段】半導体装置は、第1の方向(Y)に互いに隙間を空けて形成された複数の半導体ピラー(5A1〜5A5)から成る半導体ピラー群(5)を含む。半導体ピラー群(5)の内、両端部を除く中間部に位置する半導体ピラー(5A2〜5A4)のいずれか1つである特定の半導体ピラー(5A3)と隣接して、ダミーピラー(6)が第1の方向(Y)と直交する第2の方向(X)に設けられている。ゲート絶縁膜(10)が、複数の半導体ピラー(5A1〜5A5)の各々の外周面とダミーピラー(6)の外周面の一部とに形成されている。ゲート絶縁膜(10)を介して、複数の半導体ピラー(5A1〜5A5)の間の隙間と特定の半導体ピラー(5A3)とダミーピラー(6)との間の隙間とを埋めるように、ゲート電極(11)が、複数の半導体ピラーの側面とダミーピラーの側面とに形成されている。

(もっと読む)

高耐圧MOSFETの回路シミュレーション用モデルの作成方法と装置並びにプログラム

【課題】高耐圧MOSFETのモデルにおいて、ドレイン電流の精度を広いバイアス範囲で得ることができ、シミュレーションの精度を向上させる。

【解決手段】ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、ソース領域のソース拡散層の幅とウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFET1、2と、第2のMOSFET2のソースに一端が接続された第1の可変抵抗素子3を備え、第2のMOSFET2のソースと第1の可変抵抗素子3の他端との接続点をソース端子Sとし、第1及び第2のMOSFETの共通接続したドレイン、共通接続したゲート、共通接続したバックゲートをそれぞれドレイン端子D、ゲート端子G、バックゲート端子Bとするモデルを作成し、モデリング対象の高耐圧MOSFETの電気特性データに基づき、第1の可変抵抗素子3の抵抗値を調整する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

半導体装置及び半導体装置の検査方法

【課題】狭いゲート電極間にコンタクトを配置することなく、オーバーラップ容量を測定する。

【解決手段】この半導体装置は、下記のような第1TEGパターン(不図示)を備えている。第1TEGパターンは、素子分離領域500と、素子分離領域500に形成された開口部(不図示)と、開口部上に設けられ、互いに平行に延伸した複数のゲート電極300と、開口部のゲート電極300で覆われていない部分に形成された拡散領域200と、を備えている。ここで、ゲート電極300の一方の端部は、開口部の外縁よりも内側に配置されている。また、第1コンタクト240は、ゲート電極300の一方の端部と、開口部の外縁の間に位置して、拡散領域200に接続している。一方、第2コンタクト340は、ゲート電極300に接続している。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置

【課題】回路面積の増大を抑制しつつ高耐圧の半導体装置を得る。

【解決手段】第1導電型の第1半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度を有し、MOSトランジスタのドレイン領域として機能する。また、第1導電型の第2半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度より小さい第2の不純物濃度を有し、第1半導体層と接続されるように配置されてMOSトランジスタのドリフト層として機能する。素子領域及び素子終端領域は、第1方向と直交する第2方向の幅が同一であり、第2方向に沿った断面に関し、素子終端領域における第2半導体層の幅は、素子領域における第2半導体層の幅よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】フィントランジスタのオン電流のばらつきを抑制する。

【解決手段】半導体基板10の上に形成され、半導体基板10から突出するフィン活性領域15a,15bと、半導体基板10の上に形成され、フィン活性領域15a,15bの下部の側面を覆う素子分離膜16と、素子分離膜16から突出するフィン活性領域15a,15bの中央部及び上部のうち、中央部の側面の上に形成されたサイドウォール18a,18bとを備えている。フィン活性領域15a,15bの上部は、サイドウォール18a,18bから突出している。

(もっと読む)

半導体装置

【課題】横型構造のパワートランジスタにおいて、寄生サイリスタのラッチアップ耐量を改善するとともに、ターンオフ時間を短縮する。

【解決手段】エミッタ電極(21)下部に設けられるn+エミッタ層(6)を、所定の間隔で互いに離れて配置される単位領域(60)で構成する。単位領域においてエミッタ電極とのコンタクトを取るとともに、pベース層(5)よりも高濃度でp+層(45)を少なくともエミッタ層の下方に設ける。

(もっと読む)

半導体装置

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有し、第1導電型のバックゲートコンタクト領域を有さない第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

半導体装置及びその製造方法

【課題】パワーデバイスの高耐圧とオン抵抗の低減とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板101内のソース領域107A、ドレイン領域107B、及びドレイン領域107Bに接したドリフト領域105と、ソース領域107A及びドレイン領域107B間のドリフト領域105内のSTI絶縁層I−2と、STI絶縁層I−2上、ドリフト領域105上、並びに、ソース領域107A及びドレイン領域107B間のチャネル領域上のゲート電極110とを備える。STI絶縁層I−2は、第1及び第2のトレンチの内面上の第1の酸化膜102及び窒化膜103と、第1及び第2のトレンチを満たす窒化膜103上の第2の酸化膜104とを備える。第2のトレンチは、第1のトレンチ内に形成され、第1のトレンチの底面よりも低い底面を有し、第1のトレンチの幅よりも狭い幅を有する。

(もっと読む)

半導体装置

【課題】MOSFETの耐圧を向上させる。

【解決手段】半導体基板上に形成された平面形状が円形の給電部1pと給電部1pを中心としたリング状のガードリング領域1gとの間に、給電部1pを中心として放射状に延在するゲート電極G1を給電部1pを中心とする円周上に並べて複数配置し、前記円周上で隣り合うゲート電極G1同士の間にソース領域S1またはドレイン領域D1を形成する。これにより、ゲート電極G1の下部のウエルとソース領域S1とドレイン領域D1との間に寄生バイポーラトランジスタが形成されることを防ぐ。

(もっと読む)

電界効果トランジスタの高電圧動作方法とそのバイアス回路

【課題】 ICないしLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該ICないしLSI中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートを分割してドレインにより近い分割ゲートへドレイン電位により近い電位でかつドレイン電位に応じて変化する電位を供給する手段をとる。

(もっと読む)

双方向素子および半導体装置

【課題】高耐圧でオン電圧を低くできる双方向素子および半導体装置を提供すること。

【解決手段】分割半導体領域にpオフセット領域5とその表面に第1、第2nソース領域9、10を形成することで、第1、第2nソース領域9、10の平面距離を短縮してセルの高密度化を図り、トレンチに沿って耐圧を維持させることで高耐圧化を図り、ゲート電極7の電圧を第1、第2nソース電極11、12より高くすることで、トレンチ側壁にチャネルを形成して、双方向へ電流が流れる高耐圧で低オン電圧の双方向LMOSFETとすることができる。

(もっと読む)

半導体装置

【課題】最小加工寸法がフィン幅となるFinFETの構造において、極めて制御が困難なリング形状の加工を不要として、加工ばらつきに起因する特性ばらつきの小さなユニットセルを提供する。

【解決手段】ユニットセルは、半導体基板1上に形成された開ループ構造のゲート電極Gと、前記ゲート電極Gの内方となる領域にフィン状に形成されたドレイン領域2と、前記ゲート電極Gの外方となる領域に形成されたフィン状のソース領域3とを有する。前記ドレイン領域2の上にはドレインコンタクト2aが形成され、前記ソース領域3上にはソースコンタクト3aが形成される。

(もっと読む)

電界効果トランジスタを形成するための方法および電界効果トランジスタ・デバイス

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路(1000)が、中央配置のドレイン拡散領域(1008)及び分散型SCR端子(1010)を備える1つのドレイン構造(1006)と、分散型ドレイン拡散領域(1016)及びSCR端子(1018)を備える別のドレイン構造(1012)とを含むSCRMOSトランジスタを有する。中央配置のドレイン拡散領域とソース拡散領域との間のMOSゲート(1022)がソース拡散領域へ短絡される。SCRMOSトランジスタを有する集積回路を形成するためのプロセスも開示される。  (もっと読む)

(もっと読む)

1 - 20 / 72

[ Back to top ]