Fターム[5F140BH21]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物材料 (430)

Fターム[5F140BH21]の下位に属するFターム

n、p型とならないもの (190)

Fターム[5F140BH21]に分類される特許

1 - 20 / 240

半導体装置、高電子移動度トランジスタ、および、複数のチャネルによりソースからドレインに電子を送るための方法

電界効果トランジスタ

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】耐圧を向上できる電界効果トランジスタを提供する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

(もっと読む)

電界効果トランジスタの製造方法および電界効果トランジスタ

【課題】ドーピング密度を増やすことなく、高濃度キャリア走行部を形成でき、高い移動度と低いオン抵抗を実現できる電界効果トランジスタの製造方法および電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタ1は、窒素ドープn型SiCドリフト層12のキャリア走行部14を挟むように形成されたソース13とドレイン15とを備える。ソース13とドレイン15は、エッチングによってキャリア走行部14に隣接して形成された段部16,17を有する。キャリア走行部14は、段部16,17の段差面16A,17Aに紫外光を照射することによって段部16,17から延びるように形成された積層欠陥部18を有する。積層欠陥部18は、3C‐SiCの結晶構造を持ち、量子井戸構造のようにふるまうことからキャリアがここに多数閉じ込められる。

(もっと読む)

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】結晶欠陥の発生を抑え、デバイスのリーク電流の発生、耐圧低下、しきい値電圧の継時変化、およびショートチャネル効果を抑制することが可能な半導体装置を提供すること。

【解決手段】単結晶AlNからなる基板を準備するステップと、前記単結晶AlNからなる基板の表面を酸素プラズマによって酸化し、単結晶AlNからなる基板上に酸化アルミニウムまたはアルミニウムオキシナイトライドからなる絶縁膜を形成するステップとを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、オン抵抗を低くしつつ、閾値電圧を高くする。

【解決手段】キャップ層400と障壁層300の界面、及びチャネル層200とバッファ層100の界面には圧縮歪が生じており、障壁層300とチャネル層200の界面には引張り歪が生じている。このため、キャップ層400と障壁層300の界面、並びにチャネル層200とバッファ層100の界面において、負の電荷が正の電荷よりも多くなっており、障壁層300とチャネル層200の界面において、正の電荷が負の電荷よりも多くなっている。チャネル層200は、第1層、第2層、及び第3層の積層構造を有している。第2層は、第1層及び第3層よりも電子親和力が大きい。

(もっと読む)

半導体装置の製造方法

【課題】ヒ素(As)を高濃度にドーピングした状態でエクステンション領域のエピタキシャル成長膜表面に凹凸を発生させることなく、平滑な面に形成することを可能とする。

【解決手段】半導体基板11上にゲート絶縁膜12を介してゲート電極13を備え、前記ゲート電極13の両側の前記半導体基板11上に形成された不純物を含有してなるエクステンション領域17、18を備えた半導体装置1であって、前記エクステンション領域17、18は、シリコンゲルマニウムにヒ素を含む状態でエピタキシャル成長されたエピタキシャル成長膜からなり、このエピタキシャル成長膜は、ヒ素をドーピングしながらシリコンとゲルマニウムとを前記半導体基板11上に選択的にエピタキシャル成長させて形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

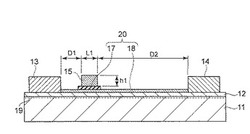

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

パルス列アニーリング方法および装置

【課題】基板の所望の領域上でアニーリングプロセスを実行するために使用される装置および方法を開示する。

【解決手段】1つの実施形態では、電磁エネルギのパルスはフラッシュランプまたはレーザ装置を使用して基板に送出される。パルスは約1nsecから約10msecの長さであってもよく、各パルスは基板材料を融解するのに必要なエネルギより少ないエネルギを有する。パルスの間隔は一般的に、各パルスにより与えられるエネルギを完全に放散させるのに十分な長である。このようにして、各パルスはマイクロアニーリング周期を終了する。パルスは1回で基板全体にまたは同時に基板の一部に送出されてもよい。

(もっと読む)

半導体デバイスおよび半導体デバイス製造方法

【課題】III族窒化物半導体では、p型不純物を高濃度にイオン注入すると、結晶品質が低下してしまう。結晶品質が低下するとオフ電流が増加して、電子デバイス特性が低下する可能性がある。このため、III族窒化物半導体では、p+層を形成することが困難であった。

【解決手段】III族窒化物半導体にドープされるとp型半導体になるp型不純物、および金属を有する合金からなる合金層と、合金層の下に接して形成され、III族窒化物半導体からなり、p型不純物が一部に拡散している半導体層と、合金層上に形成され、p型不純物の拡散係数が、半導体層より小さい拡散防止層と、を備える半導体デバイスを提供する。

(もっと読む)

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

高耐圧トランジスタ及びその製造方法

【課題】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法を提供する。

【解決手段】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法において、半導体基板の所定部位が酸化された第1絶縁膜パターン、及び第1絶縁膜パターンを少なくとも部分的に取り囲む第2絶縁膜パターンを形成する。基板上に導電性物質を蒸着して、第1端部は第1絶縁膜パターン上に位置し、第2端部は第2絶縁膜パターン上に位置するゲート電極を形成した後、基板表面の所定部位に不純物を注入してソース/ドレイン領域を形成する。ゲート電極のエッジ部分に集中される電界を緩和して高い降伏電圧を有するトランジスタを製造することができ、熱酸化膜パターンとCVD酸化膜パターンをゲート酸化膜として使用することで、MOSトランジスタにおいて電流特性及びON抵抗特性を改善することができる。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、窒化物系半導体装置を提供することを目的とする。

【解決手段】ドレイン電極26とゲート電極28との間に設けられたSBD金属電極30がAlGaN層20とショットキー接合されている。また、SBD金属電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、SBD金属電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、SBD金属電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

GaN−MISトランジスタ、GaN−IGBT、およびこれらの製造方法

【課題】オン抵抗を低減することができるGaN−MISトランジスタ、GaN−IGBT、およびこれらの製造方法を提供する。

【解決手段】ゲート電極(M)16とSiNゲート絶縁膜(I)13と半導体層(GaN)12とのMIS構造を有するGaN−MISトランジスタ150であって、半導体層は、オーミックコンタクト用n+GaN領域14が離間した2箇所に形成され、SiNゲート絶縁膜は、2箇所のオーミックコンタクト用n+GaN領域の基板反対側表面に熱CVD法により成膜されたSiN膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタや縦型FET等の縦型デバイスを、絶縁膜マスクを用いた選択成長による、ボトムアップ構造にするすることで、精密な制御を要求される工程を削減できる製造方法を提供する。

【解決手段】導電性基板20の第1主表面上に、第1絶縁膜32、金属膜42及び第2絶縁膜52を順次に形成する。次に、第1絶縁膜、金属膜及び第2絶縁膜の、中央領域の部分を除去することにより、導電性基板を露出する成長用開口部70を形成する。次に、成長用開口部内に、半導体成長部82,84を形成する。次に、第2絶縁膜の、中央領域の周囲の周辺領域内に設けられた引出電極領域の部分72を除去することにより、金属膜を露出する引出電極用開口部を形成する。次に、引出電極用開口部内72に、引出電極90を形成する。次に、半導体成長部上及び導電性基板の第2主表面上にオーミック電極92を形成する。

(もっと読む)

1 - 20 / 240

[ Back to top ]