Fターム[5F140BJ01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 単層 (1,329)

Fターム[5F140BJ01]に分類される特許

161 - 180 / 1,329

半導体装置、半導体チップ及び半導体装置の製造方法

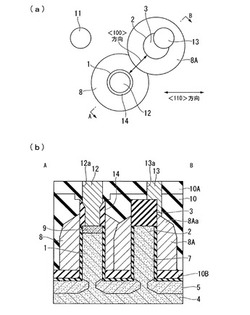

【課題】製造工程中にピラー径の変動が小さいピラー型MOSトランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板対して垂直に立設する第1のピラー及び第2のピラーの側面にゲート絶縁膜を介して形成されたゲート電極と、第1のピラーの先端部及び基端周囲領域に形成された上部拡散層及び下部拡散層と、を備え、第2のピラーのゲート電極と隣接する第1のピラーのゲート電極とは接続されており、第1のピラーのゲート電極には第2のピラーのゲート電極を介して電位が供給され、第1のピラーと、該第1のピラーに隣接する第2のピラーの少なくとも一部とは平面視して、第1のピラー及び第2のピラーの側面を構成する面のうち、熱酸化速度及び/又はエッチング速度が最大の面に対して45°の方向に沿って配置されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電体ゲート絶縁膜およびシリコン基板との界面を高品質化して、MISFETの特性向上を図る。

【解決手段】 シリコン基板11上にhigh−k膜21とゲート電極24を形成する半導体装置の製造方法において、high−k膜形成後にフッ素雰囲気でアニール処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細化が進んだトランジスタにおいて、他の問題を生じさせずに抵抗を低減する。

【解決手段】シリサイド層9は、ソース・ドレイン領域8の表層及びソース・ドレイン拡張領域6に形成されている。シリサイド層9は、半導体基板1に垂直かつゲート幅方向に対して平行な断面でみたときに、ソース・ドレイン領域8の中央部からチャネル領域に近づくにつれて半導体基板1の内側(図中下側)に近づいており、かつチャネル領域側の端部がソース・ドレイン拡張領域6に延在している。

(もっと読む)

半導体装置及びその製造方法

【課題】MIPS構造等のゲート電極と同時形成が可能であり且つ抵抗が高い抵抗素子を有する半導体装置及びその製造方法を提供する。

【解決手段】基板上に金属含有膜108及びポリシリコン膜109を順次形成する工程と、前記金属含有膜及び前記ポリシリコン膜を抵抗素子形状にパターニングする工程と、前記金属含有膜の少なくとも一部分を除去することにより、前記ポリシリコン膜の下に中空領域119を形成する工程とを備えている。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧で、特性の優れた半導体装置を提供する。

【解決手段】素子分離領域STIと、ウェルPWと、活性領域を横断するゲート電極Gと、ゲート電極の一方の側からゲート電極下方に入り込んで形成された低濃度ドレイン領域LDDと、ゲート電極の他方の側からゲート電極下方に入り込み、低濃度ドレイン領域とオーバーラップし、低濃度ドレイン領域より浅い、チャネル領域CHと、ゲート電極の他方の側に形成されたソース領域Snと、ゲート領域の一方の側に、ゲート電極から離間したドレイン領域Dnと、を有し、ゲート電極と高濃度ドレイン領域Dnとの間の中間領域の実効不純物濃度は、オーバーラップ領域の不純物濃度より高い。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ内に形成されたビット線の底面からのリーク電流を低減する。また、トレンチのアスペクト比を大きく増加させることなく、その後の工程でトレンチ内の空間に安定して成膜して、高アスペクト比による加工性の低下といった問題が生じない半導体装置を提供する。

【解決手段】半導体基板内にトレンチを形成する。このトレンチ内壁の底面上に第一の絶縁膜を形成する。また、トレンチ内壁の側面上に熱酸化により第一の絶縁膜よりも膜厚が薄い第二の絶縁膜を形成する。トレンチ内の第一の絶縁膜上に、ビット線を形成する。

(もっと読む)

イオン注入及び側方拡散による炭化シリコンパワーデバイスの自己整列的な製造方法

【課題】自己整列した浅い注入領域及び深い注入領域を形成し、浅い注入領域の低い拡散率を有するn型ドーパントを比較的固定すると共に、深い注入領域の高い拡散率を有するp型ドーパントを十分に拡散させ、良く制御されたチャネルを形成するpベース領域をn型ソースの周りに形成して横型炭化シリコンパワーデバイスを製造する。

【解決手段】炭化シリコン基板内にマスクの開口部を通してp型ドーパントをイオン注入して深いp型注入領域を形成する。マスクの同じ開口部を通してn型ドーパントをイオン注入して前記p型注入領域と比較して浅いn型注入領域を形成する。その後、前記深いp型注入領域を前記浅いn型注入領域を囲む炭化シリコン表面まで、該埋め込まれた深いp型注入領域を該浅いn型注入領域を通って炭化シリコン基板表面まで縦方向に拡散させることなく、側方拡散させるのに十分な温度及び時間でアニールする。

(もっと読む)

半導体素子

半導体素子(例えば、フリップチップ)は、介在層によってドレインコンタクトから分離されたサブストレートを含む。前記介在層を通じて延びる前記素子の動作時において、トレンチ状のフィードスルー要素を用いて、前記ドレインコンタクトおよび前記サブストレートを電気的に接続する。 (もっと読む)

高電子移動度トランジスタの構造、その構造を含んだデバイス及びその製造方法

【課題】MMICのSPDTスイッチなど、半導体デバイスとして用いるのに適したMOS−PHEMTの構造及びその製造方法を開示する。

【解決手段】MOS−PHEMT構造は、Al2O3、HfO2、La2O3及びZrO2からなる群から選ばれる材料からなるゲート誘電体層107を有することを特徴とし、これにより、このMOS−PHEMTの構造を含む、高周波スイッチデバイスなどの半導体構造が、直流電流の損失及び挿入損失の低下を防ぎ、隔絶性を向上させることができる。

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層上に第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、ソース電極およびドレイン電極の間の窒化物半導体積層体における、第1窒化物半導体層の一部および第2窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域上に形成された窒化物半導体膜と、リセス領域の内壁面、および第2窒化物半導体層の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを有し、第2窒化物半導体層は、第1窒化物半導体層に比べて広い禁制帯幅を有し、窒化物半導体膜の上面は、第1窒化物半導体層の上面よりも低いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの耐圧を高く保ちつつ、素子分離能力の低下を防ぐ。

【解決手段】基板102の一面のチャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162内部を埋め込むように形成されたゲート電極122を含むトランジスタにおいて、ソース領域112およびドレイン領域113の下方には、それぞれ第1のオフセット領域106および第2のオフセット領域107が形成される。ここで、第1のオフセット領域106および第2のオフセット領域107は、それぞれ、素子分離絶縁膜110と接する領域における下端が素子分離絶縁膜110の下端よりも上方に位置するように形成されるとともに、トレンチ162端部の下方にも形成されている。

(もっと読む)

半導体装置

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有する第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

金属ゲートとストレッサーを有するゲルマニウムフィンFET

【課題】金属ゲートとストレッサーを有するゲルマニウムフィンFETを提供する。

【解決手段】集積回路構造は、n型フィン電界効果トランジスタ(fin field effect transistor、FinFET)とp型FinFETからなる。n型FinFETは、基板上の第一ゲルマニウムフィン、第一ゲルマニウムフィンの上面と側壁上の第一ゲート誘電体、及び、第一ゲート誘電体上の第一ゲート電極からなる。p型FinFETは、基板上の第二ゲルマニウムフィン、第二ゲルマニウムフィンの上面と側壁上の第二ゲート誘電体、及び、第二ゲート誘電体上の第二ゲート電極からなる。第一ゲート電極と第二ゲート電極は、ゲルマニウムの固有エネルギーレベルに近い仕事関数を有する同一材料で形成される。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】複数のトレンチを含むトレンチゲート構造のトランジスタにおける特性ばらつきを低減する。

【解決手段】トレンチゲート構造を有するトランジスタを含む半導体装置100において、ゲート幅方向において、複数のトレンチ162は、両側方に形成された素子分離絶縁膜110とそれぞれ接して形成されたトレンチ162aおよびトレンチ162bを含み、トレンチ162aおよびトレンチ162bのゲート幅方向の幅が、これらの間に形成された他のトレンチ162cのゲート幅方向の幅以上となるように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】より高い耐熱性を有するシリサイド層を備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上にゲート絶縁膜4を介してゲート電極5を形成する工程と、半導体基板2上のゲート電極5の両側に、Ge含有領域8を形成する工程と、半導体基板2およびGe含有領域8のゲート電極5の両側の領域中に、ソース・ドレイン領域9を形成する工程と、Ge含有領域8上に、濃度5原子%以上のPdを含む金属シリサイドからなるシリサイド層11を形成する工程と、シリサイド層11を形成した後、半導体基板2に650〜750℃の熱処理を施す工程と、を含む。

(もっと読む)

半導体装置

【課題】駆動電力の高いフィン型のトランジスタを提供する。

【解決手段】所定の間隔で配置され、それぞれの中央部がチャネル領域、その両側部がソース/ドレイン領域となるフィン状の第1の半導体11層及び第2の半導体層11と、第1の半導体層11及び第2の半導体層11それぞれのチャネル領域の両側面にゲート絶縁膜12を介して形成されたゲート電極13と、第1の半導体層11のソース/ドレイン領域と第2の半導体層11のソース/ドレイン領域との間の溝を埋め込むように形成された絶縁膜19と、第1の半導体層11のソース/ドレイン領域及び第2の半導体層11のソース/ドレイン領域の絶縁膜19で覆われていない側面にそれぞれ形成されたシリサイド16とを備える。

(もっと読む)

埋め込みストレッサを有する高性能FETを形成するための方法および構造

【課題】 高性能の半導体構造およびかかる構造を製造する方法を提供する。

【解決手段】 半導体構造は、半導体基板12の上面14上に位置する、例えばFETのような少なくとも1つのゲート・スタック18を含む。構造は更に、少なくとも1つのゲート・スタックのチャネル40上にひずみを誘発する第1のエピタキシ半導体材料34を含む。第1のエピタキシ半導体材料は、少なくとも1つのゲート・スタックの対向側に存在する基板内の1対のくぼみ領域28の実質的に内部で少なくとも1つのゲート・スタックの設置場所に位置する。くぼみ領域の各々において第1のエピタキシ半導体材料の上面内に拡散拡張領域38が位置する。構造は更に、拡散拡張領域の上面上に位置する第2のエピタキシ半導体材料36を含む。第2のエピタキシ半導体材料は、第1のエピタキシ半導体材料よりも高いドーパント濃度を有する。

(もっと読む)

161 - 180 / 1,329

[ Back to top ]