Fターム[5F140BJ01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 単層 (1,329)

Fターム[5F140BJ01]に分類される特許

101 - 120 / 1,329

半導体装置の製造方法

【課題】ゲート電極上のキャップ膜が厚く、隣接するトランジスタ間の空間のアスペクト比が大きいトランジスタに、適切な濃度プロファイルを有するハロー領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】一実施の形態による半導体装置の製造方法は、基板上に第1および第2のゲート電極を形成する工程と、前記第1および第2のゲート電極下に第1および第2のハロー領域をそれぞれ形成する工程と、前記第1および第2の絶縁膜に底面および側面をそれぞれ覆われた第1および第2のキャップ膜を形成する工程と、を含む。前記第1のハロー領域は、第1の不純物を、前記第2の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。前記第2のハロー領域は、第2の不純物を、前記第1の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置の製造方法

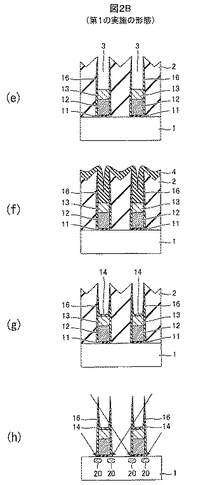

【課題】半導体装置の性能を向上させる。

【解決手段】イオン注入により半導体基板1にエクステンション領域EXを形成してから、ゲート電極GEの側壁上にサイドウォールスペーサSWを形成し、その後、イオン注入により半導体基板1にソース・ドレイン領域SDを形成する。サイドウォールスペーサSWを形成するには、半導体基板1上にゲート電極GEを覆うように絶縁膜6を形成してから、この絶縁膜6を異方性エッチングし、その後、半導体基板1上にゲート電極GEを覆うように絶縁膜7を形成してから、この絶縁膜7を異方性エッチングすることで、ゲート電極GEの側壁上に残存する絶縁膜6,7からなるサイドウォールスペーサSWを形成する。絶縁膜6のエッチング工程では、絶縁膜6をアンダーエッチングまたはジャストエッチングし、絶縁膜7のエッチング工程では、絶縁膜7をオーバーエッチングする。

(もっと読む)

電界効果トランジスタの製造方法

【課題】チャネル層をInAsから構成するヘテロ構造の電界効果トランジスタで、高速で安定した動作ができるようにする。

【解決手段】キャップ層105の表面を塩酸からなる処理液で処理する。処理液は、例えば、塩化水素の37質量%水溶液を、水で5倍(体積)に希釈したものである。次に、基板101を処理液中より引き上げ、直ちにキャップ層105の表面に付着している塩酸を除去する。この塩酸の除去では、水を用いることなく、例えば、キャップ層105の表面に窒素ガスを吹き付けることで付着している塩酸を除去する。

(もっと読む)

電界効果トランジスタ

【課題】チャネル層をInAsから構成するヘテロ構造の電界効果トランジスタで、高速で安定した動作ができるようにする。

【解決手段】第1障壁層102に形成されてAlGaSbに対して浅いアクセプタとなる不純物が導入された第1不純物導入領域110と、第2障壁層104に形成されてAlGaSbに対して浅いアクセプタとなる不純物が導入された第2不純物導入領域111とを備える。また、第1不純物導入領域110および第2不純物導入領域111は、チャネル層103の電子に不純物散乱を生じさせない範囲でチャネル層103より離間して形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極と半導体基板との間のショートの発生を抑制した上で、厚さが厚く、かつ均一な厚さとされたシリサイド層を形成可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜27を介して、ピラー26の側面26a,26bに設けられたゲート電極61,62と、ピラー26の上端26−1に形成されたシリサイド層38と、ゲート電極61,62を覆うと共に、ピラー26の側面を囲むように配置され、かつシリサイド層38の側面を露出する絶縁膜と、シリサイド層38の側面を覆うように設けられ、かつピラー26の上端26−1に含まれるシリコンをシリサイド化させる金属膜39と、シリサイド層38の下面38bと接触するように、ピラー26に形成された上部不純物拡散領域36と、シリサイド層38の上面38aに設けられたキャパシタ52と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】保護膜としてSiN膜が使用されている場合であっても、素子動作特性の変動を軽減することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置2は、ドレインドリフト領域12を有する半導体基板11と、ドレインドリフト領域12上に形成されたフィールド酸化膜17と、ゲート電極18と、中間絶縁膜17と、メタル層21,22と、これらを覆うSiN膜23と、SiN膜23上にO3−TEOSを用いたCVD法により形成され、カーボンを含有するPSG膜24とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル形成領域に印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させる半導体装置を提供する。

【解決手段】チャネル形成領域を有する半導体基板10上にゲート絶縁膜20が形成され、ゲート絶縁膜20の上層にゲート電極21が形成され、ゲート電極21の上層にチャネル形成領域に応力を印加する第1応力導入層22が形成されており、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部にソースドレイン領域13が形成されており、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に、チャネル形成領域に第1応力導入層22と異なる応力を印加する第2応力導入層26が形成されている構成とする。

(もっと読む)

多孔性絶縁体及び電界効果トランジスタ

【課題】例えば、チタン酸ストロンチウムを活性層とした電界効果トランジスタのゲート絶縁体としても使用することのできる、新規な絶縁体を提供することを目的とする。

【解決手段】絶縁性を示す材質中に直径5〜100nmである空孔を複数有し、全体の体積に対する前記空孔の占める体積の割合である空孔率が20体積%以上であり、前記空孔には水分が含まれ、前記空孔の体積に対する前記水分の占める体積の割合である水分占有率が23〜100体積%である多孔性絶縁体を使用する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性に優れた半導体装置が得られる製造方法を提供する。

【解決手段】半導体装置の製造方法は、p型電界効果トランジスタおよびn型電界効果トランジスタを備える半導体装置の製造方法であって、基板上に、界面絶縁層および高誘電率層をこの順で形成する工程と、高誘電率層上に、犠牲層のパターンを形成する工程と、犠牲層が形成されている第1の領域の高誘電率層上および犠牲層が形成されていない第2の領域の高誘電率層上に、金属元素を含む金属含有膜を形成する工程と、熱処理を行うことにより、第2の領域における界面絶縁層と高誘電率層との界面に金属元素を導入する工程と、犠牲層をウエットエッチングにより除去する工程と、を含み、除去する工程において、犠牲層は、高誘電率層よりもエッチングされやすい。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタに係る半導体装置の高速動作を可能とする。

【解決手段】P型ウエル層3の表面に形成された複数の素子分離膜4の中央部に開口溝5を形成する。開口溝5の側壁から開口溝5の内側に向かってゲート絶縁膜6を介して延在するゲート電極7を形成する。ゲート電極7をマスクにしてセルフアラインでボロンの斜めイオン注入により開口溝5内のP型ウエル層3にP型ボディ層8を形成する。

ゲート電極7をマスクに砒素のイオン注入によりP型ボディ層8にN+型ソース層9を、同時に2つの素子分離膜4間のP型ウエル層3にN+型ドレイン層10を形成する。素子分離膜4の下方のP型ウエル層3にP型ボディ層8の端部からN+型ドレイン層10に延在するN−型ドリフト層を形成する。この際、P型ボディ層8の端部から開口溝5の側壁下部までの領域AのN−型ドレイン層11の幅をできるだけ小さくなるよう制御する。

(もっと読む)

半導体装置の製造方法、及び、半導体装置

【課題】CMOS回路の閾値を簡易なプロセスで効率よく制御して、信頼性の高い半導体装置を作製する。

【解決手段】下地ゲート絶縁膜を形成し、下地ゲート絶縁膜上に選択的にマスク膜を形成し、下地ゲート絶縁膜、及び、マスク膜上に第1の金属元素を含む第1のキャップ膜を形成し、nMOSトランジスタ領域の下地ゲート絶縁膜に第1の金属元素を拡散させ、マスク膜、及び、第1のキャップ膜を選択的に除去し、第1の金属元素が拡散したnMOSトランジスタ領域の下地ゲート絶縁膜、及び、pMOSトランジスタ領域の下地ゲート絶縁膜上に第2の金属元素を含む第2のキャップ膜を形成し、下地ゲート絶縁膜に第2の金属元素を拡散させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上部拡散層が平面積の狭いものであっても、上部拡散層および上部拡散層上に設けられた配線とのコンタクト抵抗を大きくすることなく、上部拡散層と配線とを接続できる半導体装置を提供する。

【解決手段】柱状半導体5と、柱状半導体5上に形成された上部拡散層15と、上部拡散層15上に形成された接続プラグ24とを備え、上部拡散層15が、平面視島状の複数の島状部を有するものであり、接続プラグ24が、導電材料からなり、前記複数の島状部から選ばれる第1島状部と前記第1島状部に隣接する第2島状部との間の隙間を跨って、前記第1島状部の上面の少なくとも一部から前記第2島状部の上面の少なくとも一部まで連続して配置されている半導体装置とする。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加するシリコン混晶層を活性領域に設けた半導体装置において、電流駆動能力の向上とリーク電流の低下と図れるようにする。

【解決手段】半導体装置は、シリコンからなる半導体基板10に形成され、周囲を素子分離領域11により囲まれてなる第2の活性領域10bと、該第2の活性領域10b及び素子分離領域11の上に、ゲート絶縁膜13を介在させて形成されたゲート電極14とを有している。第2の活性領域10bには、ゲート電極14の両側方の領域が掘り込まれてなるリセス領域19cにp型シリコン混晶層21が形成されており、該p型シリコン混晶層21における素子分離領域11と接触する接触位置の上端21bは、第2の活性領域10bの上面におけるゲート絶縁膜13の下側部分よりも低い。

(もっと読む)

エッチング方法及び装置

【課題】基板に形成された絶縁膜をエッチングするとき、絶縁膜の下地に酸素プラズマの悪影響が生ずるのを防止できるエッチング方法を提供する

【解決手段】本発明のエッチング方法は、絶縁膜222をプラズマ化させた処理ガスに晒し、絶縁膜222を厚さ方向に途中までエッチングする第一のエッチング工程と、第一のエッチング工程の終了後に残存する絶縁膜222を酸素プラズマに晒し、残存する絶縁膜222の表面に堆積した堆積物を除去する堆積物除去工程と、残存する絶縁膜222をプラズマ化させた処理ガスに晒し、残存する絶縁膜222をエッチングする第二のエッチング工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置においてショートを生じることを防ぐことができる、半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板に所定の間隔で設けられた一対の不純物拡散領域と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側面及び前記ゲート絶縁膜の両側面を覆う、絶縁性の一対のサイドウォールスペーサーと、ゲート電極の上面に形成されたシリサイド金属膜と、を備える。サイドウォールスペーサーは、上下に積み重ねられた下部サイドウォールスペーサーと上部サイドウォールスペーサーとを有する。

(もっと読む)

双方向素子および半導体装置

【課題】高耐圧でオン電圧を低くできる双方向素子および半導体装置を提供すること。

【解決手段】分割半導体領域にpオフセット領域5とその表面に第1、第2nソース領域9、10を形成することで、第1、第2nソース領域9、10の平面距離を短縮してセルの高密度化を図り、トレンチに沿って耐圧を維持させることで高耐圧化を図り、ゲート電極7の電圧を第1、第2nソース電極11、12より高くすることで、トレンチ側壁にチャネルを形成して、双方向へ電流が流れる高耐圧で低オン電圧の双方向LMOSFETとすることができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

半導体装置およびその製造方法

【課題】メモリセル領域のトランジスタにおけるソース/ドレイン電極上の半導体層同士の接触による短絡を防止しつつ、周辺回路領域のトランジスタにおけるせり上げソース/ドレイン領域を含むソース/ドレイン電極の高濃度不純物層の接合深さの均一性を図り、短チャネル効果を抑制する。

【解決手段】メモリセル領域における隣接するトランジスタ間で半導体層同士が接触しない膜厚にエピタキシャル成長させ、その際、周辺回路領域の素子分離2のみを後退させて露出した基板面からもエピタキシャル成長半導体層10を成長させることで、周辺回路領域の半導体層のファセットFが活性領域外に形成されるようにし、その後、周辺回路領域に高濃度不純物層11用のイオン注入を行う。

(もっと読む)

101 - 120 / 1,329

[ Back to top ]