Fターム[5F140BJ01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 単層 (1,329)

Fターム[5F140BJ01]に分類される特許

201 - 220 / 1,329

電界効果トランジスタ及びその製造方法

【課題】高品質な特性を有する電界効果トランジスタ及びその方法を提供する。

【解決手段】素子分離領域106間のソース/ドレイン領域114、及びポケット領域116を含んでいる半導体基板102と、素子分離領域間の半導体基板の上面のトレンチ110内にあって、(100)面を有する底面及び上面と、2つ以上の平面を有する側面とを有するシリコンゲルマニウム層112と、ゲート絶縁層120、ゲート電極122、及びサイドスペーサ128を含むシリコンゲルマニウム層上のゲート構造と、ゲート構造によって覆われていないシリコンゲルマニウム層及び半導体基板の上部分上のメタルシリサイド124とを備え、シリコンゲルマニウム層は、チャネル長方向において、ゲート構造の下で側面を有していない。

(もっと読む)

半導体装置およびその製造方法

【課題】NMISトランジスタとPMISトランジスタの閾値電圧を同時に低減できる半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板10に形成された第1の活性領域10a上に高誘電体を含む第1のゲート絶縁膜17aと、金属材料を含む第1のゲート電極18aとを形成し、基板10に形成された第2の活性領域10b上に高誘電体を含む第2のゲート絶縁膜17bと、金属材料を含む第2のゲート電極18bとを形成する工程と、第1のゲート絶縁膜17aの端部と第2のゲート絶縁膜17bの端部とに負の固定電荷を導入する工程と、第1のゲート絶縁膜17aの端部を除去する工程とを備えている。

(もっと読む)

半導体装置の製造方法及びスパッタリング装置

【課題】半導体基板にシリサイド形成用の金属膜を形成する時に、ゲート絶縁膜にダメージが加わることを抑制する。

【解決手段】このスパッタリング装置は、チャンバ101、ウェハステージ102、リングチャック104、金属ターゲット105、防着シールド107、マグネット108、コリメータ109、並びに直流電源110,120を備えている。直流電源110は、コリメータ109に負電圧のみを印加するために設けられている。コリメータ109に印加される負電圧は、金属ターゲット105に印加される電圧より低電圧、例えば−70V以上−50V以下である。

(もっと読む)

不純物活性化方法、半導体装置の製造方法

【課題】低いシート抵抗を得る不純物活性化方法、および、ソース・ドレイン拡張部を均一な深さで再現性よく形成する製造方法を提供。

【解決手段】半導体基板21において半導体基板21よりも不純物濃度が高いボロンイオン注入層43が形成されており、ボロンイオン注入層43にパルス幅が10〜1000フェムト秒のパルスレーザー光を照射して、ボロンイオン注入層43を活性化させる。パルスレーザー光におけるパルス幅、レーザーフルーエンスおよび照射パルス数を含む照射条件を変更することにより、パルスレーザー光照射後のボロンイオン注入層43のシート抵抗を制御する。

(もっと読む)

半導体素子およびその製造方法

【課題】半導体素子の低オン抵抗化を実現し、全体の製造工程数を低減する半導体素子およびその製造方法を提供すること。

【解決手段】ソース・ドレイン領域を形成する際のイオン注入時に、低耐圧横型トレンチMOSFETでは、ドレイン形成用の開口部がトレンチ側壁から離れ、ソース形成用の開口部がトレンチ側壁に達し、トレンチ横型パワーMOSFETでは、ソース形成用の開口部がトレンチ側壁から離れ、ドレイン形成用の開口部がトレンチ側壁に達するパターンのマスクを用いる。このマスクを用いて、高ドーズ量および低加速電圧で行うイオン注入と、低ドーズ量および高加速電圧で行うイオン注入を連続して行うことによって、低耐圧横型トレンチMOSFETのLDD領域と、トレンチ横型パワーMOSFETのLDD領域とを同時に形成する。

(もっと読む)

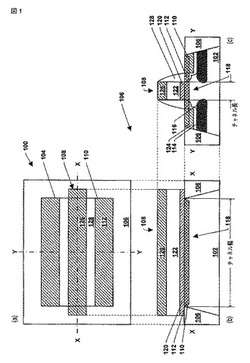

半導体装置

【課題】長い直線状のトレンチ1内に、ゲート絶縁膜17を介して第1ゲート電極2等を有するTDMOSトランジスタについて、増大するゲート抵抗と寄生容量に基づくゲート遅延の問題を、ゲート絶縁膜17に損傷を与えることなく改善する。

【解決手段】トレンチ1の側壁に、第1ゲート電極2等の材料となるポリシリコン膜22の膜厚の2倍未満の幅と奥行きからなるトレンチ凸部1aを形成する。トレンチ凸部1aはポリシリコン膜22で埋め込まれるのでその表面に形成された層間絶縁膜19に、トレンチ凸部1a部分のポリシリコンのみが露出する第1ゲートコンタクト4等を形成する。該第1ゲートコンタクト4等と接続する第1ゲート配線電極G1等を一定間隔の元、複数本形成する。

(もっと読む)

半導体装置の製造方法

【課題】後続の工程に伴う埋め込みゲートの酸化を防止し、ビットラインコンタクト及びストレージノードコンタクトと基板との間のコンタクト面積を増加させ、コンタクト抵抗を低減し、ビットラインコンタクト及びストレージノードコンタクトと埋め込みゲートとの間のGIDLを低減し、自己整合コンタクト不良を防止することのできる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板の全面にプラグ導電膜を形成するステップと、前記プラグ導電膜をエッチングしてランディングプラグを形成するステップと、前記ランディングプラグ間の基板をエッチングしてトレンチを形成するステップと、前記トレンチの表面上にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上に前記トレンチの一部を埋め込む埋め込みゲートを形成するステップと、を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体絶縁膜及びメタルゲート電極を有する半導体装置において、高仕事関数を得ると共にNBTI信頼性劣化を低減する。

【解決手段】半導体装置100において、基板101上に、高誘電体ゲート絶縁膜109を介してメタルゲート電極110が形成されている。高誘電体ゲート絶縁膜109とメタルゲート電極110との界面におけるメタルゲート電極110の側に、ハロゲン元素が偏析している。

(もっと読む)

半導体装置及びその製造方法

【課題】pMOSトランジスタにcSiGeとeSiGeを適用し、且つゲート絶縁膜におけるダメージ発生を防止でき、素子特性の向上及びしきい値制御性の向上をはかる。

【解決手段】pMOSトランジスタのチャネル部及びソース・ドレイン領域にSiGeを用いた半導体装置において、Si基板202上の一部に形成され、pMOSトランジスタのチャネルとなる第1のSiGe層205と、第1のSiGe層205上にゲート絶縁膜206を介して形成されたゲート電極208と、pMOSトランジスタのソース・ドレイン領域に埋め込み形成され、且つチャネル側の端部が基板表面よりも深い位置でチャネル側に突出するように形成された第2のSiGe層214と、第1のSiGe層205と第2のSiGe層214とを分離するように、基板の表面部でSiGe層205,214間に挿入されたSi層222とを備えた。

(もっと読む)

半導体装置の製造方法

【課題】チャネルに大きな歪を生じさせることができ、制御を容易に行うことができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、絶縁膜3、多結晶シリコン膜4及びアモルファスシリコン膜5を含む積層体を、ゲート電極の平面形状に形成する。多結晶シリコン膜4及びアモルファスシリコン膜5の側方にサイドウォール6を形成する。サイドウォール6をマスクとして半導体基板1の表面にp型不純物を導入して不純物導入領域7を形成する。サイドウォール6をマスクとして不純物導入領域7の表面に溝8を形成する。溝8内にSiGe層9を選択成長させる。アモルファスシリコン膜5を選択的に除去して、多結晶シリコン膜4を露出する。多結晶シリコン膜4上に導電層11を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチゲート構造を有するトランジスタにおいて、サブスレッショルド特性を良好にする。

【解決手段】半導体装置100は、第1導電型のソース領域112およびドレイン領域113、これらの間に第2導電型のチャネル領域108が形成された基板102と、チャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162を埋め込むように形成されたゲート電極122とを有するトランジスタを含む。チャネル領域108において、基板102表面およびトレンチ162の底部には、それぞれ第2の高濃度領域132および第1の高濃度領域130が形成されており、第2導電型の不純物濃度がトレンチ162側方における第2導電型の不純物濃度よりも高くなっている。また、第1の高濃度領域130の第2導電型の不純物濃度が第2の高濃度領域132の第2導電型の不純物濃度以上である。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域にエピタキシャル結晶を含み、エピタキシャル結晶上の金属シリサイドに起因する接合リークの発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、ファセット面13fを有するエピタキシャル結晶層13を有するMISFET10と、MISFET10を他の素子から電気的に分離し、上層3aのゲート電極12側の端部の水平方向の位置が下層3bのそれよりもゲート電極12に近く、上層3aの一部がファセット面13fに接する素子分離絶縁膜3と、エピタキシャル結晶層13の上面、およびファセット面13fの上層3aとの接触部よりも上側の領域に形成されたシリサイド層18と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】High-k/metalゲート電極構造において各極性のFETに要求される仕事関数値を実現する。

【解決手段】第1の領域と第2の領域とを有する半導体基板101の上にゲート絶縁膜103を形成する。次に、ゲート絶縁膜103の上に第1の金属窒化膜105を堆積する。次に、第1の金属窒化膜105における第2の領域に位置する部分を除去することにより、ゲート絶縁膜103における第2の領域に位置する部分を露出させる。次に、ゲート絶縁膜103における第2の領域に位置する部分の上に、第1の金属窒化膜105と同じ金属窒化物からなる第2の金属窒化膜107を形成する。

(もっと読む)

電磁気素子用絶縁膜及び電界効果素子

【課題】リーク電流を増大させることなく薄膜化が可能であり、素子を微細化することができ、しかも、界面準位に起因する動作の不安定化を生じるおそれが少ない電磁気素子用絶縁膜、及び、このような電磁気素子用絶縁膜を用いた電界効果素子を提供すること。

【解決手段】12(CaxSr1-x)O・7Al2O3(0≦x≦1)で表される組成を有し、アモルファス構造を備えた電磁気素子用絶縁膜。半導体Aと、半導体A上に形成されたソース電極S及びドレイン電極Dと、ソース電極S−ドレイン電極D間の通電方向に対して垂直方向に電界を印加するためのゲート電極Gと、半導体Aとゲート電極Gとの間に形成されたゲート絶縁膜Bとを備えた電界効果素子10。ゲート絶縁膜Bは、本発明に係る電磁気素子用絶縁膜からなる。

(もっと読む)

歪み検出素子

【課題】ゲート電極、ソース電極、およびドレイン電極を備えたトランジスタ型の歪み検出素子であって、金属製歪みゲージよりも格段に優れた検出感度を有する歪み検出素子の提供。

【解決手段】ゲート電極と、ソース電極と、ドレイン電極と、チャネルが形成される圧電材料からなる層と、を備えた歪み検出素子であって、(a)上記ゲート電極の長さが2μmより大きいこと、(b)上記ゲート電極の幅が1mmより小さいこと、(c)上記ゲート電極と上記ソース電極の距離と、上記ゲート電極と上記ドレイン電極の距離との和が13μmより大きいこと、の3条件のうち少なくともいずれか1つの条件が成立していることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】閾値電圧が相対的に高い半導体装置のチャネル領域における不純物濃度を閾値電圧が相対的に低い半導体装置のチャネル領域における不純物濃度よりも高くすると、閾値電圧が相対的に高い半導体装置の駆動力の低下を招来する虞があった。

【解決手段】半導体装置は、第1のトランジスタと第2のトランジスタとを備えている。第1のトランジスタは、第1のチャネル領域3aと、第1のゲート絶縁膜4aと、第1のゲート電極5aと、第1のエクステンション領域8aとを有している。第2のトランジスタは、第1のトランジスタよりも高い閾値電圧を有しており、第2のチャネル領域3bと、第2のゲート絶縁膜4bと、第2のゲート電極5bと、第2のエクステンション領域8bとを有している。第2のエクステンション領域8bは浅接合化不純物を含んでおり、第2のエクステンション領域8bの接合深さは第1のエクステンション領域8aの接合深さよりも浅い。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】p型ソースドレイン領域内にシリコン混晶層が形成されていると、N型MISトランジスタのキャリア移動度が低下する虞があった。

【解決手段】活性領域10aと活性領域10bとが素子分離領域11により分離されており、活性領域10a上には第1導電型の第1のトランジスタが設けられており、活性領域10b上には第2導電型の第2のトランジスタが設けられている。活性領域10b内には、第1の応力を有するシリコン混晶層21が設けられている。素子分離領域11のうち活性領域10aと活性領域10bとで挟まれた部分の上面には凹部22が設けられている。凹部23内には応力絶縁膜24が設けられており、応力絶縁膜24は第1の応力とは反対方向の第2の応力を有する。

(もっと読む)

半導体記憶装置

【課題】縦型トランジスタSGTで構成されたCMOS型6T−SRAMにおいて、小さいSRAMセル面積と安定した動作マージンを実現する。

【解決手段】6個のMOSトランジスタを用いて構成されたスタティック型メモリセルにおいて、前記メモリセルを構成するMOSトランジスタは、基板上に形成され、ドレイン、ゲート、ソースが垂直方向に配置され、ゲートが柱状半導体層を取り囲む構造を有し、前記基板は第1の導電型を持つ第1の活性領域と第2の導電型を持つ第2の活性領域からなり、それらが基板表面に形成されたシリサイド層を通して互いに接続されることにより小さい面積のSRAMセルを実現する。また、基板上に配置される第1のウェルと同一の導電型を持つドレイン拡散層のそれぞれを第1のウェルと反対の導電型を持ち、第1のウェルより浅い第2のウェル及び第3のウェルで囲むことにより、基板へのリークを抑制する。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTの増大及びキャリア移動度の低下を抑制しつつ、半導体基板表面に形成されている酸化膜と高誘電率絶縁膜との界面に、しきい値電圧を低減する電気双極子を形成可能な金属を添加する。

【解決手段】半導体基板100上にゲート絶縁膜140を介してゲート電極150が形成されている。ゲート絶縁膜140は、酸素含有絶縁膜101と、第1の金属を含む高誘電率絶縁膜102とを有する。高誘電率絶縁膜102は、第1の金属とは異なる第2の金属をさらに含む。高誘電率絶縁膜102における第2の金属の組成比が最大になる位置は、高誘電率絶縁膜102と酸素含有絶縁膜101との界面及び高誘電率絶縁膜102とゲート電極150との界面のそれぞれから離れている。

(もっと読む)

201 - 220 / 1,329

[ Back to top ]