Fターム[5F140BK12]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域の形成 (4,176) | 不純物の導入 (3,397)

Fターム[5F140BK12]の下位に属するFターム

Fターム[5F140BK12]に分類される特許

121 - 140 / 146

半導体装置およびその製造方法

【課題】 光の照射をうけても、その特性が変動することのない半導体装置およびその製造方法を提供する。

【解決手段】 本発明の半導体装置は、半導体層10と、

前記半導体層10に設けられた絶縁ゲート電界効果型トランジスタ20と、

前記絶縁ゲート電界効果型トランジスタ20の上方に設けられたエッチングストッパ膜32と、

前記エッチングストッパ膜32の上方に設けられた層間絶縁層34と、を含み、

前記絶縁ゲート電界効果型トランジスタ20は、

前記半導体層10の上方に設けられたゲート絶縁層22と、

前記ゲート絶縁層22の上方に設けられたゲート電極24と、

前記半導体層10に設けられたソース領域またはドレイン領域となる不純物領域28と、を含み、

前記ゲート絶縁層22の外側であって、該ゲート絶縁層22と前記不純物領域28とに挟まれた位置以外の領域の上方には前記エッチングストッパ膜32が除去されてなる除去領域34が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】 歪みSOI基板上に形成したpチャネルMOSトランジスタにおいて、チャネル領域に効率よく引張り応力を印加する。

【解決手段】 下層に無歪みSiGe混晶層を有する歪みSiチャネル層上にpチャネルMOSトランジスタを形成する際に、チャネル領域の両側に、無歪みSiGe混晶層からエピタキシャルにSiGe混晶領域を成長させ、前記歪みSiチャネル層をかかるSiGe混晶層領域に格子整合させることにより、歪みSiチャネル層中における応力緩和を阻止し、効率的な応力印加を実現する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】熱酸化膜と半導体基板の界面で生じる応力を抑制することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板1に溝1aを形成する工程と、溝1aの内面に位置する半導体基板1に、フッ素を導入してフッ素含有層1bを形成する工程と、溝1aの側壁及び底面に、熱酸化膜2aを形成する工程と、溝1aに絶縁膜2を埋め込む工程とを具備する。熱酸化膜2aは、フッ素を含んでいるため、イオン結合性が高くなり、従来と比べて柔軟性が増す。このため、熱酸化膜と半導体基板の界面において、応力の発生が抑制される。

(もっと読む)

絶縁ゲート電界効果トランジスタの製造方法および絶縁ゲート電界効果トランジスタ

【課題】ゲート長の短縮に対応して最適な接合深さのエクステンション部を形成できなくなってきている。

【解決手段】ゲートスタック7と側壁絶縁膜9からなる所定の幅のスペーサをマスクとする不純物のイオン注入と活性化アニールにより、2つのソース・ドレイン領域10をPウェル3に形成する。側壁絶縁膜9を除去し、これより薄い隔壁絶縁膜11を形成することによって、このスペーサの幅方向両側を後退させる。これによりスペーサのエッジと2つのソース・ドレイン領域10のエッジとを幅方向両側で離す。この状態で、後退したスペーサの幅方向両側に露出し2つのソース・ドレイン領域10を含むウェル領域に選択的なエピタキシャル成長により半導体材料を成長させ、後退したスペーサにより分離する2つのエクステンション部12を形成する。この製法においては、イオン注入の活性化アニールによりエクステンション部12内の不純物がPウェル3内に熱拡散しない。

(もっと読む)

階段状ソース/ドレイン領域を有するデバイス

【課題】階段状ソース/ドレイン領域を有するトランジスタを提供する。

【解決手段】階段状領域を設けることによって、リーク電流を最小限に留めると同時にチャネル領域のひずみを大きくするとしてもよい。このような階段状領域の形成は、基板内に2種類のリセスを形成して階段状のリセスとし、このリセス内にソース/ドレイン領域を形成することによって実現するとしてもよい。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果によるリーク電流の低減に優れた半導体装置およびその製造方法を提供する。

【解決手段】単結晶半導体基板上に形成された電界効果トランジスタの作成過程において、エクステンション領域を形成するために不純物を導入するとともに、単結晶格子を崩してアモルファス化させる。または、不純物および原子量の大きい元素を導入することによって、単結晶格子を崩してアモルファス化させる。そして、パルス幅が1fs以上10ps以下、かつ波長が370nm以上640nm以下のレーザビームを照射することにより、アモルファス化した部分のみを選択的に活性化させ、エクステンション領域を20nm以下の厚さで形成する。

(もっと読む)

半導体装置の製造方法

【課題】 エッジラフネスを解消してパターンを形成する。

【解決手段】 基板上に、被加工膜を形成形成し、第1マスクの材料膜である第1材料膜を形成する。そして、第1材料膜をエッチングして、第1マスクを形成する。更に、第1マスク表面を含む基板全面に、第2マスクの材料膜である第2材料膜を形成した後、第1マスクの側面に第2材料膜を残すようにして、第2材料膜をエッチングして、第2マスクを形成する。その後、第1マスク及び第2マスクをマスクとして、被加工膜をエッチングしてパターンを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、CMOSトランジスタにおいて、nチャネル型トランジスタとpチャネル型トランジスタの両方のオン電流を更に向上させて、かつ製造工程の効率が向上する製造方法を提供する。

【解決手段】nチャネル型トランジスタは、不純物領域と、ゲート酸化膜、ゲート電極およびゲート電極側壁絶縁膜からなる第1のゲート積層体と、半導体基板の表面および前記第1のゲート積層体を覆う引張応力を有する第1の応力制御膜とを備え、前記半導体基板の第2の領域に配置されてなるpチャネル型トランジスタは、不純物領域と、ゲート酸化膜およびゲート電極からなりゲート電極側壁絶縁膜を有していない第2のゲート積層体と、半導体基板の表面および前記第2のゲート積層体を覆う圧縮応力を有する第2の応力制御膜とを備えていることを特徴とする半導体装置が提供される。

(もっと読む)

電界効果トランジスタ

【課題】短チャネル化の限界に関する指針を明確とし、高いオン/オフ比と高速動作の両方を満たすことができる構成の電界効果トランジスタを提供することである。

【解決手段】電界効果トランジスタは、チャネル長を隔て活性層4に接して形成されたソース電極2とドレイン電極3、及びソース電極2とドレイン電極3の間に形成されたゲート電極1を有し、チャネル長がLμmで、かつ活性層4のうちでソース−ドレイン間の距離が最短となるように電流の流れる領域の厚さがdnmである。所望のオン/オフ比をxとするとき、Lとdは下記の条件を満たす。 (もっと読む)

(もっと読む)

半導体素子及びその製造方法

【課題】接合漏洩電流とキャパシタンスを低減させ短チャンネル効果を改善して素子の特性を向上させる。

【解決手段】本発明に係る半導体素子及びその製造方法は、ソース/ドレーン領域のうちいずれか一つとチャンネル領域の一部は半導体基板の上部に形成された埋込酸化膜の上部に備えられ、ソース/ドレーン領域のうち他の一つとチャンネル領域の残りは半導体基板の上部に形成されたSiエピタキシャル層の上部に備えられる。

(もっと読む)

深く炭素がドーピングされた領域並びに隆起したドナーがドーピングされたソース及びドレインを特徴とする歪みnMOSトランジスタ

本発明に係る複数の実施例は、炭素がドーピングされた領域、及び隆起したソース/ドレイン領域を有することで、nMOSトランジスタチャネル中に引っ張り応力を供する。

(もっと読む)

(もっと読む)

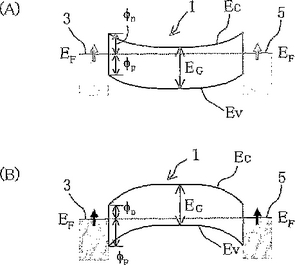

スピン依存伝達特性を有する電界効果トランジスタ及びそれを用いた不揮発性メモリ

ゲート電圧VGSの印加によって、強磁性ソースにおける金属的スピンバンドによるショットキー障壁幅が減少し、この金属的スピンバンドからのアップスピン電子がチャネル領域にトンネル注入される。このとき強磁性ソース3aの半導体的スピンバンドによるエネルギー障壁により非磁性コンタクト3bからダウンスピン電子は注入されない。すなわち、強磁性ソース3aからはチャネル層へアップスピン電子のみが注入される。強磁性ソース3aと強磁性ドレイン5aとが平行磁化の場合では、アップスピン電子は強磁性ドレインの金属的スピンバンドを伝導してドレイン電流となるが、反平行磁化を持つ場合では、アップスピン電子は強磁性ドレイン5aにおける半導体的スピンバンドによる高さΔEcのエネルギー障壁よって強磁性ドレイン5aを伝導することができない。 上記動作原理のMISFETに基づき、高性能・高集積密度の不揮発性メモリを構成することができる。  (もっと読む)

(もっと読む)

水素化ホウ素クラスターイオンの注入によるイオン注入装置及び半導体製造方法

【課題】 イオン化水素化ホウ素分子から形成されたイオンビームの注入によってP型ドーピングが達成される半導体製造法を提供する。

【解決手段】 イオン化された水素化ホウ素分子クラスターがP型トランジスタ構造を形成するために注入される、イオン注入装置及び半導体素子を製造する方法。例えば、相補型金属酸化膜半導体(CMOS)素子の製造において、このクラスターは、ソース及びドレーン構造及びポリゲートに対してP型ドーピングを提供するために注入され、これらのドーピング段階は、PMOSトランジスタの形成に極めて重要である。分子クラスターイオンは、化学形態BnHx+及びBnHx-を有し、ここで、10<n<100及び0≦x≦n+4である。  (もっと読む)

(もっと読む)

エンハンスメントモード金属酸化膜半導体電界効果トランジスタ及びその形成方法

注入フリーエンハンスメントモード金属酸化膜半導体電界効果トランジスタ(EMOSFET)を提供する。EMOSFETは、III−V化合物半導体基板と、III−V化合物半導体基板上のエピタキシャル層構造とを有する。エピタキシャル材料層は、チャネル層と、少なくとも1つのドープ層とを有する。ゲート酸化膜層は、エピタキシャル層構造の上にある。EMOSFETは、更に、ゲート酸化膜層上の金属ゲート電極と、エピタキシャル層構造上のソース及びドレイン・オーミックコンタクトと、を含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 High−k膜を用いたMISFETの電子移動度および正孔移動度を共に増加させ高性能の相補型MISFETを形成する。

【解決手段】 シリコン基板1の表面部にpウェル層2およびnウェル層3が形成され、素子分離領域4により区画されたnチャネルMISFETには、窒素添加のないnチャネル界面層5、窒素添加のないnチャネル高誘電体ゲート絶縁膜6およびnチャネルゲート電極7が形成されている。そして、n型ソース・ドレイン拡散層8が設けられている。これに対して、pチャネルMISFETでは、窒素添加のpチャネル界面層9、窒素添加のpチャネル高誘電体ゲート絶縁膜10およびpチャネルゲート電極11が形成されている。そして、p型ソース・ドレイン拡散層12が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】導通時における駆動力を向上させる。

【解決手段】所定の開口を有するマスク層を用いて、基板1とドレイン領域2からなる半導体基体の一主面側に所定の溝15を形成する工程と、少なくとも溝15の側壁に接して、該溝15からはみ出すように埋め込み領域11を形成する工程と、半導体基体並びに埋め込み領域11に接するようにヘテロ半導体層30を形成する工程と、ヘテロ半導体層30をパターニングし、ヘテロ半導体領域3を形成する工程とを含む。

(もっと読む)

センサおよびその製造方法

【課題】高感度の検出を可能にするEFT式バイオセンサの提供。

【解決手段】本発明のバイオセンサは、半導体基板にソース領域、ドレイン領域およびゲート領域を備えるように構成された電界効果トランジスタ式センサであり、メソ細孔を有し且つ該メソ細孔の壁面に酸化スズの微結晶を含むように構成された多孔質体を該ゲート領域に備え、且つ、該多孔質体がX線回折分析において1nm以上の構造周期性に対応する角度領域に少なくとも一つの回折ピークを有する。

(もっと読む)

高性能なサブ0.1マイクロメートルトランジスタ用のソース/ドレイン構造

【課題】チャネルパンチスルーおよび短チャネル効果が低減された、高性能な短チャネル長のトランジスタ構造を提供すること。

【解決手段】本発明によるトランジスタ構造(10)は、基板内に形成されたp型ウェル12を備える。ゲート構造(14)は、ソース領域(18)とドレイン領域(20)との間に挿入されたチャネル領域(16)上に形成される。ゲート構造(14)は、ゲート誘電体24上にゲート電極(22)と、ゲート(22)の面に沿った側壁26を有する。ソース領域(18)は、n型の低濃度ドープ領域(32)と、n+領域34とを有するが、ソースhalo領域は有しない。ドレイン領域(20)は、n型の低濃度ドープ領域42と、n+領域44と、p型ドレインhalo領域(50)とを有する。ドレインhalo領域(50)は、ドレイン領域にイオンを斜めに注入することにより形成された、ドープ領域である。

(もっと読む)

トランジスタ及びこれの製造方法

【課題】 超高集積を有して形成することができ、改善された構造の不純物領域を有する半導体装置のトランジスタ及びトランジスタを製造する方法が開示されている。

【解決手段】 超高集積を有して形成することができながら改善された構造の不純物領域を有する半導体装置のトランジスタにおいて、前記トランジスタは表面、表面より低い高さを有する{100}面である底面、及び表面と底面とを連結する{111}面である側面を有する半導体基板を含む。ゲート構造物が表面上に形成される。エピタキシャル層が底面と側面上に形成される。不純物領域がゲート構造物の両側に形成される。急なPN接合を形成することができるので、不純物領域の間で短チャンネル効果の発生を抑制することができる。

(もっと読む)

ゲルマニウム基板タイプ材料およびその手法

ゲルマニウム回路タイプの構造が促進される。一実施形態例では、多段階の成長およびアニール・プロセスを実施して、ヘテロエピタキシャルル・ゲルマニウムなどのゲルマニウム(Ge)含有材料を、シリコン(Si)またはシリコン含有材料を含む基板上に成長させる。いくつかの応用例では、ゲルマニウム含有材料の上面に向かって貫通する欠陥が全体的に抑制されて、欠陥が全体的にシリコン/ゲルマニウム境界面付近に閉じ込められる。これらの手法は、ゲルマニウムMOSコンデンサ、pMOSFET、およびオプトエレクトロニック・デバイスを含む、さまざまなデバイスに適用できる。  (もっと読む)

(もっと読む)

121 - 140 / 146

[ Back to top ]