Fターム[5F140BK12]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域の形成 (4,176) | 不純物の導入 (3,397)

Fターム[5F140BK12]の下位に属するFターム

Fターム[5F140BK12]に分類される特許

41 - 60 / 146

半導体装置の製造方法

【課題】

深さ方向の圧縮応力を印加して、NMOSトランジスタの性能を向上した半導体装置を提供する。

【解決手段】

CMOS型半導体装置用シリコン基板のNMOSトランジスタ領域、PMOSトランジスタ領域上方に多結晶シリコンのゲート電極を形成し、ゲート電極側壁上に第1サイドウォールスペーサを形成し、NMOSトランジスタ領域、PMOSトランジスタ領域に選択的にイオン注入を行ない、第1サイドウォールスペーサに整合した低抵抗ソース/ドレイン領域を形成する際、NMOSトランジスタ領域においてはゲート電極の上部をアモルファス化し、少なくともNMOSトランジスタ領域において第1サイドウォールスペーサを実質的に除去し、ゲート電極を覆ってキャップ膜を形成し、低抵抗ソース/ドレイン領域の活性化を行うと共にアモルファス化されたゲート電極の再結晶化を行う熱処理を行ない、キャップ膜を異方性エッチングして第2サイドウォールスペーサに加工する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極、ソース電極またはドレイン電極にタングステン膜を用いた半導体装置において、nMOSとpMOS間での抵抗差を低減可能な半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極14a,14bとソース/ドレイン拡散層16a,16bとを有するnMOS及びpMOSを形成し、ゲート電極14a,14b及びソース/ドレイン拡散層16a,16b上に、タングステン膜17を選択的に形成し、タングステン膜17を覆うように、絶縁膜(エッチングストップシリコン酸化膜18、シリコン窒化膜19)を形成し、pMOS領域12bの絶縁膜を除去し、pMOS領域12bのタングステン膜17上に、タングステン膜20を選択的に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】歪み発生層に緩和が生じにくい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極15と、ゲート電極15の両側面上に形成され、断面L字状の内側サイドウォール17Bと、半導体基板11におけるゲート電極15の両側方の領域に埋め込まれた歪み発生層19とを備えている。内側サイドウォール17Bは、5×1019/cm3以上の炭素を含む炭素含有シリコン酸化膜からなる。歪み発生層19は、1%以上の炭素を含む炭素含有シリコンエピタキシャル層を有する。

(もっと読む)

半導体装置の作製方法

【課題】せり上げ構造を有する半導体装置において、せり上げる領域をエッチングする際に、活性層である島状半導体膜がエッチングされるのを抑制する。

【解決手段】島状半導体膜の表面を酸化あるいは窒化して第1の絶縁膜を形成し、第1の絶縁膜の一部の領域上に半導体膜を形成し、第1の絶縁膜の一部を除去して島状半導体膜の中の半導体膜が形成されていない領域を露出させ、島状半導体膜の表面及び半導体膜を酸化あるいは窒化して第2の絶縁膜を形成し、第2の絶縁膜上にゲート電極を形成し、第2の絶縁膜をエッチングしてゲート絶縁膜を形成し、ゲート電極をマスクとして島状半導体膜及び半導体膜に一導電型を付与する不純物元素を添加し、島状半導体膜及び半導体膜を加熱して不純物元素を活性化させ、島状半導体膜及び半導体膜を加熱することにより第1の絶縁膜が消失する半導体装置の作製方法に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタのゲート電極、及びp型MISトランジスタのゲート電極の双方を精度良く実現する。

【解決手段】第1のMISトランジスタと第2のMISトランジスタとを備えた半導体装置において、第1のMISトランジスタは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され、シリコン膜14aとシリコン膜14a上に形成された第1の金属シリサイド膜20aとからなる第1のゲート電極26aとを備え、第2のMISトランジスタは、半導体基板10における第2の活性領域10b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜13b上に形成され、フルシリサイド化された第2の金属シリサイド膜20Bからなる第2のゲート電極26bとを備え、第1の金属シリサイド膜20aは、第2の金属シリサイド膜20Bに比べて膜厚が薄い。

(もっと読む)

半導体装置及びその製造方法

【課題】ソースドレイン領域のサイズが増大することがない局所配線構造を備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極22及び半導体基板11におけるゲート電極22の両側方にそれぞれ形成された第1のソースドレイン領域29A及び第2のソースドレイン領域29Bを有するトランジスタ12と、半導体基板11の上における第1のソースドレイン領域29Aを挟んでゲート電極22と反対側に形成されたゲート配線42と、ゲート配線42と第1のソースドレイン領域29Aとを接続する局所配線構造60とを備えている。局所配線構造60は、第1のソースドレイン領域29A及びゲート配線42の上面に跨って形成されたSiGe層61によって構成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】エピタキシャル層から半導体基板への不純物拡散を防止でき、これにより素子特性の向上を図ることが可能な半導体装置を提供する。

【解決手段】半導体基板3上に設けられたゲート電極11と、ゲート電極11両脇における半導体基板3のリセス部(掘り下げ部)3aに半導体材料をエピタキシャル成長させてなるエピタキシャル層17とを備え、エピタキシャル層17が不純物を拡散させたソース/ドレイン領域として設けられた半導体装置1aにおいて、リセス部3aの側壁には絶縁性の拡散防止層15が設けられている。そして、エピタキシャル層17は、拡散防止層15から露出しているリセス部3aの底面とリセス部3aの側壁上部Aとで、半導体基板3に接合している。

(もっと読む)

半導体装置

【課題】チャネル領域における高いキャリア移動度を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成され、内部におけるキャリアの移動度がSi結晶よりも大きい第1の結晶からなる半導体層と、前記半導体層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層を挟んで形成され、前記半導体層に前記半導体層内のキャリアの移動度が上昇する方向に歪みを与える第2の結晶を含み、前記半導体層に接する深さの浅い領域であるソース・ドレインエクステンション領域を有するソース・ドレイン領域と、を有する。

(もっと読む)

半導体装置、およびその製造方法

【課題】応力膜によるチャネル領域への歪み効果を向上させる形状の半導体基板を有し、かつ十分な深さのソース・ドレイン領域を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板と、半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、前記半導体基板の前記ゲート電極の両側の前記ゲート電極から離間した領域に凹部を形成する工程と、前記凹部の底面および側面からほぼ同じ深さまで前記半導体基板に導電型不純物を注入する工程と、前記凹部の底面および側面上に、前記半導体基板内の前記ゲート電極下のチャネル領域に歪みを与えて前記チャネル領域における電荷移動度を向上させる応力膜を形成する工程と、を含む。

(もっと読む)

半導体製造装置及び半導体装置の製造方法

【課題】基板上の表面角の異なる領域を選択的に局所加熱することができる半導体製造装置を提供する。

【解決手段】第1の領域と前記第1の領域と面方位が異なる第2の領域が形成された基板6の前記第2の領域へ偏光した光を入射する照射部1〜5と、前記第2の領域からの前記偏光した光の反射光が入射される回転検光子8と、回転検光子8を介して前記反射光を受光し、前記反射光の強度を検出する光検出器9と、回転検光子8の回転角度及び前記検出された強度に基づいて前記第2の領域の屈折率を算出する解析部10と、基板6へレーザを照射するレーザ照射部12、13と、前記屈折率に基づいて前記第2の領域のブリュースター角を求め、前記第2の領域の表面に前記ブリュースター角で前記レーザが入射するようにレーザ照射部12、13を制御するコントローラ11と、を備える。

(もっと読む)

チャンネルに対して設計されたひずみを与えるストレッサー

【課題】チャネルに対して設計されたひずみを与えるストレッサー及びその形成方法を提供すること。

【解決手段】半導体基板が、異なる不純物濃度を有する異なる部分を有するヘテロエピタキシャル・シリコン含有物質で埋め込まれたリセスを備える。歪まされた膜が、リセスされたソース/ドレイン領域を、傾斜してボトム−アップで埋め込むことができる。膜は、所定の濃度のひずみを引き起こす不純物でリセス側壁をラインし、より低い濃度の不純物でリセスの残りの部分を埋め込む。後者の場合では、側壁ライナーは先細りになりえる。

(もっと読む)

PチャネルMOSトランジスタ、NチャネルMOSトランジスタ及び不揮発性半導体記憶装置

【課題】高誘電率膜をゲート絶縁膜に用い、消費電力を低減したPMOSトランジスタを提供する。

【解決手段】半導体基板1と、半導体基板1の表面部にチャネル領域2を挟むように形成されたP型不純物拡散層3と、チャネル領域2上に形成されハフニウム又はジルコニウムと希土類元素又は第2族元素とを含む絶縁膜4a、4b、及び絶縁膜4a、4b上に形成されたシリコン酸化膜4cを有するゲート絶縁膜4と、ゲート絶縁膜4上に形成されたゲート電極5と、を備えるPMOSトランジスタ。

(もっと読む)

半導体装置

【課題】ロールオフ特性を劣化させずにチャネル領域に十分な歪みを生じさせることのできるエピタキシャル結晶を埋め込んだソース・ドレイン領域を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記半導体基板の前記ゲート電極下の領域に形成されたチャネル領域と、前記チャネル領域を挟んで形成され、チャネル方向に平行な方向の導電型不純物の濃度分布が、前記ゲート電極から遠くなるに従って濃度が増加する部分を有するソース領域およびドレイン領域と、を有する。

(もっと読む)

高耐圧半導体装置

【課題】 高耐圧半導体装置では、高電圧配線に高電圧が印加された時、トランジスタのチャネル領域等が反転し、動作に異常をきたすことがあった。

【解決手段】高電圧配線32に高電圧が印加されたときに、意図的に反転する領域33を設け、高電圧が印加されているときにオン状態となる能動素子50を備える。すなわち、能動素子50は、ソース領域25およびドレイン領域26と、ソース領域25およびドレイン領域26に接続された低電圧配線28、29とを含む。高電圧配線32は、低電圧配線28、29と上下方向に重ならないように、かつ、ソース領域25およびドレイン領域26間の上を覆うように設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】超短チャネル長化でき、Si層厚一定によって閾値を変化させずにON電流を増加でき、さらにバックゲートにより閾値も動的に変更できる縦型トランジスタ構造を備えた半導体装置および半導体装置の製造方法を提供することを目的とする。

【解決手段】基板2上に、中心軸Mが基板2面と垂直方向に形成されてなる筒型の基柱3と、基柱3の上部と下部に、中心軸Mを中心とする同心形状に形成された第1導電型からなるソース・ドレイン拡散層4a,4bと、ソース・ドレイン拡散層4a,4bに挟まれた基柱3の中間部に形成された第1導電型からなるボディ層と、基柱3の側面にゲート絶縁膜6を介して形成されたフロントゲート電極7とを備えたことを特徴とする。また、第2導電型からなるバックゲート電極8が、基柱3の内側に上部から下部まで貫通する柱状に形成されてなることとする。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォール形成時に異常放電が生じることを抑制できる半導体装置の製造方

法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、縁から2.5mm以上離れた領域に

位置するゲート絶縁膜3a,3bを表面に有する半導体ウェハ1の全面上に、導電膜4及

び反射防止膜10を形成する工程と、第1マスクパターン50をマスクとしたエッチング

により、半導体ウェハ1の周縁部1c上に位置する反射防止膜10を除去する工程と、反

射防止膜10上に第2マスクパターンを形成し、該第2マスクパターンをマスクとして反

射防止膜10及び導電膜4をエッチングすることによりゲート電極を形成する工程と、ゲ

ート電極上、ゲート絶縁膜3a,3b上、及び素子分離膜2上に絶縁膜を形成する工程と

、この絶縁膜を、平行平板型のエッチング装置を用いてエッチバックすることにより、サ

イドウォールを形成する工程とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】サイドウォールの幅及びゲート長の微小化を図りつつ、短チャンネル効果及び拡散層領域における接合容量の増大が抑えられ、また、拡散層領域の寄生抵抗が小さく、HC耐性に優れた半導体装置及びその製造方法を提供すること。

【解決手段】本発明の半導体装置は、半導体基板1と、1対の第1の拡散層領域6a、6bと、ゲート電極3と、第1の拡散層領域6a、6bと重なるように設けられた一対のシリコン選択成長層10a、10bと、シリコン選択成長層10a、10bに設けられた第2の拡散層領域7a、7bと、第1の拡散層領域6a、6bと第2の拡散層領域7a、7bとを電気的に接続する第3の拡散層領域8a、8bと、第1の拡散層領域6a、6bの周囲に設けられ、第1の拡散層領域6a、6bと逆導電型の第4の拡散層領域9a、9bとを有する。

(もっと読む)

半導体装置の製造方法

【課題】断線を防ぐことが可能な半導体装置の製造方法を提供する。

【解決手段】PMOSトランジスタにおいて、p型活性領域122が、ラインの幅方向においてn型活性領域121の一部の領域と重なるように形成される。従って、n型活性領域121とp型活性領域122とが互いに接するように混在する場合(バッティングディフュージョン)においても、n型活性領域121とp型活性領域122との界面付近に低濃度領域が生じることを防ぐことができる。

(もっと読む)

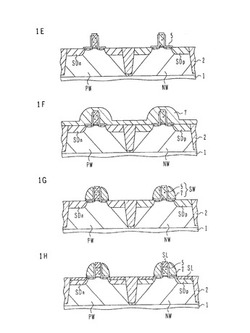

半導体装置の製造方法、半導体装置および半導体層の形成方法

【課題】半導体上にモフォロジの良好な半導体層を選択的にエピタキシャル成長させる。

【解決手段】リセスド・ソース・ドレイン型pMOSFETを形成する際、STIを形成したSi基板上にゲート絶縁膜を介してゲート電極を形成し(ステップS1)、サイドウォールを形成した後(ステップS2)、その両側のSi基板に部分的にリセスを形成する(ステップS3)。そして、そのSi基板のリセス内に、下層部の方が上層部よりも、サイドウォールやSTIに対する成長選択性が低くなるような条件を用いて、下層部と上層部をエピタキシャル成長させ、SiGe層を形成する(ステップS4,S5)。これにより、Si基板のリセス内に、サイドウォール等に対する成長選択性を確保しつつ、モフォロジの劣化が抑えられたSiGe層を形成することが可能になる。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】チャネルが形成される部分における分極電荷の発生を抑えると共に、ブレークダウンの発生を抑制できる、窒化物半導体素子およびその製造方法を提供すること。

【解決手段】電界効果トランジスタは、n型GaN層3、p型GaN層4およびn型GaN層5が積層された窒化物半導体積層構造部2を備えている。窒化物半導体積層構造部2には、ドレイントレンチ6が形成されることにより、メサ積層部8が形成されている。メサ積層部8の壁面9は、n型GaN層5の頂面5aとの境界付近に位置する上側端部11と、n型GaN層3の上面3aとの境界付近に位置する下側端部12と、上側端部11と下側端部12との間に位置する中央部10とを有している。より具体的には、壁面9は、全体として傾斜角度の異なる複数の平面形状の傾斜部分17〜27を有している。そして、この壁面9には、ゲート絶縁膜15を挟んで、ゲート電極16が対向配置されている。

(もっと読む)

41 - 60 / 146

[ Back to top ]