Fターム[5F140BK12]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域の形成 (4,176) | 不純物の導入 (3,397)

Fターム[5F140BK12]の下位に属するFターム

Fターム[5F140BK12]に分類される特許

101 - 120 / 146

半導体装置の製造方法

【課題】ダミーゲートを用いた半導体装置の製造方法において、RPTの短縮、ゲート寸法の加工精度の向上を図る半導体装置の製造方法を提供する。

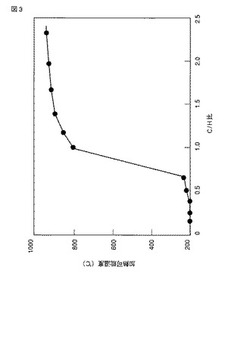

【解決手段】半導体基板上にダミーゲートを形成する工程、前記ダミーゲートをマスクとして前記半導体基板に不純物を導入して、ソース・ドレイン拡散領域を形成する工程、前記ダミーゲートの周囲に絶縁膜を形成する工程、前記ダミーゲートを除去して開口部を形成する工程、及び前記開口部にゲート絶縁膜を介してゲート電極を形成する工程を具備する方法である。前記ダミーゲートは、前記半導体基板上に、炭素と水素との原子比(C/H)が1以上であり、かつ炭素の絶対量が50%以上である炭素過剰の組成のポリマーを塗布してポリマー膜を形成する工程、前記ポリマー膜上にフォトレジストパターンを形成する工程、及び前記フォトレジストパターンを前記ポリマー膜に転写する工程により形成されることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】CMOSトランジスタを備える半導体装置において、ゲート絶縁膜と接する部分が金属シリサイド膜からなるゲートの仕事関数のマッチングと、ゲート電極低抵抗化との両立を実現する。

【解決手段】半導体装置は、基板100上にゲート絶縁膜102を介して形成されたゲート電極と、基板100におけるゲート電極123の両側に形成されたソース領域及びドレイン領域106とをそれぞれ有する複数のMOSトランジスタを備え、複数のMOSトランジスタは、ゲート電極としてPMOSゲート電極123を有するPMOSトランジスタを含み、PMOSゲート電極123は、ゲート絶縁膜102と接する第1の部分123aと、第1の部分123aの上に位置し且つ第1の部分123aよりもゲート長方向の幅が大きい第2の部分123bとを有する。

(もっと読む)

炭化珪素系半導体素子および発光素子

【課題】バンドギャップを小さくすると共に電子散乱が抑制され、炭化珪素を用いたチャネル領域でのキャリア移動度を向上させた半導体素子、並びにレーザを発振する発光素子を提供する。

【解決手段】SiC基板11上に、AlドープされたSi0.9M0.1C混晶(Mは、Ge,Sn,Pbの少なくとも一種)よりなる薄膜または細線のAlドープSiMC層14が設けられている。また、SiC基板11の内部に、AlドープされたSi0.9M0.1C混晶(Mは、Ge,Sn,Pbの少なくとも一種)よりなる薄膜または細線のAlドープSiMC層14が設け発光させる。

(もっと読む)

半導体装置の製造方法

【課題】シリコン系材料、例えばシリコン基板、多結晶シリコンパターン等をドライエッチングする際の前処理のエッチングに、フッ化水素とアンモニアとからなるエッチングガスを用いることで、自然酸化膜を選択的に除去することを可能とする。

【解決手段】酸化シリコン(素子分離領域12、サイドウォール18、19等)と表面に自然酸化膜21、22が形成されたシリコン系材料(シリコン基板11)とが露出された状態で自然酸化膜21、22を除去する工程と、自然酸化膜21、22が除去されたシリコン系材料(シリコン基板11)をエッチング加工する工程とを備えた半導体装置の製造方法であって、自然酸化膜21、22を除去する工程は、エッチングガスにフッ化水素とアンモニアとを用いたドライエッチングにより行うことを特徴とする。

(もっと読む)

絶縁ゲイト型半導体装置の作製方法

【課題】短チャネル効果を防止しつつチャネル長の短い微細な半導体装置を実現する。

【解決手段】チャネル形成領域103に対して人為的かつ局部的にドットパターン状の不純物領域104を形成する。この不純物領域104がドレイン側空乏層のチャネル形成領域103への広がりを抑え、短チャネル効果を防止する。また、不純物領域104によってチャネル幅Wを実質的に細分化し、それに伴って生じる狭チャネル効果によって短チャネル効果によるしきい値電圧の低下を緩和する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離領域から発生する結晶欠陥等の発生を低減するための半導体装置の製造方法を提供する。

【解決手段】本発明にかかる半導体装置は、(a)半導体層10に第1の溝210からなる第1認識マークを形成する工程と、(b)第1認識マーク210を用いて、半導体層にウェル20を形成する工程と、(c)半導体層の上に、少なくとも第1認識マークを含み、該第1認識マークの平面形状と比して大きい平面形状の第1の開口42を有するマスク層M1を形成する工程と、(d)マスク層M1を用いて、半導体層をエッチングすることにより第2の溝からなる第2認識マークと、を形成する工程と、(e)半導体層に、素子分離絶縁層22を形成する工程と、(f)半導体層に、第2認識マークを用いてトランジスタ100を形成する工程と、を含む。

(もっと読む)

半導体素子

【課題】 基板のフェルミ準位の影響を低減することができる半導体素子を提供する。

【解決手段】 半導体基板1の一方の面上に、この半導体基板1と同じ半導体材料を使用しドーパントの種類又は濃度を変えて緩衝層2を形成する。そして、緩衝層2上に夫々局所的に半導体層3a及び3bを形成し、この半導体層3a及び3bの対向する端部上及びこれらの間に、半導体基板1と同じ半導体材料を使用し、半導体層3a及び3bよりもドーパント濃度が低いチャネル層4を形成する。その際、緩衝層2の厚さD(nm)を、半導体基板1のフェルミ準位とチャネル層4のフェルミ準位との差V(eV)、半導体基板1の有効ドナーの濃度又は有効アクセプタの濃度NS(m−3)、緩衝層2の有効ドナーの濃度又は有効アクセプタの濃度NB(m−3)、チャネル長L(m)、素電荷e、緩衝層2の比誘電率εB、真空の誘電率をε0から求められる下記数式の範囲内とする。 (もっと読む)

(もっと読む)

応力変形させた半導体装置およびその製造方法

【課題】応力を調整し、性能向上を図った半導体装置、およびその製造法を提供すること。

【解決手段】ゲート電極104は、半導体基板(バルクシリコン基板、SOI層など)102から電気的に絶縁されている。第1側壁スペーサ110がゲート電極104の側壁に沿って形成される。上記犠牲側壁スペーサが第1側壁スペーサ110と隣接するように形成される。上記犠牲側壁スペーサおよび第1側壁スペーサ110は半導体基板102を覆っている。平坦化層は、該平坦化層の一部が上記犠牲側壁スペーサと隣接するように、半導体基板102を覆って形成されている。上記犠牲側壁スペーサが取り除かれ、エッチングによって半導体基板102内にくぼみが形成される。実質的に、上記くぼみは第1側壁スペーサ110と上記平坦化層の一部との間に配置されている。半導体材料(SiGe、SiCなど)116は上記くぼみに堆積される。

(もっと読む)

半導体装置の製造方法

【課題】

接合リーク電流の発生が軽減されたエレベーテッド・ソース/ドレイン構造を有する半導体装置の製造方法を提供することができる。

【解決手段】

本発明に係る半導体装置の製造方法は、半導体基板102表面の所定の位置に溝部105を形成する工程と、溝部105を埋設するとともに、半導体基板102表面から突出した形状を有する素子分離膜106を形成する工程と、半導体基板102および素子分離膜106を覆うように膜108を形成する工程と、膜108を選択的に除去して、半導体基板102上に露出する素子分離膜106の側壁106aに保護膜110を形成する工程と、半導体基板102上にゲート電極部123を作製する工程と、保護膜110とゲート電極部123との間の半導体基板102の表面にエピタキシャル層124を形成する工程と、エピタキシャル層124の少なくとも一部にシリサイド層130を形成する工程と、を含む。

(もっと読む)

窒化物上へゲルマニウム・スペーサを選択的に堆積するための構造及び方法

【課題】 窒化物上へゲルマニウム・スペーサを選択的に堆積するための構造及び方法を提供すること。

【解決手段】 半導体製造プロセス中でゲルマニウム構造体を選択的に形成する方法は、化学的酸化物除去(COR)プロセスにおいて自然酸化物を除去し、次いで、加熱された窒化物及び酸化物表面を加熱されたゲルマニウム含有ガスに曝して、ゲルマニウムを選択的に窒化物表面上にだけ形成し、酸化物表面上には形成しない。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】シリコン基板の表面から非常に浅い領域に高濃度の不純物を導入することができる半導体装置の製造方法を提供する。

【解決手段】p型シリコン基板1上の所定の位置に形成された所定形状のゲート絶縁膜4とゲート電極5を含むゲート構造のゲート長方向両側に浅い接合のソース/ドレイン領域を形成する半導体装置の製造方法であって、ソース/ドレイン領域の形成領域を、所定の深さにエッチングするエッチング工程と、p型シリコン基板1上に所定の組成の30Si層を堆積させ、ソース/ドレイン領域の形成領域に30Si層21を選択エピタキシャル成長させる30Si層形成工程と、p型シリコン基板1に中性子線50を照射して、30Si層21中に所定の濃度の31Pを形成する中性子線照射工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】 特性や信頼性に優れた半導体装置を作製することが可能な製造方法を提供する。

【解決手段】 Si基板上のゲート形成予定領域にダミーゲートを形成する工程と、このダミーゲートの両側に対応する領域のSi基板内に不純物を導入し熱処理によってこの不純物を活性化することによりソース・ドレイン領域23、25を形成する工程と、ダミーゲートの側壁を取り囲む絶縁膜24、26を形成する工程と、ダミーゲートを除去して開口部を22a形成する工程と、この開口部が形成された領域又はその下部領域にSiGe層28を形成する工程と、開口部に露出しているSiGe層上にゲート絶縁膜29を介してゲート電極30、31を形成する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート電極および不純物拡散層にシリサイド膜が形成された半導体装置において、不純物拡散層のシリサイド膜の異常成長や凝集を抑える。

【解決手段】 半導体装置100は、シリコン基板102と、シリコン基板102上に形成され、ゲート電極132を含む半導体素子と、ゲート長方向の断面において、シリコン基板102の半導体素子が形成された領域の両側方に形成された不純物拡散層121(または122)と、不純物拡散層121(または122)表面に形成され、第1の金属のシリサイド化合物により構成された第1のシリサイド膜130と、ゲート電極132の少なくとも表面に形成され、第1の金属のシリサイド化合物よりシリサイド化の温度が低い第2の金属のシリサイド化合物により構成された第2のシリサイド膜131と、を含む。

(もっと読む)

固相エピタキシー方式を用いた半導体素子及びその製造方法

【課題】コンタクト物質で低温熱工程によりエピタキシャルシリコンを形成しながらも、エピタキシャルシリコンの有する高い自らの比抵抗値によるコンタクト抵抗の増加を防止できるエピタキシャルシリコンをコンタクトとする半導体素子及びその製造方法を提供する。

【解決手段】固相エピタキシー工程を用いたエピタキシャル層と、前記エピタキシャル層上の第1金属層と、前記第1金属層上の窒化物系バリヤメタルと、前記バリヤメタル上の第2金属層と、前記エピタキシャル層と第1金属層との間に形成された金属シリサイドとを含む。

(もっと読む)

PFETの移動度を強化したステップ埋め込みSiGe構造

【課題】埋設されたSiGe層を有し、そのSiGe層の浅い部分がPFETチャネルに近く、SiGe層の深い部分がPFETチャネルからさらに離れているPFETを含むデバイスと、その製造方法を提供する。

【解決手段】SiGe層はテーパーされているチャネル方向に面する側面に境界を有している。このような形状によって、PFETチャネルは実質的に拡張接合特性を劣化させる必要なく、大きい圧縮応力を受けることができる。テーパーされたSiGe境界は複数のディスクリートなステップとして構成される。例えば2、3以上のディスクリートなステップが形成される。

(もっと読む)

修正されたCMOSプロセスにより製造された放射線硬化トランジスタ

NMOS電界効果トランジスタ1は、トランジスタ本体のエッジに沿ってソース30Aとドレイン30Bの間に延在し、また、フィールド絶縁体中におよびトランジスタの内部中に制限された長さだけ延在し、トランジスタ設計しきい値電圧を保持するイオン注入されない領域を本体の中央に残しており、制限された水平方向の長さの1対の保護帯域イオン注入115により放射線硬化を行われる。  (もっと読む)

(もっと読む)

MOSトランジスタのためのゲート電極

一態様では、シリコン層(112')に第1の熱処理を施し、このシリコン層(112')上に金属積層体(110')を形成し、この金属積層体に第2の熱処理を施すことによって、トランジスタのゲートを形成する。第1の熱処理は、急速熱アニールステップを含み、第2の熱処理は、急速窒化ステップを含む。本発明により得られたるゲートは、シリコン層と金属積層体との間で比較的低い界面接触抵抗を示し、そのため、このゲートを高速デバイスで使用すると有利である。  (もっと読む)

(もっと読む)

半導体装置

【課題】 ショットキー型電界効果トランジスターに於いて、殊にソース領域近傍のチャネル領域に対するゲート電極の制御性を高めて、素子の電流駆動能力の向上を図る。

【解決手段】 ゲート絶縁膜を異なる誘電率を持つ膜の積層とすることで、誘電率の高い材料のみで形成した場合と比べてゲート絶縁膜の幾何学的な意味の厚さを薄く形成することを可能とし、ゲート電極から出た電気力線のゲート絶縁膜の側面から外への漏れに起因する、殊にソース領域近傍のチャネル領域の電位に対するゲート電極の制御性の低下を抑制する事が可能となる。また、誘電率の高い材料よりなるゲート側壁絶縁膜12を設ける事に依り、異なる誘電率を持つ物質の界面に於ける電気力線の屈折に依って、ゲート電極から出た電気力線をソース領域近傍のチャネル領域に集める事が可能となり、ソース領域とチャネル領域との間に形成されるショットキー障壁を薄くし、その抵抗を低減する。

(もっと読む)

絶縁膜、絶縁膜の形成方法、半導体素子、電子デバイスおよび電子機器

【課題】所望の比誘電率を有し、機械的強度に優れる絶縁膜、この絶縁膜を容易に形成し得る絶縁膜の形成方法、この絶縁膜を備える半導体素子、電子デバイスおよび電子機器を提供すること。

【解決手段】本発明の絶縁膜は、導電体同士を絶縁するものであって、絶縁性基材42中に、当該絶縁膜の膜強度を向上させる絶縁性粒子41を含有してなるものである。この絶縁膜は、絶縁性粒子41として、絶縁性基材42の比誘電率と異なる比誘電率の粒子を用いることにより、その比誘電率を調整したものである。例えば、絶縁性粒子41として、絶縁性基材42の比誘電率より低い比誘電率の粒子を用いることにより、絶縁膜全体の比誘電率を調整(低下)することができ、かかる絶縁膜は、層間絶縁膜に好適に適用される。

(もっと読む)

絶縁膜、絶縁膜の形成方法、半導体素子、電子デバイスおよび電子機器

【課題】所望の比誘電率を有し、機械的強度に優れる絶縁膜、この絶縁膜を容易に形成し得る絶縁膜の形成方法、この絶縁膜を備える半導体素子、電子デバイスおよび電子機器を提供すること。

【解決手段】本発明の絶縁膜は、導電体同士を絶縁するものであって、絶縁性粒子41の集合体の間隙を、当該絶縁膜の膜強度を向上させる絶縁性の充填物42で充填してなるものである。この絶縁膜は、充填物42として、絶縁性粒子41の比誘電率と異なる比誘電率の材料を用いることにより、その比誘電率を調整したものである。例えば、充填物42として、絶縁性粒子41の比誘電率より低い比誘電率の材料を用いることにより、絶縁膜全体の比誘電率を調整(低下)することができ、かかる絶縁膜は、層間絶縁膜に好適に適用される。

(もっと読む)

101 - 120 / 146

[ Back to top ]