Fターム[5F140BK19]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域形成後の処理 (2,202)

Fターム[5F140BK19]の下位に属するFターム

Fターム[5F140BK19]に分類される特許

21 - 40 / 41

半導体装置の製造方法

【課題】金属シリサイド層を形成する工程を備えた半導体装置の製造方法において、ソー

ス/ドレイン領域に砒素(As)が高濃度でイオン注入される場合であっても、金属膜の

シリサイド化が面内で均一になされるようにする。

【解決手段】ポリシリコンからなるゲート電極4が形成されたシリコン基板1上に、金属

膜7を形成する。次に、第1導電型の不純物イオンを存在させる領域をマスクした状態で

、第1工程後のシリコン基板1上の金属膜7の全面に、第2導電型の不純物イオンを所定

のエネルギーで注入する。次に、第2工程後のシリコン基板1を熱処理することで、シリ

コン基板1およびゲート電極4と金属膜7を反応させて金属シリサイド層9を形成する。

次に、シリコン基板1をエッチングすることで、金属シリサイド層形成に関与せずに基板

上に残存した金属膜7を除去する。

(もっと読む)

半導体装置の製造方法

【課題】長波長レーザアニールを用い半導体基板内の所定の領域を選択的にアニールする。

【解決手段】レーザ光20の照射に対し膜厚が薄くなるに従い反射率が小さくなる反射率調整膜17を、領域Anおよび領域Apを有する半導体基板1上に形成した後、領域An上の反射率調整膜17をエッチングする。次いで、半導体基板1にレーザ光20を照射し、領域Anのn−型半導体領域11、n+型半導体領域14に対して、アニールを行う。同様にして、反射率調整膜17を半導体基板1上に形成した後、領域Ap上の反射率調整膜17をエッチングする。次いで、半導体基板1にレーザ光20を照射し、領域Apのp−型半導体領域12、p+型半導体領域15に対して、アニールを行う。

(もっと読む)

半導体装置の製造方法

【課題】不純物注入領域を高濃度に活性化させるとともに、ゲートリーク電流を低減させ得る半導体装置の製造方法を提供する。

【解決手段】浅いソース・ドレインエクステンションを活性化させる際に、nMOSにおいてスパイクRTA(第1のアニール)とこれより昇降温速度の大きい超高速昇降温アニール(第2のアニール)を併用し、pMOSにおいては超高速昇降温アニール(第2のアニール)のみを適用する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネルMISトランジスタとpチャネルMISトランジスタとが1つの基板に形成された半導体装置において、ゲート電極及び拡散層における抵抗が上昇しにくい半導体装置及びその製造方法を実現できるようにする。

【解決手段】半導体装置は、シリコン基板21に形成されたnチャネルMISトランジスタ11及びpチャネルMISトランジスタ12を備えている。nチャネルMISトランジスタ11は、第1のゲート電極14Aと、n型ソースドレイン領域16cと、第1のゲート電極14A及びn型ソースドレイン領域16cの上面を覆う第1のプラズマ反応膜18とを有している。pチャネルMISトランジスタ12は、第2のゲート電極14Bと、p型ソースドレイン領域16fと、第2のゲート電極14B及びp型ソースドレイン領域16fの上面を覆う第2のプラズマ反応膜18とを有している。

(もっと読む)

炭化珪素半導体装置およびその製造方法。

【課題】炭化珪素半導体装置のチャネル移動度の向上を図る。

【解決手段】 ゲート酸化膜形成工程の降温時に、ウェット雰囲気を維持したまま、終端・脱離温度(800〜900℃)以下まで降温させる。これにより、ゲート酸化膜とチャネル領域を構成するp型ベース層の界面のダングリングボンドをHもしくはOHの元素で終端させることが可能となる。このため、高いチャネル移動度の反転型ラテラルMOSFETとすることが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板表面のRIE処理による汚染を防止し、エレベーテッド・ソース、ドレイン拡散層の膜厚の制御が可能な半導体装置の製造方法の提供。

【解決手段】半導体基板110上に第1の絶縁膜112と、第1及び第2のダミーゲート電極113、第2の絶縁膜114とを形成する工程と、これらの側面に第3の絶縁膜115を形成し、ウエットエッチング処理により、第1、第2のダミーゲート電極及び第3の絶縁膜が形成されていない半導体基板上の第1の絶縁膜を除去し、第1、第2の領域の半導体基板表面を露出する工程と、この露出基板面に第1、第2のエピタキシャル層の第1、第2の拡散層118、121とを形成する工程と、第1及び第2の絶縁膜112、114、第1及び第2のダミーゲート電極113とを除去し、半導体基板110を露出する工程と、この露出された半導体基板110上にゲート絶縁膜126、第1及び第2のゲート電極128を形成する工程とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層に応力が付加され、かつ高信頼なMOSFETを実現する。

【解決手段】半導体基板と、前記半導体基板の表面に対向して設けられ、単結晶または多結晶構造を有する一対のソース・ドレイン電極と、前記ソース・ドレイン電極の間の前記半導体基板の表面に形成された単結晶チャネル領域と、前記チャネル領域上にゲート絶縁膜を介して形成されたゲート電極と、前記ソース・ドレイン電極の上部に形成された金属化合物層と、前記ソース・ドレイン電極の下部に位置し、前記ソース・ドレイン電極を構成する物質の固有の格子間隔とは異なる格子間隔を保持した結晶構造を有する応力付与層と、前記応力付与層の下部に位置する第1の絶縁層とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】ニッケルシリサイド層を備えた半導体装置において、ニッケルシリサイドの異常成長のない均一なシリサイド層を形成することを目的とする。

【解決手段】シリコン基板上にゲート電極を形成する工程と、ゲート電極の両側にサイドウォールを形成する工程と、シリコン基板上にシリサイド領域を形成する工程とを備え、シリサイド領域の形成工程の前にサイドウォール下のシリコン基板の表面領域にシリサイド化の反応阻害層を形成する。

(もっと読む)

半導体装置

【課題】半導体基板と、前記半導体基板に形成された第1導電型を有する素子領域と、前記素子領域の表面上に絶縁膜を介して形成された電極と、前記素子領域に形成され、前記電極の両側に形成された第2導電型の第1拡散層および第2拡散層とよりなる半導体装置において、接合容量を増大させることなく、効果的なパンチスルーストッパを形成する。

【解決手段】前記素子領域の表面から離間し、かつ、前記第1拡散層及び第2拡散層と離間して、前記素子領域内部に形成された第1導電型の高濃度不純物層を設け、さらに前記素子領域の表面と前記高濃度不純物層との間に配置され、かつ、前記第1拡散層および第2拡散層と離間して、前記第1拡散層と第2拡散層との間に形成された第1導電型のパンチスルーストッパ領域を、前記パンチスルーストッパ領域の下端が前記高濃度不純物層の近傍に達するように設ける。

(もっと読む)

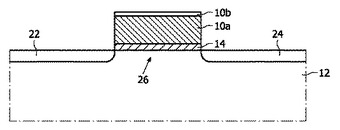

ポリシリコン電極を有する半導体デバイス

MOSトランジスタなどの半導体デバイスを製造する方法。本デバイスは、ポリシリコンのゲート(10)および、半導体基板(12)内に形成されチャネル領域(26)で分離されたドーピング領域(22,24)を備える。後の熱アニールの間にドーパント・イオンが拡散することを阻害するために、半導体基板の露出面を、例えばイオン衝撃によって、アモルファス化する。活性化およびポリシリコン再成長のためのサーマルバジェットが低いことは、ソース/ドレイン領域における急峻なドーピングプロファイルを確実にするために好ましい。結果として、ゲート電極の上部(10b)は、アモルファスのままである。ポリシリコンの下部を用いて低抵抗の接点を作成するために、ゲート電極の上部を除去する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】特性を十分に向上することができる半導体装置およびその製造方法を提供する。

【解決手段】MOSFET30は、SiC膜11を備えている。SiC膜11はその表面にファセット形成層11aを有しており、ファセット形成層11aのファセットの一周期の長さP1は100nm以上であり、ファセット形成層11aをチャネル16としている。また、MOSFET30の製造方法は、SiC膜11を形成する工程と、SiC膜11の表面にSiを供給した状態で、SiC膜11を熱処理する熱処理工程と、熱処理工程によってSiC膜11の表面に得られたファセットをチャネル16とする工程とを備えている。

(もっと読む)

超格子誘電界面層を有する半導体素子

半導体素子は、半導体基板、及びその半導体基板に隣接する少なくとも1の活性素子を有して良い。その少なくとも1の活性素子は、電極層、その電極層の下に存在し、かつその電極と接する高誘電率誘電層、及びその高誘電率誘電層の下に存在し、かつその高誘電率誘電層と接する超格子を有して良い。その超格子は、各々が複数の層からなる複数の群を積層した状態で有して良い。超格子の複数の層からなる群の各々は、基礎となる半導体部分を画定する、複数の積層された基礎となる半導体分子層、及び隣接する基礎となる半導体部分の結晶格子の内部に束縛された少なくとも1の非半導体分子層を有して良い。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 シリサイドがサイドウォールの下側に形成されないようにすることにより、当該シリサイド起因の接合リーク電流等の電気特性の不良の発生を低減するための半導体装置及びその製造方法を提供する。

【解決手段】 サイドウォールが形成されている半導体基板の上に制御膜を形成した後、シリサイドを形成するための活性化領域をイオン注入法により形成する。その後、制御膜を除去し、金属膜を形成し、熱処理してシリサイドを活性化領域に形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 トレンチ内へ埋め込んだ絶縁膜を所望のテーパー角度でエッチバックして平坦化できる半導体装置の製造方法を提供する。

【解決手段】 HTO膜109をp型半導体基板1の主面までエッチングするエッチング工程では、第1のエッチング工程として、熱酸化膜上のHTO膜109を、テーパー角度が78°となるように、CHF3:CF4を2:1としたエッチング条件で、その膜厚の半分までドライエッチングする。その後、残り半分のHTO膜109を、テーパー角度が26°となる23℃のBHF63Uで7分40秒ウエットエッチングする第2のエッチング工程を実施する。これにより、所望のテーパー角度が実現できる。

(もっと読む)

熱処理方法及び半導体装置の製造方法

【課題】結晶欠陥を抑制して熱処理することが可能な熱処理装置を提供する。

【解決手段】半導体基板1上に、半導体基板1より小さな屈折率の透光膜14を形成し、半導体基板1を300℃以上、且つ600℃以下の温度に加熱し、透光膜14を通して半導体基板1表面を0.1m秒〜100m秒のパルス幅の光を照射することを含み、透光膜14の膜厚が、光のピーク波長と、透光膜14の屈折率とで規定される。

(もっと読む)

ダイヤモンド電界効果トランジスタ及びその製造方法

【課題】 絶縁耐性が優れたダイヤモンド電界効果トランジスタ及びその製造方法を提供する。

【解決手段】 ダイヤモンド基板1上に、夫々ソース領域及びドレイン領域となる低抵抗ダイヤモンド層2a及び2bを局所的に形成し、これら間及び相互に対向する端部上に、アンドープダイヤモンド又はBが低濃度でドープされたダイヤモンドからなる高抵抗ダイヤモンド層3を形成する。また、低抵抗ダイヤモンド層2a及び2b上に、夫々ソース電極5及びドレイン電極6を形成し、高抵抗ダイヤモンド層3上に、ゲート絶縁膜4を介してゲート電極7を形成する。このとき、ゲート絶縁膜4は、酸化シリコン層、窒化アルミニウム層、アルミナ層、ダイヤモンド状炭素層、窒化シリコン層、ジルコニア層、チタン酸ストロンチウム層、チタン酸バリウム層及びサイアロン層からなる群から選択された2種以上の層を積層した積層膜とする。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の上昇や漏れ電流の増加を抑えつつ、微細化に伴う短チャネル効果を効果的に抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上には、ゲート絶縁膜2を介してゲート電極3が形成されており、ゲート電極3の側壁にはサイドウォール絶縁膜5が形成されている。サイドウォール絶縁膜5の直下の半導体基板1には、エクステンション領域6が形成されており、エクステンション領域6の外側には深いソース・ドレイン領域7が形成されている。ソース・ドレイン領域7の内側であって、ソース・ドレイン領域7と半導体基板1との界面に、拡散抑制膜8が形成されている。拡散抑制膜8は、例えば酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜からなる。拡散抑制膜8により、ソース・ドレイン領域7中の不純物の横方向拡散が抑制される。

(もっと読む)

ゲート及びチャネル内に歪を誘起させてCMOSトランジスタの性能を向上させる方法

【課題】 ゲート内の応力を調節することによってトランジスタ・チャネル内に歪を誘起させること。

【解決手段】 相補型金属酸化物半導体トランジスタを製造する方法は、異なる型のトランジスタ、例えばN型金属酸化物半導体(NMOS)トランジスタ及びP型金属酸化物半導体(PMOS)トランジスタ(第1及び第2型トランジスタ)を基板(12)上に形成する。この方法は、これらのNMOSトランジスタ及びPMOSトランジスタ上に任意の酸化物層を形成し、次いでNMOSトランジスタ及びPMOSトランジスタを硬い材料(50)、例えば窒化ケイ素層で覆う。この後、この方法は、この硬い材料層(50)の一部をパターン形成し、硬い材料層がNMOSトランジスタ上にのみ残るようにする。次に、この方法は、NMOSトランジスタを加熱し(178、204)、次いで硬い材料層(50)の残存部分を除去する。PMOSトランジスタ(PFET)のゲート(20)又はチャネル領域内に応力を生じさせることなく、NMOSトランジスタ(NFET)のゲート(22)内に圧縮応力、チャネル領域内に引張応力(70)を生じさせることによって、この方法は、PFETの性能を低下させることなく、NFETの性能を改善する。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】 浅いソース,ドレイン接合位置を保ちつつ接合リークを低く抑えることができ、且つコンタクト抵抗も低く保つ。

【解決手段】 シリコン基板101上にゲート絶縁膜200を介して形成されたゲート電極300と、ゲート電極300下のチャネル領域を挟んで基板101の表面部に形成されたソース,ドレインのエクステンション領域131,132と、エクステンション領域131,132の外側に形成されたソース,ドレイン領域141,142と、ソース,ドレイン領域141,142上に形成されたシリサイド層631,632とを備えた電界効果型トランジスタであって、シリサイド層631,632のチャネル領域側の端部近傍に、AsとOをそれぞれ1019cm-3以上の濃度で含む拡散抑制領域151,152が形成されている。

(もっと読む)

半導体装置とその製造方法

【課題】 プラズマ処理によりシリコン表面に形成される、SiCを含む変質層を、シリコン表面の侵食を最小限に抑止しながら除去する。

【解決手段】 前記変質層を、酸素ラジカルに、前記半導体表面のSi原子に結合してSi原子と酸素原子との間の二重結合の形成を阻害するような元素の活性種を添加して改質し、形成された改質層をウェットエッチングにより除去する。

(もっと読む)

21 - 40 / 41

[ Back to top ]