Fターム[5F140BK39]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極形成後の処理 (1,157) | エッチング (743)

Fターム[5F140BK39]に分類される特許

161 - 180 / 743

高応力下にあるチャネルを有するMOSデバイスを製造するための方法

【解決手段】

シリコン含有基板を備えた半導体デバイスを形成するための方法が提供される。1つの例示的な方法は、シリコン含有基板を覆う多結晶シリコン層を堆積させることと、多結晶シリコン層をアモルファス化することと、アモルファス化された多結晶シリコン層をエッチングしてゲート電極を形成することと、ゲート電極を覆う応力誘起層を堆積させることと、シリコン含有基板を焼鈍してゲート電極を再結晶化することと、応力誘起層を除去することと、ゲート電極をエッチングマスクとして用いて基板内へ凹部をエッチングすることと、凹部内に不純物ドープのシリコン含有領域をエピタキシャル成長させることとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】オフセットスペーサが除去されることを防止する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13Aと、ゲート絶縁膜上に形成されたゲート電極15Aと、ゲート電極の側面上に形成されたオフセットスペーサ17Aと、ゲート電極の側面上にオフセットスペーサを介して形成された断面形状がL字状の内側サイドウォール19と、ゲート電極15A、オフセットスペーサ17A、内側サイドウォール19、及び半導体領域10xにおける内側サイドウォール19の外側方に位置する領域を覆うように形成された絶縁膜24とを備え、オフセットスペーサ17Aは、ゲート電極の側面上に形成された内側オフセットスペーサ16と、ゲート電極の側面上に内側オフセットスペーサ16を覆うように形成された外側オフセットスペーサ17とを有し、外側オフセットスペーサは、内側オフセットスペーサの上端及び外側面に接して形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高誘電率膜をゲート絶縁膜として用いたCISトランジスタの信頼性を向上する。

【解決手段】基板1の主面には、素子分離領域2によって互いに絶縁分離されたpMISトランジスタの活性領域およびnMISトランジスタの活性領域が設けられている。素子分離領域2に係るようにnMISトランジスタの活性領域上にnMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜5が設けられており、そのハフニウム系酸化膜5と素子分離領域2上で接触し、pMISトランジスタの活性領域上にハフニウム系酸化膜5と異なる材料から構成されるpMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜9が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造歩留まりを向上させる。

【解決手段】

半導体基板1の主面にゲート絶縁膜用の絶縁膜を形成する。それから、プラズマ処理装置51の処理室51a内で、半導体基板1の主面のゲート絶縁膜用の絶縁膜をプラズマ窒化する。その後、プラズマ処理装置51から半導体基板1をフープ31内に移送し、フープ31をベイステーションBSに移動させてそこで待機させて半導体基板1を保管する。ベイステーションBSに待機している間、半導体基板1を保管しているフープ31内に、フープ31に設けられた第1の呼吸口から窒素ガスを供給し、フープ31に設けられた第2の呼吸口からフープ31内の窒素ガスを排出する。その後、フープ31を熱処理装置52に移動させて、半導体基板1を熱処理装置52の処理室内に搬入して熱処理する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】金属微粒子と半導体基板の反応を利用して電極を形成する、高性能な半導体装置の製造方法およびグレイン粒径の小さい電極を有する高性能な半導体装置を提供する。

【解決手段】直径20nm以下の金属微粒子を溶媒中に分散した溶液を、半導体基板上に塗布する工程と、溶媒を蒸発させる工程と、金属微粒子と半導体基板を反応させ、半導体基板表面に金属半導体化合物薄膜を形成する工程とを有することを特徴とする半導体装置の製造方法。半導体基板上に金属半導体化合物薄膜を有する半導体装置であって、金属半導体化合物薄膜は膜厚方向に単グレインで形成され、単グレインの粒径が40nm以下であることを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、半導体装置及びその製造方法に関し、特に非シリサイド領域において接合リークを抑制することにより、歩留まりの向上を図る半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極11と、半導体基板に形成されたソース領域8b及びドレイン領域8aとを有する半導体装置において、ドレイン領域8aの表面は、シリサイド膜が形成されたシリサイド領域20と、シリサイド領域20に隣接して形成されたシリサイド膜が形成されていない非シリサイド領域21とを具備し、シリサイド領域20は、100μm2以上の面積を有し、非シリサイド領域21は、シリサイド領域20の面積以上の面積を有することを特徴とする。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース・ドレインの寄生抵抗の低減及び短チャネル効果の抑制と共にリーク電流の低減をはかる。

【解決手段】チャネル領域を構成する第1の半導体領域12と、第1の半導体領域12上にゲート絶縁膜15を介して形成されたゲート電極16と、第1の半導体領域12をチャネル長方向から挟んで形成された金属シリサイドからなるソース・ドレイン電極14と、を具備してなる電界効果トランジスタであって、ソース・ドレイン電極14は、チャネル領域の平均的な不純物濃度よりも高い不純物濃度を有し、且つチャネル領域との界面又は界面近傍に前記不純物濃度のピークを持ち、チャネル領域は、ソース・ドレイン電極との界面又は界面近傍に前記不純物濃度のピークを持つ。

(もっと読む)

半導体装置の製造方法

【課題】Geを含有する半導体基板に効果的な洗浄方法が適用された半導体装置の製造方法を提供する。

【解決手段】Geを含有する半導体基板を、HClガス、HBrガスまたはHIガスの少なくとも一種を含むハロゲン化ガスで洗浄処理を行うことを特徴とする半導体装置の製造方法。Geを含有する半導体基板を、75℃以上110℃以下のHCl溶液で洗浄処理を行うことを特徴とする半導体装置の製造方法。例えば、MISFETのゲート絶縁膜の前処理、ソース・ドレイン電極形成の前処理、コンタクトの金属プラグ形成の前処理に適用される。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】セルフアラインコンタクトを形成する際に、エクステンション領域及びソースドレイン領域におけるシリサイド化されていない部分とコンタクトとが接触することがない半導体装置を実現できるようにする。

【解決手段】半導体装置は、ゲート電極13の側壁の上から半導体基板11の上に亘って形成されたL字サイドウォール14と、層間絶縁膜22と、L字サイドウォール14に覆われたエクステンション領域16と、一部がL字サイドウォール14に覆われたソースドレイン領域15と、ソースドレイン領域15におけるL字サイドウォール14に覆われていない部分に形成されたシリサイド層17と、シリサイド層17と接続されたコンタクト17とを備えている。L字サイドウォール14は、層間絶縁膜22と比べてエッチングレートが小さい絶縁材料により形成されている。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板10に形成されたシリコンを主成分とするソース・ドレイン拡散層3上、および半導体基板に形成されソース・ドレイン拡散層に隣接する素子分離絶縁膜の上に、金属を堆積して金属膜を形成し、第1の加熱温度の第1の加熱処理によりソース・ドレイン拡散層のシリコンとソース・ドレイン拡散層上の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜106を形成し、シリサイド膜を酸化させないようにして、素子分離絶縁膜の上の金属膜の少なくとも表面を選択的に酸化して、金属酸化膜105を形成し、第1の加熱温度よりも高い第2の加熱温度の第2の加熱処理によりシリサイド膜のシリコンの濃度を増加させ、素子分離絶縁膜上の金属酸化膜および金属膜の未反応部分を選択的に除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度の向上を実現し得る半導体装置及びその製造方法を提供する。

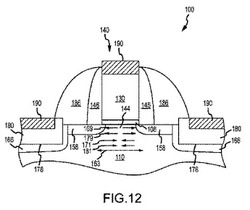

【解決手段】半導体基板10に形成されたチャネル領域44上にゲート絶縁膜18を介して形成されたゲート電極20bと、ゲート電極の側壁部分に形成されたサイドウォール絶縁膜26と、ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層38と、ソース/ドレイン拡散層に埋め込まれ、半導体基板と格子定数が異なる半導体層52とを有し、半導体層は、半導体基板のうちのサイドウォール絶縁膜の下方領域に食い込むように形成された第1の突出部54と、半導体基板のうちのサイドウォール絶縁膜の直下の部分に食い込むように形成された第2の突出部56とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】金属ゲートを形成した後に形成される絶縁膜中の水素の影響を抑制して、しきい値電圧Vthを所望の値(例えば0.3V)以下にすることを可能にする。

【解決手段】半導体基板11上に第1絶縁膜41が形成され、第1絶縁膜41に溝部42が形成され、溝部42の第1絶縁膜41側の半導体基板11上にサイドウォールスペーサ31が形成され、溝部42内にゲート絶縁膜21を介してゲート電極22が形成され、ゲート電極22の両側の半導体基板11にエクステンション領域23,24を介してソース・ドレイン領域25,26が形成され、第1絶縁膜41上にゲート電極22上を被覆する第2絶縁膜43を有し、サイドウォールスペーサ31は水素の通過を阻止する絶縁膜からなり、ゲート電極22上に水素の通過を阻止する水素バリア膜33が形成され、水素バリア膜33はゲート電極22上の周囲でサイドウォールスペーサ31と接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】横型絶縁ゲートトランジスタ素子を備え、オン抵抗の増加を抑制しつつ体格を小型化することのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体層に構成されたLDMOS素子と、半導体層の主表面上に形成された絶縁膜を同一表面から貫通するコンタクプラグとしての、ソース領域とベースコンタクト領域とに接続された第1コンタクトプラグと、を備えた半導体装置であって、ベースコンタクト領域が、半導体層の主表面に略垂直な方向においてソース領域よりも主表面に対して下方で、半導体層の主表面に沿う方向においてソース領域と少なくとも一部が重なる位置に形成されている。そして、第1コンタクトプラグが、絶縁膜及びソース領域を貫通しつつベースコンタクト領域まで延設されている。

(もっと読む)

半導体装置の製造方法

【課題】ウエル近接効果の発生を抑制することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法においては、半導体基板SUBの主表面上に反射防止膜BKが形成される。その反射防止膜BK上に、パターン端部において半導体基板SUB側に向かって広がるような傾斜を有するレジストパターンPR1が形成される。そのレジストパターンPR1をマスクとして半導体基板SUBの主表面にイオンが注入される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中のシリコン混晶層の形成を制御することにより、キャップ膜の形成を不要とし、シリサイド層を精度良く形成する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第2導電型のポリシリコン膜28Aとポリシリコン膜28A上に形成された炭素を含む第1のシリコン混晶層25とを有するゲート電極25Aと、第1のシリコン混晶層25上に形成された第1のシリサイド層29と、半導体領域10xにおけるゲート電極25Aの側方下の領域に形成された第2導電型の不純物拡散領域24と、不純物拡散領域24の上部領域に形成された炭素を含む第2のシリコン混晶層26と、第2のシリコン混晶層26上に形成された第2のシリサイド層30とを備えている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作不良を防止し、半導体装置の製造工程を簡略化する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1と、半導体基板1内に設けられる一対の不純物拡散層2A,2Bと、不純物拡散層2A,2B間の半導体基板上に設けられるゲート絶縁膜3と、ゲート絶縁膜3上に設けられるゲート電極4と、一対の不純物拡散層2A,2B上にそれぞれ設けられる2つのコンタクト5A,5Bとを具備し、ゲート電極4とコンタクト5A,5Bは、同じ材料から構成され、ゲート電極4上端およびコンタクト5A,5B上端は、半導体基板1表面からの高さが一致する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】オン抵抗の増加を抑制しつつ耐圧向上を図ることができるMIS型トランジスタの提供。

【解決手段】ゲート絶縁膜6と、ゲート絶縁膜6上に形成されたゲート電極7と、ゲート電極7の一方の側に形成されたソース領域80aと、ゲート電極7の他方の側に形成され一端がゲート電極7の下方に入り込み形成された第2の不純物濃度を有する第1ドレイン領域5と、第1ドレイン領域5内にゲート電極7から第1距離だけ離間させて形成され第2の不純物濃度よりも不純物濃度が高い第3の不純物濃度を有する第2ドレイン領域10aと、第2ドレイン領域10a内にゲート電極7から第1距離より大きい第2距離だけ離間させて形成され第3の不純物濃度よりも不純物濃度が高い第4の不純物濃度を有する第3ドレイン領域12aと、ゲート電極7上、ソース領域11a上、第2ドレイン領域10a及び第3ドレイン領域12a上に形成されたシリサイド層13とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】

歪み技術を用いたMOSトランジスタにおいて、リーク電流を抑える。

【解決手段】

半導体装置は、第1の格子定数を有する第1の半導体で形成された半導体基板に形成され、活性領域を画定する素子分離領域と、活性領域の中間位置を横断して、半導体基板上方にゲート絶縁膜を介して形成されたゲート電極と、ゲート電極側壁上に形成されたサイドウォールスペーサとを含むゲート電極構造と、ゲート電極構造両側の活性領域と素子分離領域との界面が半導体基板の表面に表出した境界の一部を覆って半導体基板の表面上方に配置された他のゲート電極構造であって、他のゲート電極と該他のゲート電極の側壁上に形成された他のサイドウォールスペーサとを含む他のゲート電極構造と、ゲート電極構造と他のゲート電極構造の間の活性領域をエッチして形成されたリセスと、リセスを埋めてエピタキシャル成長され、第1の格子定数と異なる第2の格子定数を有する第2の半導体で形成された半導体層と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】 残留有機物の除去、及びゲート絶縁膜のダメージ回復を目的として、酸化性雰囲気でRTAを行うと、ゲート絶縁膜の端面から内側に向かってバーズビークが発生してしまう。

【解決手段】 (a)半導体基板(10)の上に絶縁膜(14)を形成する。(b)絶縁膜の上に導電膜(15)を形成する。(c)導電膜及び絶縁膜をパターニングする。(d)工程(c)の後、半導体基板の少なくとも表層部を加熱する。工程(d)において、半導体基板の表層部の温度が第1の温度に到達するまでの少なくとも一部の第1の期間は、半導体基板が配置された空間に酸素ガスと不活性ガスとを供給しておき、第1の温度を超えた後は、酸素ガスの供給を停止させておく。

(もっと読む)

161 - 180 / 743

[ Back to top ]