Fターム[5F140BK39]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極形成後の処理 (1,157) | エッチング (743)

Fターム[5F140BK39]に分類される特許

81 - 100 / 743

半導体装置およびその製造方法

【課題】シリサイド層とSi層との界面における抵抗が低いMOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成された、チャネル移動度に実質的な影響を与えないSiGe層15と、SiGe層15上に形成されたSi層16と、半導体基板2、SiGe層15、およびSi層16内のゲート電極12の両側に形成されたn型ソース・ドレイン領域19と、Si層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】MIPS構造等のゲート電極と同時形成が可能であり且つ抵抗が高い抵抗素子を有する半導体装置及びその製造方法を提供する。

【解決手段】基板上に金属含有膜108及びポリシリコン膜109を順次形成する工程と、前記金属含有膜及び前記ポリシリコン膜を抵抗素子形状にパターニングする工程と、前記金属含有膜の少なくとも一部分を除去することにより、前記ポリシリコン膜の下に中空領域119を形成する工程とを備えている。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧で、特性の優れた半導体装置を提供する。

【解決手段】素子分離領域STIと、ウェルPWと、活性領域を横断するゲート電極Gと、ゲート電極の一方の側からゲート電極下方に入り込んで形成された低濃度ドレイン領域LDDと、ゲート電極の他方の側からゲート電極下方に入り込み、低濃度ドレイン領域とオーバーラップし、低濃度ドレイン領域より浅い、チャネル領域CHと、ゲート電極の他方の側に形成されたソース領域Snと、ゲート領域の一方の側に、ゲート電極から離間したドレイン領域Dnと、を有し、ゲート電極と高濃度ドレイン領域Dnとの間の中間領域の実効不純物濃度は、オーバーラップ領域の不純物濃度より高い。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置の製造方法

【課題】 所望の極浅拡散層を形成することが可能な半導体製造方法を提供する。

【解決手段】

シリコン基板1にイオン注入するイオン注入工程と、イオン注入工程の後に、シリコン

基板1にマイクロ波を照射するマイクロ波照射工程と、マイクロ波照射工程の後に、シリ

コン基板1を熱処理装置に移し、シリコン基板に0.1ミリ以上100m秒以下のパルス

幅の光を照射することにより、シリコン基板1を熱処理する熱処理工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

半導体装置とその製造方法

【課題】

高温、長時間のアニールを必要とすることなく、低いオン抵抗を実現可能な高耐圧MOSトランジスタを含む半導体装置を提供する。

【解決手段】

半導体基板の高耐圧トランジスタ用第1導電型領域上にゲート電極を形成し、ゲート電極のドレイン側部分及びドレイン領域を覆う第1のマスクをイオン注入マスクとして、ゲート電極を貫通する加速エネルギで第1導電型の不純物イオンを注入して、ソース領域で深く、ゲート電極下方で浅いチャネルドーズ領域を形成し、ゲート電極のドレイン側部分及びドレイン領域を覆う第2のマスク及びゲート電極をイオン注入マスクとして第2導電型の不純物をイオン注入してソースエクステンション領域を形成し、半導体装置を製造する。

(もっと読む)

半導体装置

【課題】駆動電力の高いフィン型のトランジスタを提供する。

【解決手段】所定の間隔で配置され、それぞれの中央部がチャネル領域、その両側部がソース/ドレイン領域となるフィン状の第1の半導体11層及び第2の半導体層11と、第1の半導体層11及び第2の半導体層11それぞれのチャネル領域の両側面にゲート絶縁膜12を介して形成されたゲート電極13と、第1の半導体層11のソース/ドレイン領域と第2の半導体層11のソース/ドレイン領域との間の溝を埋め込むように形成された絶縁膜19と、第1の半導体層11のソース/ドレイン領域及び第2の半導体層11のソース/ドレイン領域の絶縁膜19で覆われていない側面にそれぞれ形成されたシリサイド16とを備える。

(もっと読む)

トレンチDMOSトランジスタの製造方法

トレンチDMOSトランジスタの製造方法であって、半導体基板上に酸化物層及びバリア層を形成するステップと、トレンチを形成するために、酸化物層及び半導体基板をエッチングするステップと、トレンチの内壁にゲート酸化物層を形成するステップと、バリア層上にポリシリコン層を形成し、トレンチを充填するステップと、トレンチゲートを形成するために、ポリシリコン層をエッチバックするステップと、バリア層及び酸化物層を除去するステップと、拡散層を形成するために、トレンチゲートの両側の半導体基板内にイオンを注入するステップと、拡散層上をフォトレジスト層で覆い、ソース/ドレイン配置を定義するステップと、拡散層内にイオンを注入するステップと、トレンチゲートの両側に側壁を形成するステップと、拡散層及びトレンチゲート上に金属シリサイド層を形成するステップとを含む。低コスト及び改善された製造効率を伴う効果的な結果が達成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の下部からゲート電極の形成されていない基板上の領域に斜め方向のイオン注入を行って形成される不純物拡散領域を有する半導体装置において、半導体装置のサイズを従来に比して縮小化することができる半導体装置を提供する。

【解決手段】N型半導体層13の表面に形成されるP型のベース領域21と、ベース領域21内に形成されるP+型ソース領域22およびN+型ソース領域23を有するソース領域と、N型半導体層13の表面にベース領域21から離れて形成されるN+型のドレイン領域26と、ソース領域とドレイン領域26との間にゲート絶縁膜41を介して形成されるゲート電極42と、ドレイン領域26からゲート電極42の下部にかけて、ドレイン領域26に隣接して形成されるN型のドリフト領域と、を備え、ゲート電極42とゲート絶縁膜41との積層体のソース領域側側面の高さが、ドレイン領域側側面の高さよりも高く形成される。

(もっと読む)

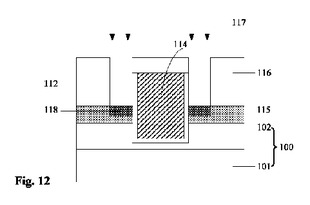

埋め込みストレッサを有する高性能FETを形成するための方法および構造

【課題】 高性能の半導体構造およびかかる構造を製造する方法を提供する。

【解決手段】 半導体構造は、半導体基板12の上面14上に位置する、例えばFETのような少なくとも1つのゲート・スタック18を含む。構造は更に、少なくとも1つのゲート・スタックのチャネル40上にひずみを誘発する第1のエピタキシ半導体材料34を含む。第1のエピタキシ半導体材料は、少なくとも1つのゲート・スタックの対向側に存在する基板内の1対のくぼみ領域28の実質的に内部で少なくとも1つのゲート・スタックの設置場所に位置する。くぼみ領域の各々において第1のエピタキシ半導体材料の上面内に拡散拡張領域38が位置する。構造は更に、拡散拡張領域の上面上に位置する第2のエピタキシ半導体材料36を含む。第2のエピタキシ半導体材料は、第1のエピタキシ半導体材料よりも高いドーパント濃度を有する。

(もっと読む)

半導体装置

【課題】 半導体装置に関し、ソース・ドレイン領域を実効的に埋込Si混晶層で構成する際の電気的特性を向上する

【解決手段】 一導電型シリコン基体と、一導電型シリコン基体上に設けたゲート絶縁膜と、ゲート絶縁膜の上に設けたゲート電極とゲート電極の両側の一導電型シリコン基体に設けた逆導電型エクステンション領域と、逆導電型エクステンション領域に接するとともに、一導電型シリコン基体に形成された凹部に埋め込まれた逆導電型Si混晶層とを備えた半導体装置であって、逆導電型Si混晶層が、第1不純物濃度Si混晶層/第2不純物濃度Si混晶層/第3不純物濃度Si混晶層を有し、第2不純物濃度を第1不純物濃度及び第3不純物濃度よりも高くする。

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層と、下地半導体層上に第1窒化物半導体層、第2窒化物半導体層、および第3窒化物半導体層が順次積層された窒化物半導体積層体と、ソース電極およびドレイン電極と、第2窒化物半導体層および第3窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域の内面および窒化物半導体積層体の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを含み、絶縁膜に接する第1窒化物半導体層の上面と、第2窒化物半導体層に接する第1窒化物半導体層の上面とに段差がないことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】p型MISトランジスタのゲート絶縁膜の酸化膜換算膜厚の厚膜化を抑制しつつ、p型MISトランジスタの実効仕事関数を増加させて、低閾値電圧を有するn型,p型MISトランジスタを実現する。

【解決手段】半導体装置は、第1,第2のMISトランジスタnTr,pTrを備えている。第1のMISトランジスタnTrは、第1の活性領域10a上に形成され、第1の高誘電率膜14Xaを有する第1のゲート絶縁膜14Aと、第1のゲート電極18Aとを備えている。第2のMISトランジスタpTrは、第2の活性領域10b上に形成され、第2の高誘電率膜14xを有する第2のゲート絶縁膜14Bと、第2のゲート電極18Bとを備えている。第2の高誘電率膜14xは、第1の調整用金属を含む。第1の高誘電率膜14Xaは、第2の高誘電率膜14xよりも窒素濃度が高く、且つ、第1の調整用金属を含まない。

(もっと読む)

バンド設計超格子を有する半導体装置

【課題】例えば大きな電荷キャリア移動度を有する半導体装置を提供する。

【解決手段】半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】ソース/ドレイン領域のPN接合部とコンタクト間のリーク電流を抑制する。

【解決手段】半導体基板(1)と、半導体基板(1)に形成されたSTI(Shallow Trench Isolation)構造(2)と、半導体基板(1)に形成され、STI構造(2)に隣接する拡散領域(12)と、層間絶縁膜(15)を貫通して拡散領域(12)とSTI構造(2)とに到達する接続コンタクト(20)と、拡散領域(12)の側面と拡散領域(12)の下の半導体基板(1)の側面に形成され、接続コンタクト(20)と拡散領域(12)の側面とを電気的に絶縁し、かつ、接続コンタクト(20)と半導体基板(1)の側面とを電気的に絶縁する酸化膜(19)とを具備する半導体装置を構成する。その半導体装置では、STI素子分離とソース/ドレイン領域のPN接合部分の間のみに選択的に絶縁膜(酸化膜)を形成している。

(もっと読む)

半導体装置とその製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上のコンタクトと柱状半導体層の周囲に形成されるゲート電極のショートの抑制。

【解決手段】上方に平面状半導体層及び該平面状半導体層上の柱状半導体層が形成された基板に対して、柱状半導体層の上部に第2のドレイン/ソース領域を形成し、コンタクトストッパー膜を成膜し、コンタクト層間膜を成膜し、第2のドレイン/ソース領域上にコンタクトを形成し、ここでコンタクトの形成は、コンタクトのパターンを形成し、コンタクトのパターンを用いてコンタクト層間膜をコンタクトストッパー膜までエッチングすることにより、コンタクト用のコンタクト孔を形成し、コンタクト用のコンタクト孔の底部に残存するコンタクトストッパー膜をエッチングにより除去することを含み、コンタクト用のコンタクト孔の底面の基板への投影面は、柱状半導体層の上面及び側面に形成されたコンタクトストッパー膜の基板への投影形状の外周内に位置する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】拡散層とゲート電極との少なくとも1つの上に耐熱性が向上したNiSi膜が形成された半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Si基板200と、Si基板200内に形成された拡散層10と、Si基板200上にSiを用いて形成されたゲート電極20との少なくとも1つと、前記拡散層10と前記ゲート電極20との少なくとも1つ上に接触して形成されたP元素を含有したNiSi膜40,42と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、高誘電率膜を用いた相補型トランジスタの実効仕事関数を調整して適切なしきい値電圧を実現する際に、エッチング工程数を低減するとともに、エッチングダメージの発生を回避する。

【解決手段】 nチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第1のゲート絶縁膜と第1金属ゲート電極との間にアルミニウム膜を設けるとともに、pチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第2ゲート絶縁膜と第2金属ゲート電極との間に酸化アルミニウム膜を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、pチャネルトランジスタのチャネル領域には圧縮歪を、nチャネルトランジスタのチャネル領域には引っ張り歪をそれぞれ効果的に印加できる新しい歪技術を提供する。

【解決手段】pチャネルトランジスタ105のゲート電極は、引っ張り内部応力を持つpチャネルメタル電極110を有する。nチャネルトランジスタ106のゲート電極は、圧縮内部応力を持つnチャネルメタル電極116を有する。

(もっと読む)

81 - 100 / 743

[ Back to top ]