Fターム[5F140BK39]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極形成後の処理 (1,157) | エッチング (743)

Fターム[5F140BK39]に分類される特許

101 - 120 / 743

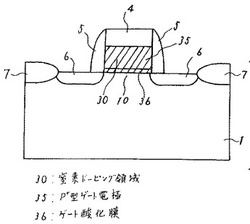

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体装置の製造方法及びスパッタリング装置

【課題】半導体基板にシリサイド形成用の金属膜を形成する時に、ゲート絶縁膜にダメージが加わることを抑制する。

【解決手段】このスパッタリング装置は、チャンバ101、ウェハステージ102、リングチャック104、金属ターゲット105、防着シールド107、マグネット108、コリメータ109、並びに直流電源110,120を備えている。直流電源110は、コリメータ109に負電圧のみを印加するために設けられている。コリメータ109に印加される負電圧は、金属ターゲット105に印加される電圧より低電圧、例えば−70V以上−50V以下である。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高品質な特性を有する電界効果トランジスタ及びその方法を提供する。

【解決手段】素子分離領域106間のソース/ドレイン領域114、及びポケット領域116を含んでいる半導体基板102と、素子分離領域間の半導体基板の上面のトレンチ110内にあって、(100)面を有する底面及び上面と、2つ以上の平面を有する側面とを有するシリコンゲルマニウム層112と、ゲート絶縁層120、ゲート電極122、及びサイドスペーサ128を含むシリコンゲルマニウム層上のゲート構造と、ゲート構造によって覆われていないシリコンゲルマニウム層及び半導体基板の上部分上のメタルシリサイド124とを備え、シリコンゲルマニウム層は、チャネル長方向において、ゲート構造の下で側面を有していない。

(もっと読む)

不純物活性化方法、半導体装置の製造方法

【課題】低いシート抵抗を得る不純物活性化方法、および、ソース・ドレイン拡張部を均一な深さで再現性よく形成する製造方法を提供。

【解決手段】半導体基板21において半導体基板21よりも不純物濃度が高いボロンイオン注入層43が形成されており、ボロンイオン注入層43にパルス幅が10〜1000フェムト秒のパルスレーザー光を照射して、ボロンイオン注入層43を活性化させる。パルスレーザー光におけるパルス幅、レーザーフルーエンスおよび照射パルス数を含む照射条件を変更することにより、パルスレーザー光照射後のボロンイオン注入層43のシート抵抗を制御する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、極めて高い歩留まりでゲート電極について均一で十分なフル・シリサイド化を確実に実現する。

【解決手段】ゲート電極104a,104b及びソース/ドレイン領域107a,107bのNiシリサイド化を行うに際して、1回目のNiシリサイド化の後に1回目のmsecアニール処理であるフラッシュランプアニール処理を行い、2回目のNiシリサイド化、更には必要であれば2回目のフラッシュランプアニール処理を行って、ソース/ドレイン領域107a,107b上には1回目のフラッシュランプアニール処理で形成されたNiSi層111bを維持した状態で、フル・シリサイドゲート電極115a,115bを形成する。

(もっと読む)

半導体装置の製造方法

【課題】微細化が進んでも適切な歪を生じさせることができる半導体装置の製造方法を提供する。

【解決手段】nチャネルトランジスタ形成予定領域51nを覆う部分を残しながら絶縁膜6のエッチバックを行うことにより、pチャネルトランジスタ形成予定領域51p内のゲート電極4の側方にサイドウォール6aを形成する。サイドウォール6aをマスクとして半導体基板1の表面にp型不純物を導入してp型不純物導入領域8pを形成し、サイドウォール6aをマスクとしてp型不純物導入領域8pの表面に溝9を形成する。溝9内にSiGe層10を成長させる。絶縁膜6のエッチバックを行うことにより、nチャネルトランジスタ形成予定領域51n内のゲート電極4の側方にサイドウォールを形成し、nチャネルトランジスタ形成予定領域51n内において、このサイドウォールをマスクとして半導体基板1の表面にn型不純物を導入してn型不純物導入領域を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域にエピタキシャル結晶を含み、エピタキシャル結晶上の金属シリサイドに起因する接合リークの発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、ファセット面13fを有するエピタキシャル結晶層13を有するMISFET10と、MISFET10を他の素子から電気的に分離し、上層3aのゲート電極12側の端部の水平方向の位置が下層3bのそれよりもゲート電極12に近く、上層3aの一部がファセット面13fに接する素子分離絶縁膜3と、エピタキシャル結晶層13の上面、およびファセット面13fの上層3aとの接触部よりも上側の領域に形成されたシリサイド層18と、を有する。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】p型ソースドレイン領域内にシリコン混晶層が形成されていると、N型MISトランジスタのキャリア移動度が低下する虞があった。

【解決手段】活性領域10aと活性領域10bとが素子分離領域11により分離されており、活性領域10a上には第1導電型の第1のトランジスタが設けられており、活性領域10b上には第2導電型の第2のトランジスタが設けられている。活性領域10b内には、第1の応力を有するシリコン混晶層21が設けられている。素子分離領域11のうち活性領域10aと活性領域10bとで挟まれた部分の上面には凹部22が設けられている。凹部23内には応力絶縁膜24が設けられており、応力絶縁膜24は第1の応力とは反対方向の第2の応力を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】PMISトランジスタのソースドレイン電極に高濃度のゲルマニウムを含むシリコンゲルマニウム層を用いても、シリコンゲルマニウム層に格子緩和を生じさせることなく、ソースドレイン電極の上部にシリコン層又は金属シリサイド層を形成できるようにする。

【解決手段】半導体装置は、n型半導体領域100の上にゲート絶縁膜101を介在させて形成されたゲート電極102と、その両側方に形成されたp型のソースドレイン電極150とを有している。ソースドレイン電極150は、n型半導体領域100に設けられた各リセス部100aに、その底部から少なくともチャネル領域の深さにまで形成されたシリコンゲルマニウム層111と、その上に形成され、炭素とシリコンゲルマニウム層のゲルマニウム濃度よりも低いゲルマニウムとを含むカーボンドープドシリコンゲルマニウム層112と、その上に形成された金属シリサイド層115とから構成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離構造の面積を増大させることなく、素子分離構造の表面の後退量を低減させる。

【解決手段】半導体基板11の表面よりも低い位置に埋め込み絶縁層12を埋め込み、埋め込み絶縁層12と材料の異なるキャップ絶縁層13を半導体基板11と埋め込み絶縁層12と間の段差12aの肩の部分にかからないようにして埋め込み絶縁層12上に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上にヒューズ素子を備える半導体装置において、ヒューズを切断しやすくし、かつヒューズ切断状態を確実に得る。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとヒューズ素子100を備える。ヒューズ素子100は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層34と、シリコン層34の上の少なくとも一部を覆うシリサイド層73と、からなる。

(もっと読む)

半導体装置の製造方法

【課題】所望のMOSトランジスタのみにチャネル領域に引っ張り応力を印加してキャリア移動度を向上させ、且つ、製造工程の複雑化を抑える。

【解決手段】シリコン基板10上にnMOSトランジスタのゲート絶縁膜13およびゲート電極14を非単結晶シリコンで形成し、ゲート電極14をマスクとして例えばAsやSb等の比較的質量数が大きい(質量数70以上)n型ドーパントを注入することで、nMOSトランジスタのソースドレイン領域を形成する。それにより、ゲート電極14は非晶質化する。そして、ゲート電極14が再結晶化する温度(約550℃)以下の温度条件でゲート電極14を覆うようにシリコン酸化膜40を形成し、その後1000℃程度の加熱処理を行う。それにより、ゲート電極14内に強い圧縮応力が残留すると共に、その下のチャネル領域には強い引っ張り応力が印加され、当該nMOSトランジスタのキャリア移動度は向上する。

(もっと読む)

半導体装置の製造方法

【課題】短いゲート長を加工可能にする半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法の一形態は、シリコン基板2上にシリコン酸化膜34を形成し、酸化膜34上に所定幅T1を有する多結晶シリコン膜35aを形成し、少なくとも多結晶シリコン膜35aの両側部を酸化し、所定幅T1よりも狭い幅を有する酸化膜34の部分を多結晶シリコン膜35aの下に残すように、酸化膜34を、多結晶シリコン膜35aの酸化された部分と共にエッチングし、酸化された部分がエッチングされた多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入し、多結晶シリコン膜35aの両側に側壁絶縁膜14を形成し、側壁絶縁膜14が形成された多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入する、工程を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 低いオン抵抗を維持しつつ、従来構成よりも更に耐圧低下を抑制したLDMOSトランジスタ及びその製造方法を提供する。

【解決手段】 P型基板1上に形成された、N型ウェル2と、ウェル2内に形成されたP型ボディ領域6と、ウェル2内においてボディ領域6よりも深い位置に形成されたP型の埋め込み拡散領域4と、ボディ領域6内に形成されたN型のソース領域9と、ウェル2内において、素子分離領域を介してボディ領域6と離間して形成したN型のドリフト領域7と、ドリフト領域7内に形成されたN型のドレイン領域10と、少なくとも前記ボディ領域9の一部上方、及びボディ領域9とドレイン領域10に挟まれた位置におけるウェル領域2の上方にわたってゲート絶縁膜を介して形成されたゲート電極7と、有し、ドリフト領域7並びにドレイン領域10が、ボディ領域6を取り囲むようにリング状に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ソース、ドレインの低抵抗化及び寄生容量の低減化のための構造、所望のゲート長、ソース、ドレイン形状、柱状半導体の直径が得られるSGTの製造方法を提供する。

【解決手段】第1の平面状半導体層上に第1の柱状半導体層を形成する工程と、第1の柱状半導体層の下部と第1の平面状半導体層に第1の第2導電型半導体層を形成する工程と、第1の柱状半導体層の底部及び第1の平面状半導体層上に第1の絶縁膜を形成する工程と、第1の柱状半導体層の周囲にゲート絶縁膜およびゲート電極を形成する工程と、ゲート電極の上部且つ第1の柱状半導体層の上部側壁と、ゲート電極の側壁に第2の絶縁膜をサイドウォール状に形成する工程と、第1の第2導電型半導体層と第2の第2導電型半導体層との間に第1導電型半導体層を形成する工程と、第1の第2導電型半導体層の上部表面と、第2の第2導電型半導体層の上部表面に金属と半導体の化合物を形成する工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

101 - 120 / 743

[ Back to top ]