Fターム[5F140CC04]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741) | SiO (1,517) | 不純物含有 (356)

Fターム[5F140CC04]の下位に属するFターム

Fターム[5F140CC04]に分類される特許

1 - 20 / 33

半導体装置

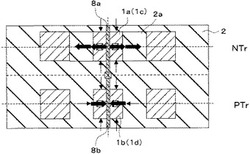

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板1aの活性領域1cが素子分離絶縁膜2で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極8a、ソース・ドレイン領域及び被覆応力膜を有するNTrを有し、ソース・ドレイン領域の両側部に位置する素子分離絶縁膜2aの表面は、ソース・ドレイン領域の表面より低い位置に形成されており、ゲート電極8a、活性領域1c、及び表面がソース・ドレイン領域の表面より低い位置に形成された素子分離絶縁膜2aを被覆して、チャネル形成領域に対し引張応力を印加する被覆応力膜が形成されている構成とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】nチャネル型MISFETQn1,Qn2を覆うように半導体基板1上に引張応力膜としての窒化シリコン膜5を形成する。窒化シリコン膜5は窒化シリコン膜5a,5b,5cの積層膜である。窒化シリコン膜5a,5bの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分よりも小さく、窒化シリコン膜5a,5bは、成膜後に紫外線照射処理を行って引張応力を増大させる。窒化シリコン膜5a,5b,5cの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分以上であり、窒化シリコン膜5cに対しては紫外線照射処理を行わない。

(もっと読む)

半導体装置及びその製造方法

【課題】保護膜としてSiN膜が使用されている場合であっても、素子動作特性の変動を軽減することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置2は、ドレインドリフト領域12を有する半導体基板11と、ドレインドリフト領域12上に形成されたフィールド酸化膜17と、ゲート電極18と、中間絶縁膜17と、メタル層21,22と、これらを覆うSiN膜23と、SiN膜23上にO3−TEOSを用いたCVD法により形成され、カーボンを含有するPSG膜24とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

半導体装置

【課題】温度が上昇するほどキャリアの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、素子形成面が(110)面方位の半導体基板上にチャネル長方向が<−110>方向に沿って配置される第1絶縁ゲート型電界効果トランジスタpMOS1と、前記半導体基板上にチャネル長方向が<−110>方向に沿って配置され、前記第1絶縁ゲート型電界効果トランジスタと前記チャネル長方向に隣接する第2絶縁ゲート型電界効果トランジスタnMOS1と、前記第1,第2絶縁ゲート型電界効果トランジスタ上を覆うように設けられ、正の膨張係数を有し、前記第1,第2絶縁ゲート型電界効果トランジスタに、動作熱によりチャネル長方向に沿って圧縮応力を加えピエゾ材料を含む第1ライナー絶縁膜11−1とを具備する。

(もっと読む)

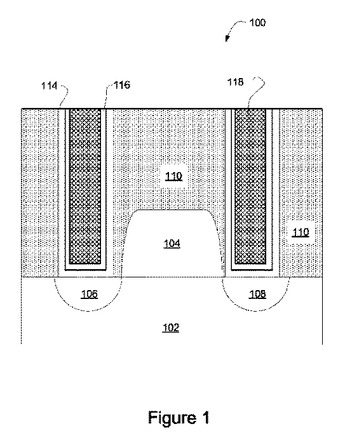

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作不良を防止し、半導体装置の製造工程を簡略化する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1と、半導体基板1内に設けられる一対の不純物拡散層2A,2Bと、不純物拡散層2A,2B間の半導体基板上に設けられるゲート絶縁膜3と、ゲート絶縁膜3上に設けられるゲート電極4と、一対の不純物拡散層2A,2B上にそれぞれ設けられる2つのコンタクト5A,5Bとを具備し、ゲート電極4とコンタクト5A,5Bは、同じ材料から構成され、ゲート電極4上端およびコンタクト5A,5B上端は、半導体基板1表面からの高さが一致する。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【課題】 サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【解決手段】 直線端部を有する突出構造体を基板(8)上に形成する。突出構造体は電界効果トランジスタのゲートラインとすることができる。応力誘起ライナを基板(8)上に堆積させる。少なくとも2つの不混和性のポリマブロック成分を含む非感光性自己組織化ブロックコポリマ層を応力誘起ライナ(50)の上に堆積させ、アニールして不混和性成分を相分離させる。ポリマレジストを現像して少なくとも2つのポリマブロック成分のうちの少なくとも1つを除去し、突出構造体の直線端部(41)により入れ子になったラインのパターンを形成する。直線型のナノスケール・ストライプが、自己配列及び自己組織化のポリマレジスト内に形成される。応力誘起層は、サブリソグラフィック幅を有する直線型応力誘起ストライプにパターン化される。直線型応力誘起ストライプ(50)は主にそれらの縦方向に沿った一軸性応力をもたらし、下層の半導体デバイスに異方性応力を加える。

(もっと読む)

半導体装置

【課題】ゲート−ドレイン間容量を小さくしてスイッチング特性を向上できる半導体装置を提供する。

【解決手段】トレンチ6、7側壁に形成したゲート電極10とトレンチ6、7内のドレインプラグ15間に、低誘電率層間絶縁膜であるLow−k膜12を形成することで、ゲート−ドレイン間容量を低減してスイッチング特性を向上させることができる。Low−k膜12はSiOC膜、又はNCS膜である。Si基板と直接接触する部分に酸化膜などの絶縁膜を被覆し、その上にLow−k膜を形成することで、信頼性とスイッチング特性の改善を両立させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とコンタクトの間の容量とフリンジ容量の両者を低減することが半導体装置及びその製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10上にゲート絶縁膜20とゲート電極21が形成され、ゲート電極の両側部における半導体基板にソース・ドレイン領域13が形成されて、電界効果トランジスタが構成されており、電界効果トランジスタを被覆して第1絶縁膜26が形成され、第1絶縁膜においてソース・ドレイン領域に達するようにコンタクトホールCHSDが開口され、コンタクトホール内にコンタクトプラグ(28,29,30)が埋め込まれ、第1絶縁膜の上層に第2絶縁膜(31,33)が形成されており、ゲート電極とコンタクトプラグの間の領域における第1絶縁膜が除去され、ゲート電極の側面とコンタクトプラグの側面を含む面から空隙Vが構成されている構成とする。

(もっと読む)

半導体装置

【課題】従来と異なる方法によりチャネル領域に歪みを発生させたMISFET構造を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成された第1のソース・ドレイン領域および第1のチャネル領域を有するn型MISFETと、前記半導体基板上に形成された第2のソース・ドレイン領域および第2のチャネル領域を有するp型MISFETと、前記第1のソース・ドレイン領域に接続され、前記第1のチャネル領域に伸張歪みを与える第1のコンタクトプラグと、前記第2のソース・ドレイン領域に接続され、前記第2のチャネル領域に圧縮歪みを与える第2のコンタクトプラグと、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】界面準位を低減し、特性変動及びリーク電流の少ない半導体製造装置及びその製造方法を提供する。

【解決手段】半導体基板1上に拡散層4を形成し、拡散層4内の上部にソース拡散領域10a及びドレイン拡散領域を形成し、拡散層4の上に、ゲート絶縁膜5を介してゲート電極8を形成し、ゲート電極8の上に保護膜13を形成し、保護膜13を覆うように絶縁層14を形成し、絶縁層14内に、保護膜13を介してゲート電極8の側面に多結晶シリコンプラグ15を形成し、その下方はゲート絶縁膜5及びゲート絶縁膜5と接している部分の保護膜13を貫通して、ソース拡散領域10aまたはドレイン拡散領域にそれぞれ連結させ、保護膜13中にフッ素を注入し、フッ素をゲート絶縁膜15と拡散層4との間のシリコン‐絶縁膜界面まで拡散させることを特徴とする。

(もっと読む)

珪化コバルトを含んだトランジスタゲート、そのトランジスタゲートを含んだ半導体装置構造、前駆構造、および製造方法

珪化コバルトを含んだ導電性要素を持つトランジスタゲートを製造するための方法であって、高温工程(迫り上げ式ソースドレイン領域の作成など)が完了する後までに、トランジスタゲートの側壁スペーサー同士のあいだにて、犠牲材料を仮置きとして用いることを含む。加えて、珪化コバルトをその導電性要素内に有するトランジスタゲートを具えた半導体装置(DRAM装置およびNANDフラッシュメモリ装置など)も開示しており、同様に、迫り上げ式ソースドレイン領域および珪化コバルトをそのトランジスタゲート内に持つトランジスタも開示する。側壁スペーサー同士の上部のあいだに犠牲材料もしくは空隙を持つトランジスタゲートを含んだ、中途半導体装置構造についても開示をしている。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜中に、内壁面で画成された開口部を形成する工程と、前記内壁面をCu−Mn合金層により、前記Cu−Mn合金層が、前記内壁面に直接に接するように覆う工程と、前記Cu−Mn合金層上に第1のCu層を堆積する工程と、前記第1のCu層上に第2のCu層を堆積し、前記第2のCu層により前記開口部を充填する工程と、前記内壁面上に、前記Cu−Mn合金層中のMn原子と前記絶縁膜との反応により、バリア層を形成する工程と、前記Cu−Mn層中の未反応Mn原子を前記第2のCu層の表面より、前記第1および第2のCu層を介して除去する工程と、含む半導体装置の製造方法において、形成されるCu配線層の抵抗を低減する。

【解決手段】前記Cu−Mn合金層の形成の後、大気に露出することなく、前記Cu−Mn合金層上に前記第1のCu層を堆積する工程を設ける。

(もっと読む)

半導体装置の製造方法

【課題】 浅い不純物拡散領域におけるドーパント不純物の拡散を抑制し得る半導体装置の製造方法を提供する。

【解決手段】 半導体基板10上にゲート絶縁膜18を介してゲート電極20を形成する工程と、ゲート電極をマスクとして半導体基板内にドーパント不純物を導入することにより、ゲート電極の両側の半導体基板内に不純物拡散領域28、36を形成する工程と、半導体基板上に、ゲート電極を覆うようにシリコン酸化膜38を形成する工程と、シリコン酸化膜を異方性エッチングすることにより、ゲート電極の側壁部分にシリコン酸化膜を有するサイドウォールスペーサ42を形成する工程とを有する半導体装置の製造方法であって、シリコン酸化膜を形成する工程では、ビスターシャルブチルアミノシランと酸素とを原料として用い、熱CVD法により、500〜580℃の成膜温度で、シリコン酸化膜を形成する。

(もっと読む)

半導体装置

【課題】埋め込み特性や膜特性に優れたシリコン酸化膜を高アスペクト比を有する凹部に形成することが可能な半導体装置を提供すること。

【解決手段】半導体装置は、半導体基板の主表面側に形成された凹部を有する下地領域と、前記下地領域の凹部内全体に埋め込まれた塩素を含有するシリコン酸化膜とを有することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】応力制御膜に生ずる複数の歪によって異なる複数種のトランジスタのチャネル移動度を向上させる。

【解決手段】シリコン基板21上にn型FET素子領域30aとp型FET素子領域30bとを形成し、ゲート電極25a,25bおよびソース・ドレイン領域28a,28bを内包すると共に、p型FET素子領域30bに対して最適化された真性応力を有する応力制御膜31を形成し、n型FET素子領域30a上の応力制御膜31に対して化学反応処理を施すことによって、n型FET素子領域30a上に他とは異なる真性応力を有する応力制御膜31aにす。こうして、互いに異なる応力を両FET素子領域30a,30bに作用させてチャネル領域の電子移動度を向上させ、ドレイン電流を向上させる。

(もっと読む)

1 - 20 / 33

[ Back to top ]