Fターム[5F140CC06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741) | SiO (1,517) | 不純物含有 (356) | BSG (34)

Fターム[5F140CC06]に分類される特許

1 - 20 / 34

半導体装置及び半導体装置の製造方法

【課題】新規な構造のコンタクトプラグを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、半導体基板に形成され、ソース/ドレイン領域及びゲート電極を有するトランジスタと、トランジスタのソース/ドレイン領域及びゲート電極を覆う絶縁膜と、絶縁膜中に形成され、トランジスタのソース/ドレイン領域またはゲート電極に接されるコンタクトプラグとを有し、コンタクトプラグは、絶縁膜の厚さ方向に延在しトランジスタのソース/ドレイン領域またはゲート電極に接触する柱部と、柱部の上部から絶縁膜の表面と平行な方向に張り出し上面が平坦化された鍔部とを有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電材料のゲートトレンチへの埋め込みが容易な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上の絶縁膜と、絶縁膜に設けられた凹部と、凹部の底部であって半導体基板上に設けられたゲート絶縁膜とを形成する工程と、凹部の内壁面上と絶縁膜の上面上に、第1金属を含む導電材料で第1ゲート電極膜を形成する工程と、第1ゲート電極膜上に、凹部の側面部分の一部は覆わないように、導電材料の融点よりも高い融点を持つ材料でカバー膜を形成する工程と、カバー膜が形成された状態で、熱処理を行って、第1ゲート電極膜をリフローさせる工程とを有する。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

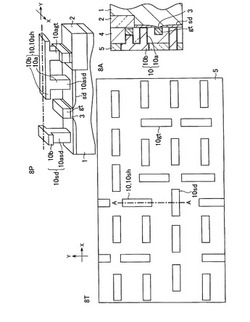

トレンチ型パワーMOSトランジスタおよびその製造方法

【課題】パワーMOSトランジスタにおいて、高い降伏電圧、高い出力電流および高速の動作速度を備えるのみならず、水平構造を備えるために、CMOSの製造工程で製作された一般的な集積回路と同一のチップ上に整合させる。

【解決手段】本発明のトレンチ型パワーMOSトランジスタはゲート導電体312と、絶縁層310とを備えたトレンチ型ゲート領域を具備する。絶縁層310は、ゲート導電体312と井戸領域308との間で薄い側壁領域を形成しており、ゲート導電体312と二重拡散のドーピング領域306との間で厚い側壁領域を形成するとともに、ゲート導電体312と深井戸領域304との間で厚い最下部領域を形成している。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

導電性コンタクトの組み込みのための構造体及びプロセス

【課題】 キーホール・シームの形成を排除した信頼性が高い高アスペクト比のコンタクト構造体を含む半導体構造を提供する。

【解決手段】 キーホール・シームの形成は、本発明においては、誘電体材料内部に存在する高アスペクト比のコンタクト開口部内に高密度化貴金属含有ライナを設けることによって排除される。高密度化貴金属含有ライナは拡散バリアの上に配置され、これら両方の要素は、本発明のコンタクト構造体の導電性材料を、下層の半導体構造体の導電性材料から分離する。本発明の高密度化貴金属含有ライナは、第1の抵抗率を有する貴金属含有材料の堆積、及び、堆積した貴金属含有材料の抵抗率をより低い抵抗率に減少させる高密度化処理プロセス(熱又はプラズマ)を、堆積した貴金属含有材料に施すことによって形成される。

(もっと読む)

コンタクト構造物の形成方法、及びこれを利用した半導体装置の製造方法

【課題】コンタクト構造物の形成方法及びこれを利用した半導体装置の製造方法を提供する。

【解決手段】コンタクト領域103を有する対象体100上に絶縁層106を形成した後、絶縁層106をエッチングしてコンタクト領域103を露出させる開口を形成する。露出されたコンタクト領域103上にシリコン及び酸素を含む物質膜を形成した後、シリコン及び酸素を含む物質膜上に金属膜を形成する。シリコン及び酸素を含有する物質膜と金属膜を反応させて、少なくともコンタクト領域103上に金属酸化物シリサイド膜121を形成した後、金属酸化物シリサイド膜121上の開口を埋める導電膜を形成する。コンタクト領域とコンタクトとの間に金属、シリコン、及び酸素が三成分系を成す金属酸化物シリサイド膜を均一に形成することができるため、改善された熱安定性及び電気的特性を有する。

(もっと読む)

サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【課題】 サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【解決手段】 直線端部を有する突出構造体を基板(8)上に形成する。突出構造体は電界効果トランジスタのゲートラインとすることができる。応力誘起ライナを基板(8)上に堆積させる。少なくとも2つの不混和性のポリマブロック成分を含む非感光性自己組織化ブロックコポリマ層を応力誘起ライナ(50)の上に堆積させ、アニールして不混和性成分を相分離させる。ポリマレジストを現像して少なくとも2つのポリマブロック成分のうちの少なくとも1つを除去し、突出構造体の直線端部(41)により入れ子になったラインのパターンを形成する。直線型のナノスケール・ストライプが、自己配列及び自己組織化のポリマレジスト内に形成される。応力誘起層は、サブリソグラフィック幅を有する直線型応力誘起ストライプにパターン化される。直線型応力誘起ストライプ(50)は主にそれらの縦方向に沿った一軸性応力をもたらし、下層の半導体デバイスに異方性応力を加える。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極の側壁絶縁膜のエッチングを効果的に防止することが可能な半導体装置を提供する。

【解決手段】 半導体基板11と、半導体基板上に形成されたゲート絶縁膜13と、ゲート絶縁膜上に形成されたゲート電極22と、ゲート電極の側面に形成された第1の絶縁膜17と、第1の絶縁膜の表面を覆い、第1の絶縁膜とは異なった材料で形成された第2の絶縁膜28と、半導体基板、ゲート電極及び第2の絶縁膜を覆い、第2の絶縁膜とは異なった材料で形成された第3の絶縁膜23とを備える。

(もっと読む)

珪化コバルトを含んだトランジスタゲート、そのトランジスタゲートを含んだ半導体装置構造、前駆構造、および製造方法

珪化コバルトを含んだ導電性要素を持つトランジスタゲートを製造するための方法であって、高温工程(迫り上げ式ソースドレイン領域の作成など)が完了する後までに、トランジスタゲートの側壁スペーサー同士のあいだにて、犠牲材料を仮置きとして用いることを含む。加えて、珪化コバルトをその導電性要素内に有するトランジスタゲートを具えた半導体装置(DRAM装置およびNANDフラッシュメモリ装置など)も開示しており、同様に、迫り上げ式ソースドレイン領域および珪化コバルトをそのトランジスタゲート内に持つトランジスタも開示する。側壁スペーサー同士の上部のあいだに犠牲材料もしくは空隙を持つトランジスタゲートを含んだ、中途半導体装置構造についても開示をしている。  (もっと読む)

(もっと読む)

抵抗が低減されたfinFET及びその製造方法

【課題】 抵抗が低減されたfinFET及びその製造方法を提供する

【解決手段】 (1)基板を準備するステップと、(2)基板上にfinFETの少なくとも1つのソース/ドレイン拡散領域を形成するステップとを含む、finFETの製造方法を提供する。各々のソース/ドレイン拡散領域は、(a)非シリサイド化シリコンの内部領域と、(b)非シリサイド化シリコン領域の上面及び側壁の上に形成されたシリサイドとを含む。

(もっと読む)

半導体装置

【課題】プラズマチャージによる影響を抑制することによる信頼性の向上、かつ、微細化が図られた半導体装置を提供する。

【解決手段】本発明にかかる半導体装置は、第1導電型の半導体層10と、半導体層10に設けられた分離絶縁層20により特定された第1領域10Aおよび第2領域10Bと、第2領域10Bに設けられたゲート絶縁層32と、第1領域10Aおよび第2領域10Bの上方に設けられた連続したゲート電極34と、第2領域10Bに設けられたゲート電極34を挟む不純物領域36と、を含み、少なくとも第1領域10Aの上方に位置するゲート電極34は、第2導電型の半導体部である。

(もっと読む)

レーザ照射装置及び半導体装置の製造方法

【課題】シリンドリカルレンズアレイを用いて線状ビームを形成する際に、原ビームの光軸ずれを防止することでシリンドリカルレンズアレイにおける原ビームの入射位置のずれを防止し、安定的に均一強度分布の線状ビームを形成すること。

【解決手段】レーザ発振器から射出されるレーザビームを偏向する偏向ミラーと、転送レンズと、転送レンズを通過したレーザビームを複数に分割するシリンドリカルレンズアレイと、シリンドリカルレンズアレイで形成されたレーザビームを重ね合わせる集光レンズとを備え、レーザ発振器の射出口から偏向ミラーまでの距離をa、偏向ミラーから前記転送レンズまでの距離をb、転送レンズからシリンドリカルレンズアレイの入射面までの距離をc、転送レンズの焦点距離をfとした場合、これらが次式、

1/f=1/(a+b)+1/c

を満たすように配置する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極にドライエッチングが困難な低抵抗材料を用いて、自己整合コンタクト構造を有する半導体装置を製造する。

【解決手段】シリコン基板上に、ゲート絶縁膜、ポリシリコン膜および第1絶縁膜を形成する工程と、第1絶縁膜をパターニングする工程と、金属膜を形成する工程と、ポリシリコン膜と金属膜と反応させてシリサイド層を形成する工程と、未反応の金属膜の除去後に、第2絶縁膜を形成する工程と、第1絶縁膜が露出し且つ第1絶縁膜で覆われていない領域に第2絶縁膜が残るように第2絶縁膜を除去する工程と、第1絶縁膜の除去後に、第2絶縁膜をマスクに用いてエッチングを行い、上層側にシリサイド層および下層側にポリシリコン層を有するゲート電極を形成する工程と、ゲート電極の側面に第3絶縁膜を形成する工程と、層間絶縁膜を形成し、コンタクトホールを形成する工程とを有する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】動作特性が向上した半導体装置の製造方法及びそれによって製造された半導体装置を提供する。

【解決手段】基板上にNMOSトランジスタを形成し、NMOSトランジスタ上に第1層間絶縁膜を形成し、第1層間絶縁膜を脱水素化することを含む半導体装置の製造方法。脱水素化することは、第1層間絶縁膜のストレスを変化させうる。特に、第1層間絶縁膜は脱水素化の後、200MPa以上の引張ストレスを有しうる。脱水素化された層間絶縁膜を含む半導体装置も提供される。

(もっと読む)

1 - 20 / 34

[ Back to top ]