Fターム[5F140CC13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 製法 (1,285) | CVD (1,073) | プラズマCVD (324)

Fターム[5F140CC13]に分類される特許

141 - 160 / 324

半導体装置及びその製造方法

【課題】ゲート電極をフルシリサイド化したMISFETを有する半導体装置及びその製造方法に関し、MISFETの特性劣化を引き起こすことなくゲート電極をフルシリサイド化しうる半導体装置の製造方法、並びに、そのような製造方法を用いて形成された優れた特性のMISFETを有する半導体装置を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜18と、ゲート絶縁膜18上に形成された金属シリサイド膜56bと、金属シリサイド膜56b上に形成された金属シリサイド膜56aとを有し、金属シリサイド膜56bにおける金属元素に対するシリコンの組成が、金属シリサイド膜56aにおける金属元素に対するシリコンの組成よりも大きいゲート電極26nと、ゲート電極26nの両側の半導体基板10内に形成された不純物拡散領域対54とを含むトランジスタを有する。

(もっと読む)

半導体装置の製造方法

【課題】 自然酸化膜を還元除去できる低温化可能な工程を有する半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、(a)少なくともシリコン表面層を有する基板を準備する工程と、(b)前記シリコン層の表面に厚さ0.1nm〜0.5nmの自然酸化膜を形成する工程と、(c)前記厚さ0.1nm〜0.5nmの自然酸化膜を水素アニール処理により、還元除去する工程と、(d)前記工程(c)に続いて、前記シリコン表面層の表面にゲート絶縁膜を形成する工程と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数の増加や前後のプロセスへの影響を抑えて、n型MOS−FET、p型MOS−FETのそれぞれに適する応力を付与することが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体基板wと、半導体基板wに形成されたソース領域12aおよびドレイン領域13aと、半導体基板w上のソース領域12a、ドレイン領域13a間に形成されたゲート電極16と、半導体基板wおよびゲート電極16上に形成された層間膜18と、層間膜18に埋め込み形成され、引張または圧縮応力を有する金属または金属化合物を含む膜22a、22bを有し、半導体基板wおよびゲート電極16と離間するように形成されたダミーフローティングパターン22を備える。

(もっと読む)

少なくとも1つの誘電体層を形成するための方法およびシステム

【課題】エッチングされた所望のアスペクト比の提供。

【解決手段】構造を形成するための方法が、基板の表面にわたって少なくとも1つの特徴部を形成するステップを含む。少なくとも1つの特徴部の上には窒素含有誘電体層を形成する。少なくとも1つの特徴部の少なくとも1つの側壁上の窒素含有層の第1の部分を、第1の速度で取り除き、少なくとも1つの特徴部の底部領域に隣接する基板の上の窒素含有層の第2の部分を、第2の速度で取り除く。第1の速度は第2の速度よりも大きい。窒素含有誘電体層の上に誘電体層を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】異なるチャネル長のトランジスタを有し、設計の自由度が向上され、かつ、ゲート容量の増加を防止できる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】半導体基板1に、第一の導電型の活性領域41、42を形成し、チャネル用シリコン柱4b、4cを含む複数のシリコン柱4a〜4dを形成した後、第二の導電型の第一半導体領域7aを形成する工程と、容量増加防止用絶縁膜10を設けてゲート電位供給用シリコン柱4a、4dを形成する工程と、前記チャネル用シリコン柱4b、4cの周囲にゲート絶縁膜11を設ける工程と、ゲート電位供給用電極12bとゲート電極12aを形成し、接続する工程と、第一層間絶縁膜13を形成する工程と、前記チャネル用シリコン柱4bの高さを低くする工程と、第二の導電型の第二半導体領域7bを形成する工程と、を有する半導体装置100の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法

【課題】MOSFETにおいて、ショートチャネル効果の抑制と移動度向上を両立させることを可能とする。

【解決手段】半導体基板13上にダミーゲート絶縁膜31を介してダミーゲート34を形成する工程と、ダミーゲート34の両側の半導体基板13にソース・ドレイン不純物領域23,24を形成する工程と、ダミーゲート34の両側の半導体基板13上にエクステンション領域25,26を形成する工程と、ダミーゲート34直下のソース側にソース不純物領域23のオーバーラップ領域27を形成する工程と、ダミーゲート34を除去し、該除去領域に露出したダミーゲート絶縁膜31を除去する工程と、除去領域に露出した半導体基板13にリセス形状15を形成する工程と、リセス形状15を形成した半導体基板13上にゲート絶縁膜21とゲート電極22とを順次形成する工程とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】高い平坦性の素子分離領域を得ることを課題とする。

【解決手段】トレンチ領域形成用のマスクとしての第1絶縁膜を半導体基板の直上に形成する工程と、マスクを用いて半導体基板にトレンチ領域を形成する工程と、トレンチ領域を含む半導体基板及び第1絶縁膜の直上に第2絶縁膜を形成することで、トレンチ領域上の第2絶縁膜からなる凹部と、第1絶縁膜上の第2絶縁膜からなる凸部と得る工程と、凹部の底面まで凸部を構成する第2絶縁膜を除去する第1除去工程と、第1絶縁膜及び第2絶縁膜を所定の膜厚まで化学的機械研磨法により除去することで、凹部及び凸部より形成された段差を20nm以下に低減する第2除去工程とを含み、第1絶縁膜及び第2絶縁膜が、同一の化学的機械研磨条件で研磨レートに差がない絶縁膜からなり、第2除去工程が、0.2〜0.6重量%の研磨粒子を含むスラリーを用いて行なわれることを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

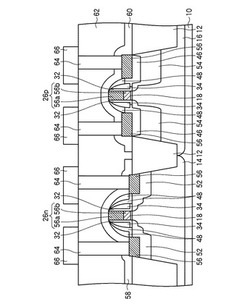

【課題】n型MISトランジスタのゲート電極、及びp型MISトランジスタのゲート電極の双方を精度良く実現する。

【解決手段】第1のMISトランジスタと第2のMISトランジスタとを備えた半導体装置において、第1のMISトランジスタは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され、シリコン膜14aとシリコン膜14a上に形成された第1の金属シリサイド膜20aとからなる第1のゲート電極26aとを備え、第2のMISトランジスタは、半導体基板10における第2の活性領域10b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜13b上に形成され、フルシリサイド化された第2の金属シリサイド膜20Bからなる第2のゲート電極26bとを備え、第1の金属シリサイド膜20aは、第2の金属シリサイド膜20Bに比べて膜厚が薄い。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性に優れた微細な半導体装置を提供する。

【解決手段】半導体基板と、半導体基板に形成されたトレンチ内の絶縁体からなる素子分離領域と、このトレンチ内の絶縁体に囲まれた半導体領域およびその上に形成された単結晶シリコン層を含む活性領域と、この単結晶シリコン層上に形成されたゲート絶縁膜と、前記活性領域を跨ぐようにゲート絶縁膜上に設けられたゲート電極と、このゲート電極の両側の、前記活性領域に設けられた拡散層と、を有する半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】小型で駆動力が高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1において、シリコン基板2のpMOS領域RpにpMOS8を形成し、nMOS領域RnにnMOS9を形成する。次に、pMOS領域Rpを覆うように、内部に圧縮応力が生じている圧縮応力膜11を形成し、圧縮応力膜11におけるnMOS領域Rn側の端側面上に緩衝膜13を形成し、nMOS領域Rn、圧縮応力膜11の端部、及び緩衝膜13を覆うように、内部に引張応力が生じている引張応力膜12を形成する。緩衝膜13は、その内部応力の大きさが圧縮応力膜11の圧縮応力の大きさ及び引張応力膜12の引張応力の大きさよりも小さい膜とする。

(もっと読む)

半導体装置、およびその製造方法

【課題】応力膜によるチャネル領域への歪み効果を向上させる形状の半導体基板を有し、かつ十分な深さのソース・ドレイン領域を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板と、半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、前記半導体基板の前記ゲート電極の両側の前記ゲート電極から離間した領域に凹部を形成する工程と、前記凹部の底面および側面からほぼ同じ深さまで前記半導体基板に導電型不純物を注入する工程と、前記凹部の底面および側面上に、前記半導体基板内の前記ゲート電極下のチャネル領域に歪みを与えて前記チャネル領域における電荷移動度を向上させる応力膜を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】電流駆動能力が高いMOSFETを備えた半導体装置を提供する。

【解決手段】半導体装置1において、シリコン基板2の表面にNMOS3を形成し、NMOS3のチャネル領域7の直上域に、内部に圧縮応力を有する圧縮応力膜8を設け、シリコン基板2上における少なくともチャネル領域7の直上域の周囲に、内部に引張応力を有する引張応力膜9を設ける。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲートオーバーラップ容量を少なくすることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】半導体基板1上に形成された柱状体3と、前記柱状体3の先端側3bに形成された先端側不純物拡散領域5と、前記柱状体3の基端側3aに形成された基端側不純物拡散領域4と、前記柱状体3の外周面3cに形成されたゲート絶縁膜7と、前記先端側不純物拡散領域5を覆うように外周面3cに形成された先端側絶縁層10と、前記基端側不純物拡散領域4を覆うように外周面3cに形成された基端側絶縁層9と、前記先端側絶縁層10および前記基端側絶縁層9の間に配置されたゲート電極8と、を具備することを特徴とする半導体装置21を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、各ゲートについて均一で十分なフル・シリサイド化を実現する、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極の表層部分及びソース/ドレイン領域16a,16bの表層部分がシリサイド化されている状態において、半導体基板1にフラッシュランプアニールを施す。この処理により、ソース/ドレイン領域16a,16bには(NiPt)2Si層19bが形成された状態が保持されて、ゲート電極のみが選択的にフル・シリサイド化され、フル・シリサイドゲート電極21が形成される。

(もっと読む)

半導体装置の製造方法

【課題】製造時における半導体素子へのプラズマダメージの影響を小さくすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に半導体素子を形成する工程と、マイクロ波をプラズマ源とし、半導体基板の表面近傍において、プラズマの電子温度が1.5eVよりも低く、かつプラズマの電子密度が1×1011cm−3よりも高いマイクロ波プラズマを用いたCVD処理によって半導体素子上に膜を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド膜上に形成されるシリコン窒化膜の膨れや剥離を抑えることができる半導体装置の製造方法を提供する。

【解決手段】表面にシリサイド膜が形成された領域を有する半導体基板を、酸素元素を含むガス雰囲気中でプラズマ処理してシリサイド膜の上に酸化膜を形成する工程と、その酸化膜を形成した後、半導体基板の表面を覆うシリコン窒化膜を形成する工程と、を備えた。

(もっと読む)

種類および膜厚の異なるゲート絶縁層を有するCMOSデバイス、ならびにその形成方法

high−k金属ゲート構造(310N,310B,310P)によって従来のゲート電極構造(310)を置換するためのプロセスシーケンスにおいて、例えば、選択性の高いエッチングステップ(322,325,327,331)を使用することによって、追加のマスク形成ステップの数を少なく保つことができ、これにより、従来のCMOS技術との高い互換性を保つことができる。更に、ここに開示の技術は、前工程(front-end)のプロセス技術および後工程(back-end)のプロセス技術との互換性を実現し、これにより、トランジスタレベルのほか、コンタクトレベルでも実績のある歪み発生機構を組み込むことが可能となる。  (もっと読む)

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】

CMOS装置の製造工程におけるコンタクト不良発生を抑制する。

【解決手段】

半導体装置の製造方法は、(a)Si基板に、n型の第1の活性領域、p型の第2の活性領域を形成する工程と、(b)活性領域に、第1、第2のゲート電極構造、第1、第2のソース・ドレイン領域をそれぞれ形成する工程と、(c)第1のソース/ドレイン領域に、凹部を形成する工程と、(d)凹部にSi−Geを含むp型の圧縮応力を有する半導体エピタキシャル層を形成する工程と、(e)半導体基板上に引張応力を有する窒化シリコンのエッチストッパ膜、層間絶縁膜を形成する工程と、(f)層間絶縁膜、エッチストッパ膜を貫通して、コンタクト孔をエッチングする工程と、(g)半導体基板上方に酸素を含むプラズマを発生する工程と、(h)コンタクト孔に導電性プラグを埋め込む工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細ショットキーMISFETのソース電極がチャネル端の表面ポテンシャルをピニングすることで発生するトランジスタ性能の劣化を防止する。

【解決手段】ショットキーMISFETを構成する、半導体基板上に形成したソース金属電極8と半導体基板中のチャネル領域11との接触で形成されるショットキー障壁高さとφB0、半導体基板のバンドギャップEGと、半導体基板の真性キャリア濃度niと、デバイスの動作温度Tと、ボルツマン係数kに対して、少なくともソース電極と接するチャネル端近傍の不純物濃度NCHを、NCH≦ni・exp((qφB0−0.5EG)/kT)の条件を満たすようにする。

(もっと読む)

141 - 160 / 324

[ Back to top ]