Fターム[5F140CC13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 製法 (1,285) | CVD (1,073) | プラズマCVD (324)

Fターム[5F140CC13]に分類される特許

161 - 180 / 324

半導体素子およびその製造方法

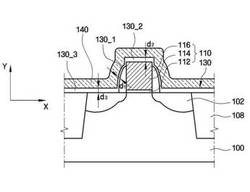

【課題】MOSトランジスタに十分な応力(ストレス)が加える半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、半導体基板100と、半導体基板100上に備えられたゲート電極114およびゲート電極114の側壁面に備えられたスペーサ116を含むゲート構造物110と、ゲート構造物110の両側の半導体基板100内に形成されたソース/ドレーン領域102と、ゲート構造物110上エッチング停止膜130と、を含み、エッチング停止膜130は、スペーサ116上の第1領域130_1およびゲート電極の上面上の第2領域130_2を含み、第1領域130_1の厚さは、第2領域130_2の厚さの85%以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】圧縮応力を有する絶縁膜と引っ張り応力を有する絶縁膜とが互いに応力を相殺することがない半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタと、第1の応力絶縁膜20Aと、第1の絶縁膜21Aと、第2の絶縁膜21Bとを備えている。第1のトランジスタは、半導体基板10の第1の活性領域11Aに形成され、第1のゲート電極14Aを有する。第1の応力絶縁膜20Aは、第1のゲート電極14Aを覆うように形成され、第1のトランジスタのチャネル領域に応力を加える。第1の絶縁膜21Aは、第1の応力絶縁膜20Aの上に接して形成され、上面が平坦化されている。第2の絶縁膜21Bは、第1の絶縁膜21Aの上に接して形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート酸化膜へのプラズマダメージを抑制することができ、ゲート酸化膜の劣化が抑制されるとともにスループットが向上した半導体装置の製造方法を提供する。

【解決手段】本発明にかかる半導体装置の製造方法において、プラズマ絶縁膜を形成する工程は、成膜装置内において、成膜ガスを供給しながら、高周波電界および低周波電界を印加してFET形成領域を覆う前記プラズマ絶縁膜を成膜する工程と、前記プラズマ絶縁膜を成膜した後、前記高周波電界の印加を継続しながら、前記低周波電界の印加を停止した後または同時に前記成膜ガスの流量を経時的に漸次減少させる工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】ダマシンゲートプロセスにおいて、ゲート電極用溝形成時に層間絶縁膜が後退せず、短絡の原因となる導電層の残渣が発生しない半導体装置の製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10にダミーゲート絶縁膜12とダミーゲート電極13を形成し、ダミーゲート電極をマスクとして基板にソース・ドレイン領域19を形成し、酸化シリコンよりフッ酸耐性を有する絶縁性材料によりダミーゲート電極より厚い膜厚でダミーゲート電極を被覆して第1絶縁膜21を形成し、その上に第1絶縁膜と異なる絶縁性材料で第2絶縁膜22を形成し、第2絶縁膜の上面から第1絶縁膜の頂部、さらにダミーゲート電極が露出するまで第1絶縁膜と第2絶縁膜とを平坦化除去し、ダミーゲート電極及びダミーゲート絶縁膜を除去し、得られるゲート電極用溝の底部にゲート絶縁膜を形成し、その上にゲート電極を形成し、電界効果トランジスタとする。

(もっと読む)

半導体装置およびその製造方法

【課題】LCDドライバなどで小型化によるプラグの高抵抗化を抑制し、かつ、高耐圧MISFETのゲート電極と配線間の耐圧不良を改善できる技術を提供する。

【解決手段】LCDドライバにおいて、高耐圧MISFETでは、電界緩和用絶縁領域3上にゲート電極10bの端部が乗り上げている。そして、高耐圧MISFET上の1層目の層間絶縁膜上にソース配線あるいはドレイン配線となる配線HL1が形成されている。このとき、半導体基板1Sとゲート絶縁膜8の界面からゲート電極10bの上部までの距離をa、ゲート電極10bの上部から配線HL1が形成されている層間絶縁膜の上部までの距離をbとすると、a>bとなっている。このように構成されている高耐圧MISFETにおいて、配線HL1は、高耐圧MISFETのゲート電極10bと平面的な重なりを有しないように配置されている。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

半導体装置の製造方法

【課題】水素原子の拡散による特性変動が少ない半導体装置を提供することを課題とする。

【解決手段】半導体基板上に、ゲート絶縁膜を介してゲート電極を形成する工程と、前記半導体基板及び前記ゲート電極上に第一のシリコン窒化膜を形成する工程と、前記ゲート電極をマスクとして前記第一のシリコン窒化膜を介して不純物注入することにより前記半導体基板の表面層に拡散領域を形成する工程と、前記第一のシリコン窒化膜上に第二のシリコン窒化膜を形成する工程とを含み、前記第一のシリコン窒化膜が、前記第二のシリコン窒化膜より水素含有量が小さいことを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタ及びp型MISトランジスタの双方において、所望のシリサイド組成比を有する金属シリサイド膜からなるフルシリサイド化ゲート電極を精度良く実現する。

【解決手段】半導体装置は、第1の活性領域10a上に形成された第1のゲート絶縁膜13a、第1のゲート絶縁膜13a上に形成された第1のフルシリサイド化ゲート電極24a、及び第1のサイドウォール17aとを有するn型MISトランジスタと、第2の活性領域10b上に形成された第2のゲート絶縁膜13b、第2のゲート絶縁膜13b上に形成された第2のフルシリサイド化ゲート電極24b、及び第2のサイドウォール17bとを有するp型MISトランジスタとを備える。第1のフルシリサイド化ゲート電極24aの上面高さは、第2のフルシリサイド化ゲート電極24bの上面高さよりも低い。

(もっと読む)

トランジスタのゲート電極のプレアモルファス化のブロッキング

トランジスタのソース/ドレイン領域を選択的にプレアモルファス化する一方で、トランジスタのゲート電極はプレアモルファス化しない技術が提供される。例示的実施形態においては、ゲート電極にわたってプレアモルファス化注入ブロッキング材料が形成される。更に例示的実施形態においては、各種ストレッサを用いてチャネル領域に歪みが誘発される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ニッケル膜又はニッケル合金膜を用いてシリサイド化を行う場合において、シリサイド化されたソース/ドレイン拡散層のシート抵抗及びそのばらつきを低減するとともに、接合リーク電流を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上10に、ゲート電極16とソース/ドレイン拡散層24とを有するトランジスタ26を形成する第1の工程と、半導体基板上に、ゲート電極及びソース/ドレイン拡散層を覆うように、ニッケル又はニッケル合金より成る金属膜28を、基板温度を220℃〜300℃とした状態で形成する第2の工程と、金属膜とソース/ドレイン拡散層の上部とを反応させ、ソース/ドレイン拡散層上に、ニッケルシリサイド又はニッケル合金シリサイドより成るシリサイド膜34bを形成する第3の工程とを有している。

(もっと読む)

半導体装置の製造方法

【課題】NMOSトランジスタなどのnチャネル領域を有する電界効果トランジスタの電流駆動能力をより向上させることができる半導体装置の製造方法を提供する。

【解決手段】半導体装置のNMOSトランジスタ3は、nチャネル領域を有する半導体基板1と、n型ソース/ドレイン領域4と、ゲート絶縁膜7と、ゲート電極8とを含んでいる。n型ソース/ドレイン領域4は、半導体基板1上にnチャネル領域を挟むように形成されている。ゲート絶縁膜7はnチャネル領域上に形成されている。半導体装置の製造方法は、半導体基板1上にゲート絶縁膜7およびゲート電極8が形成される工程と、半導体基板1上にゲート電極8を覆うように窒化シリコンを含む薄膜20が形成される工程と、この薄膜20に紫外線が照射される工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 n型FET及びp型FETのドレイン電流の増加(電流駆動能力の向上)を図る。

【解決手段】 半導体基板に形成されたn型及びp型FETを有する半導体装置の製造であって、前記p型FETのゲート電極と前記半導体基板の素子分離領域との間の半導体領域を絶縁膜で覆った状態で、前記n型及びp型FET上にこれらのゲート電極を覆うようにして、前記n型FETのチャネル形成領域に引っ張り応力を発生させる第1の絶縁膜を形成する(a)工程と、エッチング処理を施して、前記p型FET上の前記第1の絶縁膜を選択的に除去する(b)工程と、前記n型及びp型FET上にこれらのゲート電極を覆うようにして、前記p型FETのチャネル形成領域に圧縮応力を発生させる第2の絶縁膜を形成する(c)工程と、前記n型FET上の前記第2の絶縁膜を選択的に除去する(d)工程とを有する。

(もっと読む)

電界効果型トランジスタの修復方法、半導体装置の修復方法、半導体装置の作製方法、及び半導体装置

【課題】電界効果型トランジスタのリーク電流を低減し、寿命の向上を図るための簡便な修復方法を提供することを課題とする。また、作製コストの増加を抑え、消費電力が小さく、且つ信頼性の高い半導体装置を提供することを課題とする。

【解決手段】ソース電極又はドレイン電極の一方と、ゲート電極との間に、電気的な衝撃を加える。または、ソース電極又はドレイン電極の一方と、ソース電極又はドレイン電極の他方との間に、電気的な衝撃を加える。これにより、リークパスを絶縁化し、リーク電流を低減することができる。なお、上記の電気的な衝撃は、静電気等の電気パルスであっても良いし、直流電圧、交流電圧、直流電流、交流電流等であっても良い。

(もっと読む)

半導体装置及びその製造方法

【課題】 nチャネル導電型電界効果トランジスタ及びpチャネル導電型電界効果トランジスタの電流駆動能力の向上を図る。

【解決手段】 半導体基板の一主面の第1の領域にチャネル形成領域が構成されたnチャネル導電型電界効果トランジスタと、前記半導体基板の一主面の第1の領域と異なる第2の領域にチャネル形成領域が構成されたpチャネル導電型電界効果トランジスタとを有する半導体装置であって、前記nチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力と、前記pチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力とが、各々で異なっている。前記nチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力は引っ張り応力であり、前記pチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力は圧縮応力である。

(もっと読む)

半導体装置の製造方法

【課題】拡散層領域を細く形成する場合でも、拡散層領域の縮みによるコンタクト抵抗の増大を抑えることを可能とした半導体装置の製造方法を提供する。

【解決手段】素子分離領域によって分離された拡散層領域5を形成する際に、2重露光技術を用いて拡散層領域5を2段階に分けて形成する。これにより、拡散層領域5を細く形成する場合でも、拡散層領域5の長手方向の両端における縮みを抑制することができ、拡散層領域5の長手方向における両端と、コンタクトホール12に埋め込まれたコンタクトプラグ13との接続面積を確保しながら、コンタクト抵抗の上昇を抑えることが可能である。

(もっと読む)

半導体装置及びその製造方法

【課題】 nチャネル導電型電界効果トランジスタ及びpチャネル導電型電界効果トランジスタの電流駆動能力の向上を図る。

【解決手段】 半導体基板の一主面の第1の領域にチャネル形成領域が構成されたnチャネル導電型電界効果トランジスタと、前記半導体基板の一主面の第1の領域と異なる第2の領域にチャネル形成領域が構成されたpチャネル導電型電界効果トランジスタとを有する半導体装置であって、前記nチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力と、前記pチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力とが、各々で異なっている。前記nチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力は引っ張り応力であり、前記pチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力は圧縮応力である。

(もっと読む)

PMOSトランジスタ製造方法及びCMOSトランジスタ製造方法

【課題】簡単な工程を通じて優れた動作特性を有するPMOSトランジスタ及びCMOSトランジスタの製造方法を提供する。

【解決手段】 PMOSトランジスタの製造方法において、基板上にゲート酸化膜パターン及び該ゲート酸化膜パターン上に積層されるゲート電極を含むゲート構造物を形成する段階と、前記ゲート構造物に隣接する両側の基板表面下に周期表第3族からなる不純物を注入させて複数の不純物領域を形成する段階と、前記基板の表面及びゲート構造物表面上に不純物拡散防止膜を形成する段階と、前記不純物拡散防止膜上にシリコン窒化膜を形成する段階と、前記不純物領域に含まれる不純物を活性化させながら前記不純物領域間に歪みシリコン領域(strained silicon region)が形成されるように前記基板を熱処理する段階とを有することを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル領域のゲート幅方向に与える応力を移動度が向上する方向に働かすとともに、ソース・ドレイン領域表面にシリサイド層を形成した際のリークの発生を防止することを可能とする。

【解決手段】半導体基板11の素子形成領域12を挟むようにして該半導体基板11に埋め込んで形成された素子分離領域13と、ゲート絶縁膜21を介して素子形成領域12を横切るように形成されたゲート電極22と、ゲート電極22の両側の素子形成領域12に形成されたソース・ドレイン領域27、28とを備え、ゲート電極22下における素子形成領域12からなるチャネル領域14が素子分離領域13より突出するように形成されていて、ソース・ドレイン領域27、28は素子分離領域14の表面より深い位置まで形成されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】ダミーゲートを除去することで形成された溝39、59を有して半導体基板11上に形成された側壁絶縁膜33、53と、前記溝39、59内にゲート絶縁膜41を介して形成されたゲート電極43、63と、前記側壁絶縁膜33、53上から前記半導体基板11上にかけてそれぞれに形成された第1、第2応力印加膜21、22と、前記ゲート電極43、63の両側に前記半導体基板11に形成されたソース・ドレイン領域35、36、55、56とを有し、前記応力印加膜21、22は前記第1溝39、第2溝59が形成される前に成膜されていることを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】トランジスタ構造を非対称にすることなく、短チャネル効果が抑制された状態で、寄生抵抗を十分に低減することができ、チャネル領域の結晶欠陥が抑制された半導体装置の製造方法および半導体装置を提供する。

【解決手段】まず、Si層11a、SiO2層11bおよびSi層11cがこの順に積層されたSOI基板11上に、ゲート絶縁膜15を介してゲート電極16を形成する工程を行う。次に、ゲート電極16をマスクにしたエッチングにより、SOI基板11を最下層のSi層11aが露出するまで掘り下げる工程を行う。次いで、露出されたSi層11aの表面上に、Si層をエピタキシャル成長させてエピタキシャル成長層22を形成するとともに、エピタキシャル成長層22にソース・ドレイン領域23を形成する工程を行うことを特徴とする半導体装置の製造方法および半導体装置である。

(もっと読む)

161 - 180 / 324

[ Back to top ]