Fターム[5F140CC13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 製法 (1,285) | CVD (1,073) | プラズマCVD (324)

Fターム[5F140CC13]に分類される特許

61 - 80 / 324

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の上にゲート絶縁膜を形成する工程と、ゲート絶縁膜の上にゲート電極14cを形成する工程と、ゲート電極14cの側面にサイドウォール15a、15bを形成する工程と、サイドウォール15a、15bを形成した後に、有機アルカリ溶液又はTMAHをエッチング液として用いて、ゲート電極14cの横の半導体基板10に穴10a、10bを形成する工程と、穴10a、10bにソース/ドレイン材料層18a、18bを形成する工程とを有する。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

保護トランジスタおよび半導体集積回路

【課題】占有面積が小さく、所望の耐圧と熱破壊の防止を両立した保護トランジスタを提供する。

【解決手段】ゲート長方向の一方の側でゲート直下の領域に隣接しているゲート・ドレイン間領域REgdが、ゲート幅方向に互いに隣接する領域として、第1領域REgd1と第2領域REgd2とを有する。第1領域は、ドレイン耐圧が相対的に大きく、第2領域は、ドレイン電極(ドレインコンタクト部に設けられているシリサイド層10D)からの距離が平面視で第1領域より遠く、ドレイン耐圧が相対的に小さい。このため、耐圧が低いゲート・ドレイン間領域REgd2の加熱部分Aからドレインコンタクト部が遠いが、面積は小さく(または拡大しない)構造となっている。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置の製造方法

【課題】 置換ゲート工程で発生する不良を防止できる半導体装置の製造方法を提供する。

【解決手段】本発明による半導体装置の製造方法は、半導体基板上にゲート絶縁膜および犠牲ゲート電極を含むゲートパターンを形成する段階、前記半導体基板および前記ゲートパターン上にエッチング停止層および絶縁層を形成する段階、前記エッチング停止層が露出するまで前記絶縁層を除去する段階、前記犠牲ゲート電極が露出するまで前記エッチング停止層をエッチバックする段階、前記犠牲ゲート電極を除去し、結果物の全体構造の上面に金属層を形成する段階、前記絶縁層が露出するまで前記金属層を除去する段階、および前記金属層を所定の深さでエッチバックする段階を含む。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

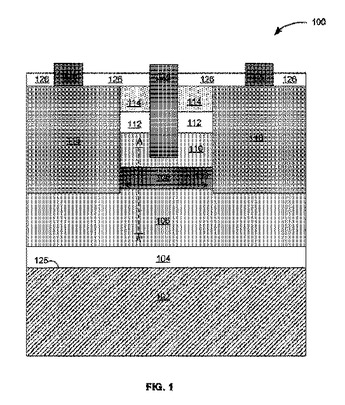

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

液晶パネル用基板、液晶パネル、電子機器及び投射型表示装置

【課題】半導体を基板とする液晶パネルは、ウェル領域があるため、漏れ光がトランジスタ部分のみでなくそこから離れた半導体基板を通過しただけで光リーク電流が流れることがある。この光リーク電流が、ガラス基板上にスイッチング素子としてのTFTを配置した液晶パネルに比べて多くなるという欠点がある。

【解決手段】反射電極となる画素電極(14)と、画素電極への電圧印加を制御するスイッチング素子とを有する画素単位が基板上にマトリックス状に配置されてなる液晶パネル用基板において、両素電極とスイッチング素子の端子電極を構成する導電層(6a)との間に、両者を接続するためのコンタクトホールを形成し、このコンタクトホールの形成箇所を囲む開口を有し、隣接する複数の画素電極の間の領域には開口を有さない遮光層を、画素電極と導電層との間に設けることにより、画素電極どうしの隙間から漏込む光による弊害を防ぐ。

(もっと読む)

集積回路デバイスに歪みを与える技術及び構成

本開示の実施形態により、例えば横型電界効果トランジスタなどの集積回路デバイスに歪みを与える技術及び構成が提供される。集積回路デバイスは、半導体基板と、該半導体基板と結合された第1のバリア層と、第1のバリア層に結合された、第1の格子定数を持つ第1の材料を有する量子井戸チャネルと、量子井戸チャネルに結合されたソース構造とを含む。ソース構造は、第1の格子定数とは異なる第2の格子定数を持つ第2の材料を有し、量子井戸チャネルに歪みを与える。その他の実施形態も開示される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

高耐圧半導体装置および駆動回路

【課題】スイッチング応答速度が速い高耐圧トランジスタ、および電力損失および誤動作を抑制した駆動回路を提供すること。

【解決手段】高耐圧半導体装置は、p-型シリコン基板100上に設けられ、かつp-ウエル領域102に囲まれたn-型領域101と、ドレイン電極120と接続されるドレインn+領域103と、ドレインn+領域103と離れて設けられ、かつドレインn+領域103を囲むpベース領域105と、pベース領域105内に形成されたソースn+領域114と、を備える。また、n-型領域101を貫通し、かつシリコン基板100に達するp-領域131が設けられている。n-型領域101は、p-領域131により、n-型領域101aとn-型領域101bに分離されている。n-型領域101aは、ドレインn+領域103を備えている。n-型領域101bは、フローティング電位を有する。

(もっと読む)

半導体装置

【課題】 半導体装置に関し、ソース・ドレイン領域を実効的に埋込Si混晶層で構成する際の電気的特性を向上する

【解決手段】 一導電型シリコン基体と、一導電型シリコン基体上に設けたゲート絶縁膜と、ゲート絶縁膜の上に設けたゲート電極とゲート電極の両側の一導電型シリコン基体に設けた逆導電型エクステンション領域と、逆導電型エクステンション領域に接するとともに、一導電型シリコン基体に形成された凹部に埋め込まれた逆導電型Si混晶層とを備えた半導体装置であって、逆導電型Si混晶層が、第1不純物濃度Si混晶層/第2不純物濃度Si混晶層/第3不純物濃度Si混晶層を有し、第2不純物濃度を第1不純物濃度及び第3不純物濃度よりも高くする。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置及びその製造方法

【課題】p型MISトランジスタのゲート絶縁膜の酸化膜換算膜厚の厚膜化を抑制しつつ、p型MISトランジスタの実効仕事関数を増加させて、低閾値電圧を有するn型,p型MISトランジスタを実現する。

【解決手段】半導体装置は、第1,第2のMISトランジスタnTr,pTrを備えている。第1のMISトランジスタnTrは、第1の活性領域10a上に形成され、第1の高誘電率膜14Xaを有する第1のゲート絶縁膜14Aと、第1のゲート電極18Aとを備えている。第2のMISトランジスタpTrは、第2の活性領域10b上に形成され、第2の高誘電率膜14xを有する第2のゲート絶縁膜14Bと、第2のゲート電極18Bとを備えている。第2の高誘電率膜14xは、第1の調整用金属を含む。第1の高誘電率膜14Xaは、第2の高誘電率膜14xよりも窒素濃度が高く、且つ、第1の調整用金属を含まない。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置

【課題】窒化物半導体を用いたノーマリオフ型のトランジスタを備えた半導体装置において、駆動時のゲート電流を低減しつつ、トランジスタの過渡応答特性を安定させる。

【解決手段】半導体装置は、基板101と、基板101の上に積層された複数の窒化物半導体層からなり、且つチャネル領域を含む第1の窒化物半導体層104Sと、第1の窒化物半導体層104Sの上に形成され、且つチャネル領域と逆導電型の第2の半導体層105と、第2の半導体層105に接するように形成され、金属層107からなる導電層と、導電層の上に形成された絶縁体層110と、絶縁体層110の上に形成されたゲート電極111と、第2の半導体層105の両側方に形成されたソース電極108及びドレイン電極109とを備えている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

61 - 80 / 324

[ Back to top ]