Fターム[5F140CF05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 同時工程 (1,387) | SD上とゲート電極上のプラグ (157)

Fターム[5F140CF05]に分類される特許

1 - 20 / 157

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

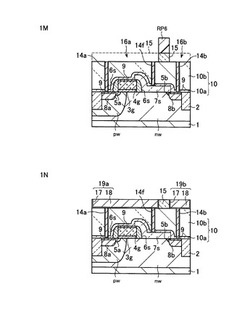

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極断線の確率を下げる。

【解決手段】半導体装置1の製造方法は、シリコン基板2の主面に絶縁体ピラー6を形成する工程と、絶縁体ピラー6の側面に保護膜12を形成する工程と、シリコン基板2の主面にシリコンピラー4を形成する工程と、シリコンピラー4の側面にゲート絶縁膜10を形成する工程と、それぞれシリコンピラー4及び絶縁体ピラー6の側面を覆い、互いに接する第1及び第2のゲート電極11,13を形成する工程とを備える。本製造方法によれば、ダミーピラーとしての絶縁体ピラー6の側面に保護膜12を形成しているので、チャネル用のシリコンピラー4をトランジスタとして加工する際にダミーピラーが削られてしまうことが防止される。したがって、ゲート電極断線の確率を下げることが可能になる。

(もっと読む)

ポータブル電気素子およびデータ処理センタのための低電圧MOSFETを形成する半導体素子および方法

【課題】半導体素子を提供すること。

【解決手段】半導体素子であって、基板と、該基板内に形成された井戸領域と、該基板の表面の上方に形成されたゲート構造と、該ゲート構造に隣接して基板内に形成されたソース領域と、該ソース領域の反対側に該ゲート構造に隣接して該基板内に形成されたドレイン領域と、該ソース領域を通して形成されたトレンチと、該トレンチを通して形成されたプラグと、該トレンチを通して該プラグの上方に形成されたソースタイと、該ソース領域、該ドレイン領域、および該ゲート構造の上方に形成された相互接続構造とを備える、半導体素子。

(もっと読む)

半導体装置

【課題】安定した静電気保護機能を有する半導体装置を提供すること。

【解決手段】半導体装置は、シリコン柱を有するシリコン基板、シリコン柱の側壁に沿って形成されたゲート電極、ゲート電極とシリコン柱との間に形成されたゲート絶縁膜シリコン柱の上部に形成された上部拡散層、及びシリコン基板において上部拡散層より下方に形成された下部拡散層、を有する縦型MOSトランジスタと、下部拡散層と電気的に接続されたパッドと、を備える。サージ電圧が印加された際に下部拡散層と基板との間においてブレイクダウンが発生する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上部拡散層が平面積の狭いものであっても、上部拡散層および上部拡散層上に設けられた配線とのコンタクト抵抗を大きくすることなく、上部拡散層と配線とを接続できる半導体装置を提供する。

【解決手段】柱状半導体5と、柱状半導体5上に形成された上部拡散層15と、上部拡散層15上に形成された接続プラグ24とを備え、上部拡散層15が、平面視島状の複数の島状部を有するものであり、接続プラグ24が、導電材料からなり、前記複数の島状部から選ばれる第1島状部と前記第1島状部に隣接する第2島状部との間の隙間を跨って、前記第1島状部の上面の少なくとも一部から前記第2島状部の上面の少なくとも一部まで連続して配置されている半導体装置とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な電気的特性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜20と、ゲート絶縁膜上に形成されたキャップ膜22と、キャップ膜上に形成されたシリコン酸化膜23と、シリコン酸化膜上に形成された金属ゲート電極24と、金属ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層48とを有している。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】IGBTを構成するバイポーラトランジスタのターンオフ時間を短くし、かつIGBTを構成するバイポーラトランジスタを動作しやすくする。

【解決手段】シンカー層115は第1導電型ウェル102及び第2導電型ドリフト層104それぞれに接しており、かつ第1導電型コレクタ層108から離れている。シンカー層115の表層には、第2導電型拡散層(第2の第2導電型高濃度拡散層)116が形成されている。第2導電型拡散層116はシンカー層115より不純物濃度が高い。第2導電型拡散層116と第1導電型コレクタ層108は、素子分離絶縁膜16を介して互いに分離している。

(もっと読む)

半導体装置およびその製造方法

【課題】CMPによるダミーゲート電極の頭出し工程およびCMPによるメタルゲート電極の形成工程を回避できる製造方法を提供する。

【解決手段】シリサイド膜24S,24D上に選択的に、シリコン膜25S,25Dを形成する工程と、側壁絶縁膜23WA,23WBの間にシリコン基板の表面を露出する凹部23Vを形成する工程と、側壁絶縁膜23WA,23WBの表面および露出されたシリコン基板表面を連続して覆うように、誘電体膜を形成する工程と、シリコン基板上に金属または導電性金属窒化物を含む導電膜を、凹部23Vに誘電体膜を介して充填するように形成する工程と、導電膜をエッチバックし、側壁絶縁膜23WA,23WBの間において凹部23Vを誘電体膜を介して充填するゲート電極を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタを備えた半導体装置において、トランジスタのGIDLを抑制する。

【解決手段】縦型トランジスタを備えた半導体装置に関する。縦型トランジスタは、半導体領域と、半導体領域上に設けられた柱状領域と、柱状領域の側面を覆うように設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、柱状領域の上部に設けられた第1の不純物拡散領域と、半導体領域内に柱状領域を囲むように設けられた第2の不純物拡散領域と、を有する。第1の不純物拡散領域は、柱状領域の側面と離間するように設けられている。

(もっと読む)

高耐圧MOSトランジスタおよび半導体集積回路装置、高耐圧半導体装置

【課題】半導体基板上に他のCMOS素子と集積して形成される高耐圧MOSトランジスタの、工程数を抑制しながら、ドレイン耐圧特性を向上させる。

【解決手段】半導体基板21と、ゲート電極23と、第2の導電型のソース領域21Sと、第2の導電型のドレイン領域21Dと、ソースエクステンション領域21aと、ドレインエクステンション領域21bと、を含み、ソースエクステンション領域21aとドレインエクステンション領域21bとの間にはチャネル領域が形成され、ソース領域21Sおよびソースエクステンション領域21aの下方には第1のウェル21PWが、第1の導電型で、素子分離領域21Iの下端部を超える深さで形成され、第1のウェル21PWの下方には第2のウェル21DNWが第2の導電型で形成され、第1のウェル21PWおよび第2のウェル21DNWは、ドレインエクステンション領域21b、ドレイン領域21Dの下には形成されない。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置の製造方法

【課題】 所望の極浅拡散層を形成することが可能な半導体製造方法を提供する。

【解決手段】

シリコン基板1にイオン注入するイオン注入工程と、イオン注入工程の後に、シリコン

基板1にマイクロ波を照射するマイクロ波照射工程と、マイクロ波照射工程の後に、シリ

コン基板1を熱処理装置に移し、シリコン基板に0.1ミリ以上100m秒以下のパルス

幅の光を照射することにより、シリコン基板1を熱処理する熱処理工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】複数のトレンチを含むトレンチゲート構造のトランジスタにおける特性ばらつきを低減する。

【解決手段】トレンチゲート構造を有するトランジスタを含む半導体装置100において、ゲート幅方向において、複数のトレンチ162は、両側方に形成された素子分離絶縁膜110とそれぞれ接して形成されたトレンチ162aおよびトレンチ162bを含み、トレンチ162aおよびトレンチ162bのゲート幅方向の幅が、これらの間に形成された他のトレンチ162cのゲート幅方向の幅以上となるように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】同一の半導体基板上に、高性能な低電圧MISFET、高信頼なMONOS型不揮発性メモリおよび高電圧MISFETを形成する。

【解決手段】ロジック回路などに使用される低電圧MISFETの形成領域において、キャップ酸化膜をマスクにすることによってダミーゲート電極上にシリサイドが形成されるのを防ぎ、ダマシンプロセスを用いて低電圧MISFETのゲートをhigh−k膜18およびメタルゲート電極20で形成する際の形成工程を簡略化する。また、ダミーゲート電極除去時のRIEによりダメージを受けたゲート絶縁膜を一旦除去し、新たにゲート酸化膜17を形成することで素子の信頼性を確保する。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リークを抑制しながら、キャリアの移動度向上とチャネル中でのキャリア速度の増加を実現することができるトランジスタを提供する。

【解決手段】半導体基板10のチャネル形成領域にチャネル方向に第1の幅を有するSiGe層15が埋め込まれ、チャネル形成領域上にゲート絶縁膜28が形成され、ゲート絶縁膜上に、第1の幅より大きい第2の幅を有してSiGe層の形成領域からはみ出す領域を有するゲート電極29が形成され、チャネル形成領域を挟む半導体基板においてエクステンション領域12を有するソースドレイン領域13が形成されて、電界効果トランジスタが構成されており、エクステンション領域と半導体基板の接合面から伸びる空乏層がSiGe層に達しないようにエクステンション領域とSiGe層が離間されている。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】ソース/ドレイン領域のPN接合部とコンタクト間のリーク電流を抑制する。

【解決手段】半導体基板(1)と、半導体基板(1)に形成されたSTI(Shallow Trench Isolation)構造(2)と、半導体基板(1)に形成され、STI構造(2)に隣接する拡散領域(12)と、層間絶縁膜(15)を貫通して拡散領域(12)とSTI構造(2)とに到達する接続コンタクト(20)と、拡散領域(12)の側面と拡散領域(12)の下の半導体基板(1)の側面に形成され、接続コンタクト(20)と拡散領域(12)の側面とを電気的に絶縁し、かつ、接続コンタクト(20)と半導体基板(1)の側面とを電気的に絶縁する酸化膜(19)とを具備する半導体装置を構成する。その半導体装置では、STI素子分離とソース/ドレイン領域のPN接合部分の間のみに選択的に絶縁膜(酸化膜)を形成している。

(もっと読む)

1 - 20 / 157

[ Back to top ]