Fターム[5F152CD05]の内容

再結晶化技術 (53,633) | 被結晶化層の下方の層 (4,095) | 目的(結晶化のためのもの) (284) | 結晶の種として使用 (62)

Fターム[5F152CD05]に分類される特許

21 - 40 / 62

エピタキシャルシリコンウェーハの製造方法

【課題】エピタキシャル成長時の加熱に伴うスリップが発生せず、ウェーハ表面のボイド欠陥に起因したエピタキシャル膜の表面粗さの低下も解消可能なエピタキシャルシリコンウェーハの製造方法を提供する。

【解決手段】単結晶のシリコンウェーハの表面を研削し、ウェーハ表層に加工変質層を形成後、変質層を高エネルギ光の照射で溶融、固化する。変質層は、単結晶シリコンより吸光係数が高いので、光加熱でウェーハが溶ける前に溶融し、エピタキシャル膜に改質できる。その結果、エピ成長加熱によるスリップが発生せず、ウェーハ表面のボイド欠陥よるエピ膜の表面粗さの低下も解消できる。

(もっと読む)

多結晶シリコンの製造方法、薄膜トランジスタ、その製造方法及びそれを含む有機電界発光表示装置

【課題】薄膜トランジスタ、その製造方法及びそれを含む有機電界発光表示装置を提供する。

【解決手段】基板と、前記基板上に位置するバッファ層と、前記バッファ層上に位置する第1の半導体層及び第2の半導体層と、前記第1の半導体層及び第2の半導体層と絶縁されているゲート電極と、前記第1の半導体層及び第2の半導体層と前記ゲート電極とを絶縁するゲート絶縁膜と、前記ゲート電極と絶縁され、前記第2の半導体層に一部が接続するソース/ドレイン電極とを含み、前記第1の半導体層上部に前記第2の半導体層が位置することを特徴とする薄膜トランジスタ及びその製造方法に関する。

(もっと読む)

薄膜トランジスタ、その製造方法及びそれを含む有機電界発光表示装置

【課題】薄膜トランジスタ、その製造方法及びこれを含む有機電界発光表示装置を提供する。

【解決手段】基板と、前記基板上に位置するバッファ層と、前記バッファ層上に位置する第1半導体層及び第2半導体層と、前記第1半導体層及び第2半導体層と絶縁されるゲート電極と、前記第1半導体層及び第2半導体層と前記ゲート電極とを絶縁するゲート絶縁膜と、前記ゲート電極と絶縁され、前記第2半導体層と一部が接続するソース/ドレインである電極とを含み、前記第1半導体層は前記第2半導体層の下部に位置し、前記第1半導体層の面積は第2半導体層の面積よりも小さいことを特徴とする薄膜トランジスタ及びその製造方法に関する。また、前記薄膜トランジスタを含む有機電界発光表示装置とその製造方法に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体部材が単結晶の半導体材料からなり、特性が良好な半導体装置及びその製造方法を提供する。

【解決手段】単結晶のシリコンからなるシリコン基板11上に絶縁膜12を形成し、絶縁膜12に開口部12aを形成し、絶縁膜12上に開口部12aを介してシリコン基板11と接触するようにアモルファスシリコン膜を形成し、このアモルファスシリコン膜をシリコン基板11を起点として固相エピタキシャル成長させて、その後パターニングする。これにより、開口部12aの直上域から外れた領域の一部に、単結晶のシリコンからなるシード層を形成する。次に、このシード層を覆うようにアモルファスシリコン膜を堆積させ、このアモルファスシリコン膜をシード層を起点として固相エピタキシャル成長させて、単結晶シリコン膜を形成する。そして、この単結晶シリコン膜をパターニングすることにより、シリコンピラー33を形成する。

(もっと読む)

半導体装置の製造方法、トランジスタの製造方法ならびに電気光学装置の製造方法

【課題】結晶シリコン層を得る結晶化技術として、能動層の一部にNi,Co,Fe,Pd,Pt,Cu,Auの金属触媒を導入し、加熱処理を施して結晶化を行い、引き続きエキシマレーザ等によりエネルギーを与えることで種結晶を形成し、非晶質シリコン層領域を結晶化するという発明が提案されているが、この技術を用いた場合、種結晶の面配向を制御することができないという課題がある。

【解決手段】アルミニウム層102上に非晶質シリコン層103を堆積した後、アニールを行うことで層転換を行わせる。同時に非晶質シリコン層103は(111)配向を有する多結晶シリコン層104に変換される。多結晶シリコン層104をパターニングし種結晶として用いて、積層された非晶質シリコン層105をレーザアニールにより結晶化し、結晶シリコン層12を有する半導体装置108の製造方法を提供することが可能となる。

(もっと読む)

歪シリコン膜の製造方法

【課題】 新規な歪シリコン膜の製造方法を提供する。

【解決手段】 (a)基板表面の一部に、複数の凹部を形成する。(b)複数の凹部の各々に、シリコンとは熱膨張係数の異なる絶縁性の膜を埋め込む。(c)絶縁性の膜、及び基板の表面にシリコン膜を形成する。(d)シリコン膜にレーザビームを照射して、シリコン膜をラテラルエピタキシャル成長させるとともに、ラテラルエピタキシャル成長させたシリコン膜に歪を導入する。

(もっと読む)

半導体基板、半導体基板の製造方法、トランジスタ、並びに電気光学装置

【課題】多結晶シリコンを(111)配向を選択的に形成する場合、結晶粒界の位置はランダムに形成されるため、トランジスタのチャネル部分に結晶粒が配置された場合、結晶粒界に存在するトラップ準位の影響により、電気的特性が低下する。また、多結晶領域を形成する単結晶群の大きさは0.5μm程度であり、トランジスタを形成した場合複数の結晶粒界がチャネルに配置されてしまい、同様に電気的特性が低下するという課題がある。

【解決手段】(111)配向を含む第1シリコン層204上に貫通孔206を含む絶縁層205を形成した後、第2シリコン層前駆体207aを積層し、XeClエキシマレーザを用いて第1シリコン層204を種結晶として再結晶工程を行う。これにより、面方位が(111)に揃えられ、且つ10μm程度の大粒径単結晶が得られる。この結晶上にトランジスタを形成することで、電気的特性に優れたトランジスタを提供できる。

(もっと読む)

半導体基板、半導体基板の製造方法、トランジスタ、並びに電気光学装置

【課題】多結晶シリコンを(111)配向を選択的に形成する場合、結晶粒界の位置はランダムに形成されるため、トランジスタのチャネル部分に結晶粒が配置された場合、結晶粒界に存在するトラップ準位の影響により、電気的特性が低下する。また、チャネル部分に発生したホットキャリアを吸収する領域がなく、キンク特性が発生するという課題がある。

【解決手段】(111)配向を含む不純物がドーピングされた第1シリコン層204上に貫通孔206を含む絶縁層205を形成した後、第2シリコン層前駆体207aを積層し、XeClエキシマレーザを用いて第1シリコン層204を種結晶として再結晶工程を行い、面方位が(111)に揃えられた第2シリコン層207を形成する。そして不純物がドーピングされた第1シリコン層204からホットキャリアを引き抜くことで、キンクの発生が抑えられ、且つ電気的特性に優れたトランジスタを提供できる。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】微細化TFTに適用が可能な低抵抗のソース・ドレイン構造を低温プロセスで形成可能な薄膜半導体及びその製造方法を提供すること。

【解決手段】透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成され、側壁に絶縁膜からなるサイドウオールスペーサを有するゲート電極、及び前記ソース領域並びにドレイン領域上にそれぞれ600℃以下の温度で固相成長された、第1導電型の不純物を含む積上げソース多結晶半導体層並びに第1導電型の不純物を含む積上げドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

SOI基板の作製方法

【課題】貼り合わせ不良を低減し、且つ大面積の単結晶半導体膜を形成することを可能とするSOI基板の作製方法を提供することを目的の一とする。

【解決手段】複数の第1の単結晶半導体膜が形成された第1の基板上に、接合層として機能する第1の絶縁膜を形成し、第1の絶縁膜を平坦化した後、第1の絶縁膜上に単結晶半導体基板を貼り合わせて熱処理を行い、第2の単結晶半導体膜を形成する。次いで、第1及び第2の単結晶半導体膜をシード層として第3の単結晶半導体膜を形成し、第3の単結晶半導体膜にイオンを導入して脆化層を形成した後、第3の単結晶半導体膜上に接合層として機能する第2の絶縁層を形成し、第2の基板を第2の絶縁膜上に重ね合わせて熱処理を行い、第2の絶縁膜を介して第2の基板上に、第3の単結晶半導体膜の一部を固定されたSOI基板を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域として用いるエピタキシャル成長結晶からゲート絶縁膜への不純物拡散による信頼性の低下を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、第1の面と、前記第1の面に対して傾斜した第2の面とを有するSiGe結晶層を形成する工程と、前記SiGe結晶層上に非晶質Si膜を形成する工程と、加熱処理を施すことにより、前記SiGe結晶層の前記第1および第2の面をシードとして、前記非晶質Si膜の前記第1および第2の面の近傍に位置する部分を結晶化させてSi結晶層を形成する工程と、前記非晶質Si膜の加熱処理により結晶化しなかった部分を選択的に除去、または薄くする工程と、前記Si結晶層の表面に酸化処理を施すことにより、前記Si結晶層の表面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、を含む。

(もっと読む)

光電変換装置の製造方法

【課題】限りある資源を有効活用しつつ、優れた光電変換特性を有する光電変換装置を提供する。

【解決手段】単結晶半導体基板の一表面から1000nm未満の深さの領域に脆化層を形成し、且つ単結晶半導体基板の一表面側に第1不純物半導体層、第1電極を形成する。第1電極と支持基板とを重ね合わせて貼り合わせた後、脆化層又は当該脆化層の近傍を分離面として単結晶半導体基板を分離させることにより、支持基板上に第1単結晶半導体層を形成する。第1単結晶半導体層の分離面上に非晶質半導体層を形成し、熱処理を行い、非晶質半導体層を固相成長させて第2単結晶半導体層を形成する。第2単結晶半導体層上に、第1不純物半導体層とは逆の導電型の第2不純物半導体層を形成し、第2不純物半導体層上に第2電極を形成する。

(もっと読む)

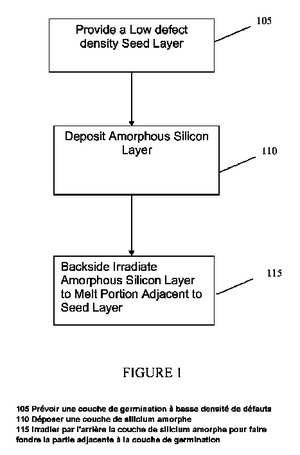

エピタキシャルに配向された厚膜を調製するための調製システムおよび方法

開示される内容は、エピタキシャルに配向された結晶性厚膜を生成するための、薄膜のレーザー結晶化の利用に関する。1つ以上の実施形態において、厚い結晶性膜を調製する方法は、結晶化のための膜を基板上に提供する工程であって、前記基板の少なくとも一部はレーザー照射に対して実質的に透過性であり、前記膜は、支配的な表面結晶配向性を有するシード層と、前記シード層の上方に配置された最上層とを含む、工程と、パルス状レーザーを用いて前記膜を前記基板の後側から照射して、前記最上層の第2の部位が固形のままの状態で、前記最上層の第1の部位を前記シード層との界面において溶融させる工程と、前記最上層の前記第1の部位を再度固化させて、前記シード層とエピタキシャルな結晶性レーザーを形成して、これにより、熱を解放して前記最上層の隣接部位を溶融する工程とを含む。  (もっと読む)

(もっと読む)

結晶化方法および活性半導体膜構造体

【課題】結晶化に続いて、所定の位置に残すことができ、その後の処理工程を妨げない手段によって種結晶を横成長させる方法並びに該方法を用いた構造体を提供する。

【解決手段】第1の半導体結晶をエッチングして種結晶領域を形成し、その上に、種結晶領域を露出させる開口部が設けられた絶縁体層、および第2の半導体膜を形成してレーザアニールし、種結晶から横成長を行う。その後、種結晶領域の上の第2の半導体膜を除去し、残っている第2の半導体膜中のトランジスタ活性領域を形成する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタを有する表示装置の作製方法

【課題】電気特性が優れた薄膜トランジスタ、及びそれを有する表示装置を作製する方法を提案する。

【解決手段】ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に微結晶半導体及び非晶質半導体を有する半導体膜を形成し、半導体膜の非晶質半導体を選択的に除去して微結晶半導体を残存させ、微結晶半導体を種としてシリコンまたはゲルマニウムを含む堆積性ガスを用いて結晶成長させて微結晶半導体膜を形成して、ゲート絶縁膜及び微結晶半導体膜の界面における結晶性を高める。次に、ゲート絶縁膜との界面における結晶性が高められた微結晶半導体膜をチャネル形成領域として用いて薄膜トランジスタを形成する。

(もっと読む)

半導体素子のための緩衝化基板

【課題】製造時間と製造価格を増加することなく多結晶シリコン粒径の微小化と均一化を行なうための技術を提供する。

【解決手段】基板100上に形成したシリコン層104をレーザビーム106の照射によって結晶化して多結晶シリコン層108を得る半導体装置などに用いられ、基板100とシリコン層104との間にバッファ層102が形成されている。バッファ層102を有するこのようなバッファ化基板において、該バッファ層102は、基板100の限界温度よりも高い融点を有し、さらに、シリコン層104の結晶化に際し、バッファ層102上に均一なシリコン結晶粒子を形成するためシリコン層104の核生成密度を規定し、かつシリコン層104の結晶化過程における等方粒成長の基礎として機能する。

(もっと読む)

半導体装置の製造方法

【課題】

本発明は、低温下で結晶性の良好な単結晶および多結晶を提供することを目的とする。また、本発明は、固相成長法を用い、信頼性の高い半導体装置を提供することを目的とする。

【解決手段】

本発明では、非晶質半導体薄膜を基板あるいは絶縁膜上に堆積するにあたり、特に、その膜を構成する主元素からなる非晶質膜の平均原子間隔分布が、単結晶の平均原子間隔分布にほぼ一致するように形成し、これに再結晶化エネルギーを付与し固相成長を行い単結晶半導体薄膜3を形成する。

(もっと読む)

レーザアニール方法及びレーザアニール装置

【課題】半導体膜の結晶化プロセスにおいて均質な核を発生させることにより結晶粒径の揃った多結晶半導体膜を形成する。

【解決手段】半導体膜5の下地層又はキャップ層として光触媒層4を形成する。光触媒層4に吸収される波長をもつ励起光8を光触媒層4に照射しながら、半導体膜5にレーザ光1を照射して、半導体膜5を溶融及び固化させることにより結晶化させる。この方法により、光触媒層4の超親水作用によって半導体融液の濡れ性が改善する。このため、半導体膜5の融点近傍で、半導体膜5と光触媒層4の界面に結晶核を発生させることができ、これにより結晶粒径の揃った多結晶半導体膜を形成することができる。

(もっと読む)

3次元集積回路装置及びその製造方法

【課題】ガラス基板上に薄膜半導体層を形成した3次元集積回路装置を提供する。

【解決手段】ガラス基板11上に、単結晶もしくは準単結晶の薄膜半導体層13,16が、層間絶縁層14を介して複数層積層形成され、複数層の薄膜半導体層13,16のうち1層以上に能動素子Tr21,Tr22が形成されている3次元集積回路装置10を構成する。

(もっと読む)

半導体装置の製造方法、半導体装置、集積回路、電気光学装置および電子機器

【課題】TFTで使用される半導体膜に含まれる、個々の結晶粒の結晶方位にバラツキがあると、トランジスタの特性バラツキが引き起こされる。トランジスタの特性にバラツキが生じると、大きな余裕を持って回路設計を行う必要が生じ回路特性を向上させることが困難となる。

【解決手段】第1シリコン膜を、結晶方位が揃えられた第1多結晶シリコン膜300に改質した後、平面視にて電気的に分離し、多結晶シリコン島302を形成する。次に、多結晶シリコン島302の一部を露出させる微細貫通孔126が開口されたバッファ絶縁膜を形成し、その上に非晶質シリコン膜13を形成する。そして、レーザアニールにより多結晶シリコン島302と同じ面方位に揃えられたシリコン結晶膜155を形成することで特性が揃えられたTFTを提供する。

(もっと読む)

21 - 40 / 62

[ Back to top ]