Fターム[5F152LL02]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 気相 (1,473)

Fターム[5F152LL02]の下位に属するFターム

Fターム[5F152LL02]に分類される特許

1 - 20 / 128

エピタキシャルウェーハとその製造方法

レーザー光線の出力設定方法およびレーザー加工装置

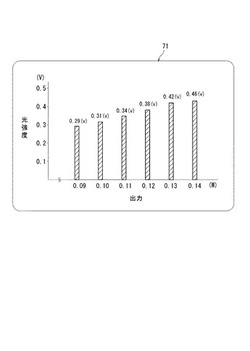

【課題】バッファー層にレーザー光線を照射することによりサファイア基板を剥離する際に、レーザー光線の適正な出力を設定する出力設定方法およびレーザー加工装置を提供する。

【解決手段】エピタキシー基板の表面にバッファー層を介して積層された光デバイス層にレーザー光線を照射することにより、エピタキシー基板を剥離する際のレーザー光線の出力を設定する方法であって、エピタキシー基板の裏面側からバッファー層にレーザー光線を、出力を変更しつつ照射するレーザー光線照射工程と、レーザー光線照射工程によって発生するプラズマにおけるバッファー層を形成する物質の波長域の光強度を、バッファー層に照射したレーザー光線の出力に対応して表示手段に表示するプラズマ光強度表示工程と、表示手段に表示されたレーザー光線の出力に対応したプラズマの光強度に基づいて、適正なレーザー光線の出力を設定する出力設定工程とを含む。

(もっと読む)

エピタキシャルウエーハ及びその製造方法

【課題】 本発明は、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハ及びその製造方法を提供することを目的とする。

【解決手段】 撮像素子製造用のエピタキシャルウエーハを製造する方法であって、前記エピタキシャル層の成長前に、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算し、前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長することを特徴とするエピタキシャルウエーハの製造方法。

(もっと読む)

エピタキシャルウェーハとその製造方法

【課題】歪み層形成に供されるウェーハで転位発生に対して耐性が高いエピタキシャルウェーハを提供する。

【解決手段】シリコンエピタキシャル層表面の酸素濃度が1.0×1017〜12×1017atoms/cm3とされてなるエピタキシャルウェーハの製造方法であって、酸素濃度設定熱処理の処理温度Xと処理時間Yとが、処理温度Xが800℃〜1400℃の範囲、処理時間Yが180min以下で、かつ、

Y ≧ 1.21×1010 exp(−0.0176X)

の関係を満たすように設定される。

(もっと読む)

炭化珪素基板の製造方法および炭化珪素半導体装置の製造方法

【課題】炭化珪素基板の表面を保護することができる方法を提供する。

【解決手段】炭化珪素基板80が準備される。2μg/m3以上の二酸化窒素濃度を有する雰囲気に炭化珪素基板80をさらすことによって、炭化珪素基板80上に酸化膜70が形成される。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】チャネル移動度の低下を抑制しつつ閾値電圧を制御する炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の炭化珪素半導体装置の製造方法は、(b)二酸化珪素膜が形成された炭化珪素基板を窒化処理する工程と、(c)窒化処理された炭化珪素基板を水蒸気を含んだ酸素雰囲気で熱処理する工程とを備える。工程(c)は、(c1)窒化処理された炭化珪素基板を投入した熱処理炉の温度を不活性ガス雰囲気中で昇温又は降温する工程を含む。工程(c1)は、窒化処理直後のチャネル移動度をμch、昇温又は降温開始時刻をt=0、熱処理開始時刻をt=t1、熱処理終了時刻をt=t2、熱処理炉からの基板取出時刻をt=t3、ボルツマン定数をk、時刻tにおける熱処理炉の温度をT(K)とした場合に、式(1)により求められる炭化珪素基板中のチャネル移動度の低下率が10%以下となるように昇温速度及び/又は降温速度を決定する。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、シリコンエピタキシャル層に結晶欠陥が生じ易いという問題がある。

【解決手段】半導体装置1は、シリコン基板10、歪み付与層20、シリコン層30、FET40、および素子分離領域50を備えている。シリコン基板10上には、歪み付与層20が設けられている。歪み付与層20上には、シリコン層30が設けられている。歪み付与層20は、シリコン層30中のFET40のチャネル部に格子歪みを生じさせる。シリコン層30中には、FET40が設けられている。FET40は、ソース・ドレイン領域42、SD extension領域43、ゲート電極44およびサイドウォール46を含んでいる。ソース・ドレイン領域42と上述の歪み付与層20とは、互いに離間している。FET40の周囲には、素子分離領域50が設けられている。素子分離領域50は、シリコン層30を貫通して歪み付与層20まで達している。

(もっと読む)

窒化ガリウム基板

【課題】量産に用い得る厚さと面積を確保しながら、容易な生産方法でかけやわれの発生を抑制してオリエンテーションフラットを形成することを目的とする。

【解決手段】窒化ガリウム結晶体27から、ファセット15を有する硬質の立体構造物14を陵線等に平行に除去することで、欠けや割れの発生を抑制した窒化ガリウム基板を提供できる。しかも、ファセット15を有する硬質の立体構造物14の陵線等は特有の結晶方位を有し、かつ、明瞭であるので、立体構造物14の陵線等に平行に切断加工した窒化ガリウム結晶体27の切断線21をデバイス加工の基準線となるオリエンテーションフラットに用いることができる。

(もっと読む)

真性半導体層を備えたウェーハ

【課題】ウェーハを製造するための新規な方法を提供する。

【解決手段】本発明は、ウェーハを製造するための方法に関し、この方法は、半導体基板上にドープト層を設けるステップと、ドープト層上に第1の半導体層を設けるステップと、第1の半導体層上に埋込み酸化物層を設けるステップと、埋込み酸化物層上に第2の半導体層を設けるステップと、を備える。

(もっと読む)

トレンチ埋め込みエピタキシャル成長条件の最適化方法

【課題】トレンチ埋め込みエピタキシャル成長の制御パラメータを変更した際にエピタキシャルの成長反応の変化傾向を簡便に知ることができ、結果として、最適な成長条件を簡便に見つけ出すことが可能な、トレンチ埋め込みエピタキシャル成長条件の最適化方法を提供する。

【解決手段】シリコンソースガスにエッチングガスを混合した混合ガスを原料ガスとし、この原料ガスをH2キャリアガスで流通させることにより、シリコン基板表面に形成したトレンチ内部にエピタキシャル層を成長させてトレンチ内部をエピタキシャル層で埋め込む工程を含む半導体基板の製造方法における、トレンチ内部をエピタキシャル層で埋め込む際のエピタキシャル成長の最適条件を求める方法であって、ある特定のアスペクト比のトレンチ内部を埋め込む際のエピタキシャル成長の最適条件をエピタキシャル成長速度のH2キャリアガスの流量依存性により求めることを特徴とする。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法

【課題】 エピタキシャル成長中における基板からエピタキシャル層へのオートドープ量を抑制し、抵抗分布及び膜厚分布の良好なエピタキシャルウェーハを得ることができるシリコンエピタキシャルウェーハの製造方法を提供することを目的とする。

【解決手段】 シリコン単結晶基板上にシリコン単結晶をエピタキシャル成長させて、エピタキシャル層を積層するシリコンエピタキシャルウェーハの製造方法において、抵抗率が0.5mΩ・cm以上10.0mΩ・cm以下であり、リンまたはヒ素がドープされている前記シリコン単結晶基板上に、成長速度を3μm/分以上15μm/分以下として、抵抗率が0.5Ω・cm以上2000Ω・cm以下である前記エピタキシャル層を成長させることを特徴とするシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

炭化珪素半導体基板、炭化珪素半導体装置、炭化珪素半導体基板の製造方法および炭化珪素半導体装置の製造方法

【課題】縦型の半導体素子の形成が可能で、かつ高品質な単結晶SiC基板の使用量を減らすことが可能であるSiC半導体基板を提供する。

【解決手段】支持基板1と、支持基板1の表面に接合されることにより支持基板1と一体化された単結晶SiC層2と、を有するSiC半導体基板において、支持基板1を、単結晶SiCより比抵抗が低い材料を用いて構成された基板1aと、当該基板1aを被覆するSiC組成薄膜1bとを備えたものとする。

(もっと読む)

裏面照射型固体撮像素子用エピタキシャル基板およびその製造方法

【課題】裏面照射型固体撮像素子をより高い歩留まりで製造することが可能なエピタキシャル基板およびその製造方法を提供する

【解決手段】本発明の裏面照射型固体撮像素子用エピタキシャル基板100は、炭素、または、炭素および窒素が添加され、抵抗率が100Ω・cm未満であるp型シリコン基板1と、該p型シリコン基板上のp型第1エピタキシャル層2と、該第1エピタキシャル層上のp型またはn型第2エピタキシャル層3と、を有し、前記第1エピタキシャル層2は、p型不純物のピーク濃度が2.7×1017atoms/cm3以上1.1×1019atoms/cm3未満であることを特徴とする。

(もっと読む)

MOSゲート型炭化珪素半導体装置の製造方法

【目的】チャネル移動度を大きくし、チャネル抵抗を低減できるMOSゲート型炭化珪素半導体装置の提供。

【構成】トレンチの側壁に接するゲート酸化膜とチャネル反転層表面との間に他導電型シリコン半導体層が形成されるMOSゲート型炭化珪素半導体装置であって、他導電型シリコン半導体層がアモルファスシリコン層で形成し、レーザー光を前記アモルファスシリコン層に対して前記MOSゲート型炭化珪素半導体装置のチャネル電流が流れる方向と交差しない方向へスキャンしてアモルファスシリコン層をポリシリコンに変換する。

(もっと読む)

基板製造方法及び該方法によって得られた基板

【課題】活性材料要素をしじたいに移し替えるコストを低減する。

【解決手段】第1の材料から成る活性要素の表面上における支持体2への接合対象部位に非晶質材料6を蒸着する工程を備え、第2の材料が第1の材料よりも希少ではないことを特徴とする。更に、特に光学、電子工学又は光電子工学用の基板を製造する際に第1の材料から成る活性要素8を第2の材料から成る支持体2の表面に接合する操作を行う基板製造方法にも関する。この方法は、活性要素8又は支持体2が少なくともその表面上の接合対象部位に多結晶材料を含み、接合に先立ち、この多結晶材料を含む表面上に非晶質材料6の層を形成することを特徴とする。

(もっと読む)

半導体基板の製造方法

【課題】表面保護膜の剥離ムラやウォーターマークの発生、及びSi基板への不純物吸着等の問題を抑制することにより、固体撮像装置を作製した場合に暗電流の白傷欠陥の発生を効果的に防止可能なエピタキシャル基板の製造方法を提供する。

【解決手段】SiからなるCZ基板11上に、アクリル樹脂をベースポリマーとする有機膜12を形成する。有機膜12を介してCZ基板11に炭素イオンを注入し、CZ基板11中に炭素注入領域13を形成する。その後、有機膜12を比較的強い酸化剤であるSPM(硫酸過酸化水素水)の溶液によるウェットエッチング、若しくは水素ガスを用いたドライエッチングで洗浄して除去する。その後はCZ基板11の表面にSi材料を用いてSiエピタキシャル層14を形成し、エピタキシャル基板を得る。

(もっと読む)

単結晶炭化珪素基板を有する複合基板

【課題】複合基板を用いた半導体装置の製造において単結晶炭化珪素基板の間の隙間に起因した工程変動を抑制する。

【解決手段】第1の単結晶炭化珪素基板11の第1の辺S1と、第2の単結晶炭化珪素基板12の第2の辺S2とが直線状に並ぶように、第1の単結晶炭化珪素基板11の第1の頂点P1と、第2の単結晶炭化珪素基板12の第2の頂点P2とが互いに突き合わされている。また第1の辺の少なくとも一部と、第2の辺の少なくとも一部とが、第3の単結晶炭化珪素基板13の第3の辺S3に突き合わされている。

(もっと読む)

炭化珪素基板を有する複合基板

【課題】複合基板が有する複数の炭化珪素基板の間の隙間への異物の残留を防ぐことができる複合基板を提供する。

【解決手段】第1の炭化珪素基板11は、支持部30に接合された第1の裏面B1と、第1の裏面B1に対向する第1の表面T1と、第1の裏面B1および第1の表面T1をつなぐ第1の側面S1とを有する。第2の炭化珪素基板12は、支持部30に接合された第2の裏面B2と、第2の裏面B2に対向する第2の表面T2と、第2の裏面B2および第2の表面T2をつなぎ、第1の側面S1との間に隙間GPを形成する第2の側面S2とを有する。閉塞部21は隙間GPを閉塞している。

(もっと読む)

炭化珪素基板を有する複合基板の製造方法

【課題】炭化珪素基板を有する複合基板を用いた半導体装置の製造工程において、炭化珪素基板の間の隙間に起因した工程変動を抑制する。

【解決手段】支持部30と第1および第2の炭化珪素基板11、12とを有する接合基板が準備される。第1の炭化珪素基板11は、支持部30に接合された第1の裏面と、第1の裏面に対向する第1の表面と、第1の裏面および第1の表面をつなぐ第1の側面とを有する。第2の炭化珪素基板12は、支持部30に接合された第2の裏面と、第2の裏面に対向する第2の表面と、第2の裏面および第2の表面をつなぎ、第1の側面との間に隙間を形成する第2の側面とを有する。隙間を充填する充填部40が形成される。次に第1および第2の表面が研磨される。次に充填部40が除去される。次に隙間を閉塞する閉塞部が形成される。

(もっと読む)

結晶欠陥の除去方法

【課題】エピタキシャル成長法により堆積させたSiC層の表面から深い位置に形成された結晶欠陥でも、確実に除去することができる方法を提供する。

【解決手段】単結晶SiCからなる半導体基板1表面にエピタキシャル層2を積層させて形成したSiC基板の表面にレジスト膜12を形成し、基板裏面から紫外線を照射することで、表面のレジスト膜12を露光する。結晶欠陥11のある部分は、レジスト膜12は露光されないため、開口が形成される。その開口部内にイオン注入することで、エピタキシャル層2、半導体基板1を高抵抗化し、結晶欠陥を除去する。最後に、レジスト膜12を除去することで、半導体装置を形成することができるSiC基板が得られる。

(もっと読む)

1 - 20 / 128

[ Back to top ]