Fターム[5F152LL03]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 気相 (1,473) | CVD、VPE (918)

Fターム[5F152LL03]の下位に属するFターム

プラズマCVD (98)

MOCVD、MOVPE (333)

Fターム[5F152LL03]に分類される特許

201 - 220 / 487

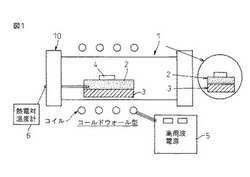

炭化珪素エピタキシャル用基板の製造方法

【課題】カーボンの供給を抑えた反応室内条件下でのエピタキシャル成長用基板として好適な炭化珪素基板の製造方法を提供する。

【解決手段】カーボンの供給を抑えた反応室1内条件下、炭化珪素基板4をアルゴン雰囲気下にてエピタキシャル成長温度まで昇温させて基板4の表面をアルゴン処理し、エピタキシャル成長温度に到達した段階で昇温のための加熱およびアルゴンガス供給を停止する炭化珪素エピタキシャル用基板4の製造方法。

(もっと読む)

多層膜構造体およびその形成方法

【課題】半導体素子用の多層膜構造体を基板上に形成する多層膜構造体であって、大きな伸張歪を半導体層に印加できる多層膜構造体の形成方法を提供する。

【解決手段】半導体素子用の多層膜構造体10を基板上に形成する際に、基板11上に、当該基板11を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、圧縮歪を有する圧縮歪半導体層12を形成する。その圧縮歪半導体層12の上方に、圧縮歪半導体層12を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、無歪の無歪半導体層13を積層する。圧縮歪半導体層12の圧縮歪を緩和させることにより、無歪半導体層13に伸張歪を印加する。それにより、大きな伸張歪を無歪半導体層13に印加することができる。

(もっと読む)

薄膜形成装置および薄膜形成方法

【課題】高い品質のGaを含む化合物半導体層をより容易に形成できるようにする。

【解決手段】原料ガス供給部104が供給する原料ガスにガリウム(Ga)を接触させるガリウム配置部105を備える。ガリウム配置部105は、例えば、原料ガス供給部104が供給する原料ガスを通過させる経路と、この経路に配置された金属Gaと、この金属Gaを加熱する加熱部とを備えるものである。従って、原料ガス供給部104より供給される原料ガスに含まれているIn原料ガスは、ガリウム配置部105を通過することで、例えば50℃に加熱された金属Gaに接触し、この後、基板Wの表面に供給されることになる。

(もっと読む)

炭化珪素基板、半導体装置、配線基板及び炭化珪素の製造方法

【課題】電子素子等のデバイスを実装するには、炭化珪素基板の高周波損失が大きく、実際には電子素子を炭化珪素基板に実装できなかった。

【解決手段】20GHzにおける高周波損失が2.0dB/mm以下の炭化珪素基板であれば、電子素子を実装して十分に動作させることができることを見出し、2.0dB/mm以上の高周波損失特性を有する炭化珪素基板を2000℃以上で加熱する。この熱処理により20GHzにおける高周波損失を2.0dB/mm以下にすることができた。また、ヒーターに窒素を流さないで、CVDにより炭化珪素基板を作製することによって高周波損失を2.0dB/mm以下にすることができた。

(もっと読む)

半導体結晶成長用基板および半導体結晶

【課題】結晶欠陥の少ない半導体層を形成する。

【解決手段】面方位が(111)であるSiからなる半導体結晶成長用基板本体11の外周部に膜厚が100nmの窒化シリコンからなる保護膜14を形成する。すなわち、半導体結晶成長用基板本体11の側面12および半導体結晶成長用基板本体11の表面13の最外周から2mmまでの部分に保護膜14を形成する。また、半導体結晶成長用基板本体11の表面13の保護膜14が形成されていない領域上にAlNからなるバッファ層21を形成し、バッファ層21上に膜厚が3μmのGaN結晶からなる半導体層22を形成する。

(もっと読む)

SOI基板の製造方法

【課題】SOI基板のSOI層上に良質なシリコンエピタキシャル層を積層させるのと同時にSOI基板の接合強度も上げることができるSOI基板の製造方法を提供することを目的とする。

【解決手段】ボンドウェーハの表面から水素イオン、希ガスイオンの少なくとも一種類のガスイオンをイオン注入してイオン注入層を形成し、前記ボンドウェーハのイオン注入した表面とベースウェーハの表面とを酸化膜を介して貼り合わせた後、前記イオン注入層でボンドウェーハを剥離させることによりSOI層を有するSOI基板を作製し、該SOI層を有するSOI基板に水素を含む還元性雰囲気もしくは塩化水素ガスを含む雰囲気で熱処理を行い、その後前記SOI層の表面をCMPで研磨した後に、前記SOI基板のSOI層上にシリコンエピタキシャル層を成長させることを特徴とする厚膜SOI層を有するSOI基板の製造方法を提供する。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】炭化珪素半導体装置のpベースオーミックコンタクトは、高濃度イオン注入により形成されるp++層と金属電極とで構成される。高濃度イオン注入を室温で行うと、p++層の結晶が著しく劣化しプロセス不良の原因となるため、高温中で注入を行う方法が用いられる。デバイスのスイッチング損失等の観点から、pベースオーミックコンタクト抵抗率はより低いことが望ましい。公知技術では、イオン注入温度と、オーミックコンタクト抵抗率及びプロセス不良に関する、詳細な関係については言及されていない。

【解決手段】上記イオン注入工程に於いて、炭化珪素ウェハの温度を175〜300℃、望ましくは175〜200℃に保持しておく。175〜300℃でのイオン注入により形成されるp++領域を用いたpベースオーミックコンタクト抵抗率は、300℃を超える温度でイオン注入した場合よりも低くなる。又、プロセス不良も発生しない。

(もっと読む)

単結晶薄膜を有する基板の製造方法

【課題】特別な基板を用いなくても結晶欠陥がほとんど無い単結晶薄膜を有する基板を容易に製造することができる方法を提供することを目的とする。

【解決手段】少なくとも、ドナー基板とハンドル基板を準備する工程Aと、前記ドナー基板上に単結晶層を積層成長させる工程Bと、前記単結晶層が形成されたドナー基板の単結晶層中にイオン注入してイオン注入層を形成する工程Cと、前記イオン注入されたドナー基板の単結晶層の表面と前記ハンドル基板の表面を貼り合わせる工程Dと、前記貼り合わせられたドナー基板の前記単結晶層中のイオン注入層で剥離する工程Eとにより前記ハンドル基板上に単結晶薄膜を形成し、少なくとも、前記単結晶薄膜が形成されたハンドル基板をドナー基板として前記A〜Eの工程を繰り返すことを特徴とする単結晶薄膜を有する基板の製造方法を提供する。

(もっと読む)

ヘテロエピタキシャル層を備えた半導体ウェハ及び前記ウェハの製造方法

【課題】バウの制御のためだけでなく、SiGeエピタキシャル層の品質を改善するために、特にSi基板上に堆積されたSiGe層のクロスハッチ及び表面ラフネスを低減するために、背面層によって形成された応力を用いる適切な解決策を提供すること。

【解決手段】第1の面及び第2の面を有する基板10、前記基板の第1の面に堆積された完全に又は部分的に緩和されたヘテロエピタキシャル層20、及び前記基板の第2の面に堆積された応力相殺層30を有する、半導体ウェハ。

(もっと読む)

基板の製造方法

【課題】III族窒化物の結晶体の基板を製造する際における剥離バッファー層をエッチングするための時間を短縮する方法を提供する。

【解決手段】基板の製造方法は、下地基板の上にバッファー層を形成するバッファー層形成工程S1と、バッファー層の上に、バッファー層の一部を覆うマスクパターンを形成するマスクパターン形成工程S2と、バッファー層及びマスクパターンを覆うように、III族窒化物の結晶体を成長させる成長工程S5と、マスクパターンの第1のエッチャントを用いてマスクパターンを選択的にエッチングすることにより、バッファー層の第2のエッチャントを供給するための経路を形成する経路形成工程S6と、経路を介して第2のエッチャントを供給してバッファー層を選択的にエッチングすることにより、結晶体を下地基板から分離する分離工程S7とを備える。

(もっと読む)

複合半導体基板とその製造方法

【課題】複合半導体基板において、Si基板とその上の窒化物系半導体層との応力を低減することにより、窒化物系半導体層中の欠陥密度を低くするとともに、複合半導体基板の反り量を小さくする。

【解決手段】複合半導体基板は、(111)面方位を有しかつ複数の凸部が形成された一主面を有するシリコン基板(101)と、その一主面を覆う窒化物系半導体層(102)とを含み、複数の凸部間に空隙(103)が存在していることを特徴としている。このような複合基板においては、異種材料のシリコンと窒化物系半導体を含むことによる応力を低減することができ、窒化物系半導体層中の欠陥密度を低く抑えることと複合基板の反りを小さくすることができる。

(もっと読む)

窒化ガリウムまたはガリウムおよびアルミニウム窒化物の層を製造する方法

本発明は、AlxGa1−xN(式中、0≦x≦3)の組成を有する窒化物の無亀裂単結晶質層(5)を、該層中に引張応力を発生しそうな基材(1)上に形成する方法に関し、該方法は、a)該基材(1)上に核形成層(2)を形成する工程、b)該核形成層(2)上に単結晶質中間層(3)を形成する工程、c)該中間層(3)上に単結晶質種層(4)を形成する工程、d)該種層(4)上にAlxGa1−xN窒化物の単結晶質層(5)を形成する工程を含んでなる。この方法の特徴は、−中間層(3)の材料がアルミニウムおよびガリウム窒化物であり、−種層(4)の材料が、ホウ素含有量が0〜10%であるAlBN化合物であり、−種層(4)の厚さと中間層(3)の厚さとの比が0.05〜1であり、−種層(4)を形成する温度が、該無亀裂単結晶質AlxGa1−xN窒化物層(5)を形成する温度より50〜150℃高いことである。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】性能を確保しながらコストを低減することができる半導体装置の製造方法を提供する。

【解決手段】貫通穴2が形成された基板1上にAlN層3、GaN層4、i−AlGaN層5、n−AlGaN層6及びn−GaN層7を形成する。更に、ソース電極9s、ドレイン電極9d及びゲート電極9gを形成し、半導体素子を形成する。その後、HF溶液中において、貫通穴2に向けて紫外線を照射することにより、AlN層3を基板1から分離する。その後、AlN層3を除去し、GaN層4の裏面に絶縁性の基板を貼り合わせる。

(もっと読む)

半導体装置の製造方法

【課題】Si系基板上に結晶性の良いSi系単結晶をエピタキシャル成長させることのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、酸化物からなる部材を備えたSiを主成分とする半導体基板の表面をSiおよびGeのうちの少なくともいずれか1つを含むハロゲン含有ガスに曝す工程と、前記半導体基板の前記表面をハロゲン含有ガスに曝し始めた後、前記表面をハロゲンを含まないSi含有ガスおよびハロゲンを含まないGe含有ガスのうち少なくともいずれか1つを含む雰囲気に曝し、前記表面にSiおよびGeのうち少なくともいずれか1つを含む結晶膜をエピタキシャル成長させる工程と、を含む。

(もっと読む)

歪みシリコン層が形成されたシリコンウェーハ及びその製造方法

【課題】シリコン以外の元素の層を堆積して形成していなくても十分な歪み量の歪みシリコン層を有するシリコンウェーハ及びその製造方法を低コストで提供することを目的とする。

【解決手段】歪みシリコン層を有するシリコンウェーハの製造方法であって、少なくとも、シリコンウェーハにイオンを注入することによって該シリコンウェーハの表面層をイオン注入層とし面内方向の格子を歪ませた後、前記シリコンウェーハのイオン注入された面上にシリコンを気相成長させることにより歪みシリコン層を成長させることを特徴とする歪みシリコン層を有するシリコンウェーハの製造方法を提供する。

(もっと読む)

ナノ構造処理のための導電性補助層の形成及び選択的除去

一又は複数のナノ構造の作成方法が開示されており、当該方法は:基板の上部表面上に導電層を形成すること;導電層上に触媒のパターン層を形成すること;触媒層上に一又は複数のナノ構造を成長させること;及び一又は複数のナノ構造の間及び周囲の導電層を選択的に除去することを含んでなる。デバイスもまた開示されており、該デバイスは、基板、ここで基板は一又は複数の絶縁領域によって隔てられた一又は複数の露出金属島を含んでなる;一又は複数の露出金属島又は絶縁領域の少なくともいくつかを覆う基板上に配された導電性補助層;導電性補助層上に配された触媒層;及び触媒層上に配された一又は複数のナノ構造を含んでなる。 (もっと読む)

結晶基板およびGaN系結晶膜の製造方法

【課題】GaN系半導体デバイスの結晶成長用に適した、欠陥密度の小さい高品質のGaN系結晶膜連続膜を備えた結晶基板を得る。

【解決手段】GaN系半導体デバイス形成用基板として用いる結晶基板において、表面がC面のサファイア基板101と、該サファイア基板101上に形成されたGaNバッファ層102と、該GaNバッファ層102上に形成されたエピタキシャル成長GaN層103と、該エピタキシャル成長層103上に形成された、複数の開口部105を有するSiO2膜104と、該SiO2膜104の開口部105にGaN系化合物の選択再結晶化により形成された複数の島状GaN系結晶11と、該島状GaN系結晶11を核とするGaN系結晶の成長により形成されたGaN系結晶連続膜12とを備えた。

(もっと読む)

シリコンの結晶化方法、接合体、半導体装置の製造方法および半導体装置

【課題】比較的低温下で、結晶粒や成長方向の制御を確実に行うことができ、これにより半導体特性に優れたポリシリコン層を効率よく形成可能なシリコンの結晶化方法、熱処理を施すことにより良好な結晶化がなされる非晶質部を備える接合体、前記結晶化方法により形成された半導体部を備える半導体装置を製造する方法、および、この方法により製造された半導体装置を提供すること。

【解決手段】本発明のシリコンの結晶化方法は、a−Si膜30a(非晶質部)と、c−Siの種結晶30cとを用意する工程と、a−Si膜30aの表面と種結晶30cの表面に、それぞれエネルギーを付与する工程と、a−Si膜30aと種結晶30cとを接合し接合体305を得る工程と、接合体305を加熱することにより、a−Si膜30aを結晶化する工程とを有する。これにより、a−Si膜30aと種結晶30cとの接合界面が成長核となって結晶化が進行する。

(もっと読む)

単結晶オキシカルコゲナイド系薄膜の成長方法、半導体積層構造体、半導体装置の製造方法および半導体装置

【課題】薄膜間の界面が急峻で良質な単結晶オキシカルコゲナイド系薄膜を成長させることができる単結晶オキシカルコゲナイド系薄膜の成長方法を提供する。

【解決手段】YSZ基板やMgO基板などからなる基板101上にパルス・レーザ・デポジション法やスパッタリング法などによりアモルファスオキシカルコゲナイド系薄膜102を成長させ、このアモルファスオキシカルコゲナイド系薄膜102を反応性固相エピタキシャル成長法により結晶化させることにより単結晶オキシカルコゲナイド系薄膜103を形成する。この単結晶オキシカルコゲナイド系薄膜103上に溶液気化CVD法により単結晶オキシカルコゲナイド系薄膜104を成長初期からエピタキシャル成長させる。

(もっと読む)

半導体膜の製造方法、半導体装置の製造方法、電子機器の製造方法、半導体膜、半導体装置および電子機器

【課題】特性を向上させた炭化シリコン膜(半導体膜)の製造方法を提供する。

【解決手段】第1シリコン膜S1上に炭素源ガスを供給することにより前記シリコン膜上に第1炭化シリコン膜3を形成する第1工程と、前記第1炭化シリコン膜上に、第2シリコン膜5を形成する第2工程と、前記第2シリコン膜上にレーザを照射する第3工程と、前記第3工程後の前記第1炭化シリコン膜上に炭素源ガスおよび珪素源ガスを供給することにより第2炭化シリコン膜を形成する第4工程と、を有する。かかる方法によれば、レーザ照射により、第1炭化シリコン膜3を改質でき、当該膜上に成長する第2炭化シリコン膜の特性が良好となる。

(もっと読む)

201 - 220 / 487

[ Back to top ]