Fターム[5F152LL03]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 気相 (1,473) | CVD、VPE (918)

Fターム[5F152LL03]の下位に属するFターム

プラズマCVD (98)

MOCVD、MOVPE (333)

Fターム[5F152LL03]に分類される特許

161 - 180 / 487

半導体基板の製造方法、および半導体基板

【課題】改善された光子/電子の変換効率を備える半導体基板を製造する方法を提供する。

【解決手段】本発明は、半導体基板の製造方法に関する。当該方法は、絶縁型基板上に第1の半導体層(7)を設けるステップと、拡散バリア層(9)を設けるステップと、第2の半導体層(11)を設けるステップとを備える。拡散バリア層を設けることにより、高ドープされた第1の半導体層から第2の半導体層への拡散を抑制することが可能になる。本発明はまた、これに相当する半導体基板、および当該基板を備えるオプトエレクトロニクスデバイスに関する。

(もっと読む)

ホウ素ドープ半導体ナノワイヤ及びその製造方法

【課題】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤ及びその製造方法を提供する。

【解決手段】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤは、次の工程を含む製造方法により製造できる。

工程(1):半導体原料ガスを用いて、基板上にIV族半導体ナノワイヤを成長させる;

工程(2):ジボランガスのみを導入することにより、前記半導体ナノワイヤの表面にホウ素膜を堆積させる;

工程(3):表面にホウ素膜を堆積させた前記ホウ素膜付き半導体ナノワイヤを、半導体ナノワイヤ(本体)の融点以下の温度で熱アニールする。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

グラフェン層が成長された基板およびそれを用いた電子・光集積回路装置

【課題】グラフェン層成膜の大面積化や基板材質の選択自由度の拡大、製造の低コスト化を実現するグラフェン層が成長された基板およびそれを用いた電子・光集積回路装置を提供する。

【解決手段】本発明に係るグラフェン層が成長された基板は、単層または複数層からなるグラフェン層が成長された基板であって、前記グラフェン層は前記基板の表面に対して略平行に成長しており、前記グラフェン層に対向する前記基板の最表面には金属酸化物の原子層が存在し、前記グラフェン層の前記基板に隣接する層と前記金属酸化物の原子層との層間距離が0.34 nm以下であることを特徴とする。また、前記金属酸化物の原子層の算術平均表面粗さRaが1 nm以下であることが好ましい。

(もっと読む)

エピタキシャルシリコンウェーハとその製造方法

【課題】シリコン結晶育成時にリンのような電気抵抗率降下用ドーパントとゲルマニウムが一緒に高濃度にドープされた低電気抵抗率のシリコン結晶基板をベースにしたエピタキシャルシリコンウェーハにおいて、ミスフィット転位とスタッキングフォルト(SF)の双方を抑制する。

【解決手段】シリコン結晶育成時に例えばリンとゲルマニウムが一緒に高濃度ドープされたシリコン結晶基板上に、シリコンエピタキシャル層をCVD法で成長させるプロセスにおいて、そのプロセス温度を1000〜1090℃の範囲内(より望ましくは、1050〜1080℃)の範囲内にする。これにより、SFに起因してエピタキシャルシリコンウェーハの表面に生じるLPD(SFに起因して生じる)の個数が大幅に減る。

(もっと読む)

基板上に微細構造を作製する方法

【課題】 本発明は微細構造の作製方法に関する。

【解決手段】 先駆体流体が存在する中で基板全体にわたって集束粒子ビームを走査することによって、パターニングされたシード層が形成される。ここで前記シード層を原子層堆積法又は化学気相成長法によって成長させることによって、高品質の層を成長させることができる。当該方法の利点は、非常に薄い層しか堆積しなくて良いため、前記シード層を形成するのに要する時間が相対的に短くなることである。

(もっと読む)

半導体製造方法と装置

【課題】部分的に絶縁膜が形成されているシリコン基板上を単結晶で覆うことができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】部分的に絶縁膜が形成されたSi基板10上に、a−Si膜14を成膜する(図1(b))。このSi基板10を熱処理すると、基板のSi結晶を種としてa−Siが固相Epi化される(図1(c))。基板の厚さ方向に対して充分にEpi結晶化された範囲を保護するようにレジスト膜18を形成し(図1(d))、エッチング処理を行い(図1(e))、その後、アッシング処理によってレジスト膜18を剥離し、このSi基板10上に再度a−Si膜を成膜する(図1(f))。再度、上記熱処理を行うことで、a−Siが固相Epi化される(図1(g))。

(もっと読む)

ダイアモンド層を有する窒化ガリウム層の製造

一態様における方法は、第1熱伝導率を有する第1ダイアモンド層と、第1熱伝導率よりも高い第2熱伝導率を有する第2ダイアモンド層とを有する窒化ガリウム(GaN)層を製造するステップを含む。この製造するステップは、第2ダイアモンド層を第1ダイアモンド層上に堆積させるために、マイクロ波プラズマ化学蒸着(CVD)プロセスを用いるステップを含む。 (もっと読む)

半導体装置の製造方法

【課題】横方向固相エピタキシャル成長法において単結晶膜成膜工程に要する時間を短縮し、半導体装置の製造を短時間で行う。

【解決手段】単結晶シリコン部403及び絶縁膜401が表面において露出したウエハ200を、構成元素としてSiを含むガスの雰囲気中に曝露し、単結晶シリコン部403及び絶縁膜401の上にアモルファスのシリコン膜402を成膜する成膜工程と、成膜工程後に、シリコン膜402を加熱して、単結晶シリコン部403を基にしてシリコン膜402を単結晶化させる加熱工程と、加熱工程後に、ウエハ200を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、単結晶化した部分を残留させつつ、単結晶化しなかった部分を除去する選択成長工程と、を含む半導体装置の製造方法であって、ウエハ200に対して、成膜工程、加熱工程及び選択成長工程を繰り返す。

(もっと読む)

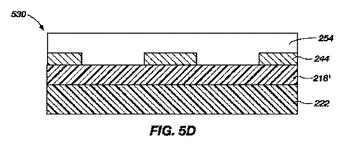

歪み処理複合半導体基板及びそれを形成する方法

【課題】 支持基板上に歪みIII族窒化物材料シード層を含む複合基板を作製する新規な方法を提供する。

【解決手段】 複合基板を作製する方法は、III族窒化物材料において所望の格子歪みを発生させて、複合基板上に形成すべきデバイス構造の格子定数に実質的に適合する格子定数を得るステップを含む。III族窒化物材料は、Ga極性又はN極性で形成され得る。所望の格子歪みは、III族窒化物材料と成長基板の間にバッファ層を形成するか、III族窒化物材料中にドーパントを注入するかあるいは不純物を導入して、その格子定数を変化させるか、又は熱膨張係数(CTE)を有するIII族窒化物材料を異なるCTEを有する成長基板上に形成することによって発生され得る。

(もっと読む)

半導体基板の製造方法、半導体基板

【課題】シリコン層又はシリコン基板上に、欠陥密度が低く高品質なエピタキシャル層を、少ない工程で低コストに形成することが可能な半導体基板の製造方法を提供する。

【解決手段】シリコンウエーハ11の一面11aに対して、ウエットエッチング法によって異方性エッチングを行う。シリコンウエーハ11の一面11aに対して、異方性エッチングを行うと、シリコンウエーハ11の一面11aに微細な凹凸12が形成される。この微細な凹凸12は、例えば(111)面からなる傾斜面12a,12bで構成された溝14が、周期的に多数形成されたものであればよい。

(もっと読む)

SOI基板とその製造方法、固体撮像装置とその製造方法、および撮像装置

【課題】SOI基板の単結晶シリコン層の表面側から侵入した金属不純物のような汚染物質をSOI基板の支持基板側にゲッタリングし易くすることを可能にする。

【解決手段】シリコン基板11と、前記シリコン基板11上に形成された酸化シリコン層12と、前記酸化シリコン層12上に形成されたシリコン層13と、前記シリコン基板11中に形成されたゲッター層14と、前記酸化シリコン層12に形成された不純物注入領域からなるダメージ層15を備えている。

(もっと読む)

低減した格子ひずみを備えた半導体材料、同様に包含する半導体構造体、デバイス、および、加工された基板を製造する方法

半導体装置を製作する方法または構造体は、従順な材料の層の上に横たわっている半導体材料の構造体を形成することを含み、その後半導体材料構造体を緩和させる従順な材料の粘性を変えて、緩和した半導体材料の連続層を形成する際の種子層として、緩和した半導体材料構造体を利用する。ある実施形態では、半導体材料の層は、III-Vタイプ半導体材料(例えばインジウム窒化ガリウム)から成る。新しい中間構造体が、この種の方法の間、形成される。加工された基板は、緩和した格子の構造体を有する半導体材料の連続層を含む。  (もっと読む)

(もっと読む)

ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置

【課題】格子定数が広範囲にわたり可変であり、且つ結晶性に優れた基板およびその製造方法を提供する。また上記基板上に形成された半導体素子を提供する。

【解決手段】6回対称軸をを有する結晶からなる第1の層11と、該結晶上に形成される金属酸窒化物結晶からなる第2の層12を有し、第2の層12が、In、Ga、Si、Ge及びAlからなる群から選択される少なくとも1つの元素と、NとOとZnとを主要元素として含み、且つ第2の層12が面内配向性を有する積層構造体を備えたウルツ鉱型結晶成長用基板。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体部材が単結晶の半導体材料からなり、特性が良好な半導体装置及びその製造方法を提供する。

【解決手段】単結晶のシリコンからなるシリコン基板11上に絶縁膜12を形成し、絶縁膜12に開口部12aを形成し、絶縁膜12上に開口部12aを介してシリコン基板11と接触するようにアモルファスシリコン膜を形成し、このアモルファスシリコン膜をシリコン基板11を起点として固相エピタキシャル成長させて、その後パターニングする。これにより、開口部12aの直上域から外れた領域の一部に、単結晶のシリコンからなるシード層を形成する。次に、このシード層を覆うようにアモルファスシリコン膜を堆積させ、このアモルファスシリコン膜をシード層を起点として固相エピタキシャル成長させて、単結晶シリコン膜を形成する。そして、この単結晶シリコン膜をパターニングすることにより、シリコンピラー33を形成する。

(もっと読む)

半導体デバイス用基板、半導体デバイス装置、設計システム、製造方法、および設計方法

【課題】結晶薄膜の膜質および膜厚を均一にする。

【解決手段】半導体デバイスを形成するためのデバイス用薄膜と、デバイス用薄膜を囲み、デバイス用薄膜の前駆体が結晶に成長することを阻害する阻害部と、前駆体が結晶に犠牲成長することによって形成された犠牲成長部であって、デバイス用薄膜の周辺に阻害部で隔てられて設けられた犠牲成長部と、犠牲成長部の上部を覆い、かつデバイス用薄膜の上部を露出する保護膜を備えた。保護膜はポリイミドであってもよい。

(もっと読む)

半導体装置の製造方法

【課題】半導体層に形成したリセスにモフォロジの良好な別の半導体層をエピタキシャル成長させる。

【解決手段】Si基板上にゲート絶縁膜、ゲート電極及びサイドウォールスペーサを形成した後(ステップS1,S2)、そのSi基板のソース・ドレイン領域を形成する部分に、ドライエッチングで第1リセスを形成する(ステップS3)。そして、ドライエッチングによってエッチングダメージが生じた第1リセスの表層部をウェットエッチングで除去することによって第2リセスを形成した後(ステップS4)、第2リセスにSiGe層をエピタキシャル成長させる(ステップS5,S6)。これにより、Si基板に形成したリセスに、モフォロジの良好なSiGe層を形成することが可能になる。

(もっと読む)

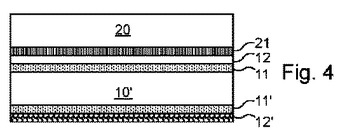

マイクロエレクトロニクス分野において単結晶膜を形成する方法

所定の材料の薄膜を形成する方法は次の工程を含む:表面上に上記所定の材料のアモルファスおよび/または多結晶膜12を有する第1の基板10が準備される;この第1の基板に疎水性直接結合(分子付着)によって、第2の基板20が結合され、上記第2の基板は、その表面上に所定の結晶配向の単結晶参照膜21を有する;少なくとも、アモルファスおよび/または多結晶膜に熱処理が適用され、上記熱処理は、このアモルファスおよび/または多結晶膜12の少なくとも一部に参照膜21の結晶配向に沿って固相再結晶を受けさせるように設計され、この参照膜は再結晶種として機能を果たす;少なくとも部分的に再結晶された膜は、参照膜の少なくとも一部から分離される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】高集積、高速且つ高性能な歪みSOI構造の縦型MISFETを得ること。

【解決手段】Si基板1上に酸化膜2を介して、横方向エピタキシャルSiGe層3が設けられ、SiGe層3は素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。SiGe層3上には選択的に縦方向エピタキシャルSiGe層7が設けられ、SiGe層7の側面には格子定数がやや小さい横方向エピタキシャル歪みSi層8が周設され、歪みSOI基板を形成しており、SiGe層7及び歪みSi層8の上部にはドレイン領域(10、11)が設けられ、SiGe層3全体、SiGe層7及び歪みSi層8の下部にはソース領域9が設けられ、歪みSi層8の側面にはゲート酸化膜12を介してゲート電極13が周設され、ドレイン領域11、ソース領域9及びゲート電極13には、それぞれ導電プラグ20を介してCu配線23が接続されている歪みSOI構造の縦型のMISFETを構成すること。

(もっと読む)

161 - 180 / 487

[ Back to top ]