Fターム[5F152LL04]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 気相 (1,473) | CVD、VPE (918) | プラズマCVD (98)

Fターム[5F152LL04]に分類される特許

1 - 20 / 98

シリコン単結晶膜およびその製造方法

【課題】薄層化された自立性のシリコン単結晶膜を提供し、また、剥離時の熱処理温度を格段に低減することができる新たなシリコン単結晶膜の形成方法を提供する。

【解決手段】シリコン単結晶膜6は、Siの含有率が、90原子%以上であり、厚みが、50μm以下であり、自立性がある。

(もっと読む)

グラフェン構造の製造方法及びこれを用いた半導体装置の製造方法

【課題】所望の位置にグラフェン膜を有するグラフェン構造及びこれを用いた半導体装置を提供する。

【解決手段】所定の基材3上において、炭素含有層4と、少なくともケイ素を含む炭素化合物層5とを順次に積層し、その上に絶縁膜層6を形成した後、絶縁膜層の一部をエッチングにより取り除いた基板に対してアニーリングを実施し、絶縁膜の除去部にのみグラフェン膜7を形成したグラフェン構造1を形成し、これを用いて表面にショットキー電極8、およびオーミック電極9,10を形成させて半導体装置2を作製する。

(もっと読む)

装置の作製方法

【課題】剥離前の形状及び特性を保った良好な状態で転置工程を行えるような、剥離工程

を用いて半導体装置及び表示装置を作製できる技術を提供する。よって、より高信頼性の

半導体装置及び表示装置を装置や工程を複雑化することなく、歩留まりよく作製できる技

術を提供することも目的とする。

【解決手段】透光性を有する第1の基板上に光触媒物質を有する有機化合物層を形成し、

光触媒物質を有する有機化合物層上に素子層を形成し、光を第1の基板を通過させて、光

触媒物質を有する有機化合物層に照射し、素子層を前記第1の基板より剥離する。

(もっと読む)

半導体基板の作製方法

【課題】SOI基板等の単結晶半導体層を有する半導体基板において、該単結晶半導体層を厚膜化することを課題の一とする。また、半導体基板の量産性を向上させることを課題の一とする。

【解決手段】単結晶半導体基板上に非晶質半導体層を形成した後、絶縁層を介して支持基板と貼り合わせ、該単結晶半導体基板の一部を、非晶質半導体層とともに支持基板上に転載する。そして、非晶質半導体層を固相エピタキシャル成長させることで、支持基板上に厚い単結晶半導体層を形成するものである。

(もっと読む)

微結晶シリコン膜の作製方法および薄膜トランジスタの作製方法

【課題】絶縁膜と微結晶シリコン膜との密着性を向上させた微結晶シリコン膜の作製方法を提供する。

【解決手段】絶縁膜55上に、後のプラズマ酸化等により完全に酸化される高さ(例えば0nmより大きく5nm以下)の微結晶シリコン粒、または後のプラズマ酸化等により完全に酸化される膜厚(例えば0nmより大きく5nm以下)の微結晶シリコン膜もしくはアモルファスシリコン膜を形成し、前記微結晶シリコン粒または前記微結晶シリコン膜もしくはアモルファスシリコン膜に酸素を含むプラズマ処理またはプラズマ酸化を施すことにより、前記絶縁膜上に酸化シリコン粒57aまたは酸化シリコン膜を形成し、前記酸化シリコン粒または前記酸化シリコン膜の上に微結晶シリコン膜59を形成する微結晶シリコン膜の作製方法である。

(もっと読む)

光起電力素子、TFT、及びi型半導体層の形成方法

【課題】 低コストで、優れた性能をもつシリコン系薄膜を提供するために、タクトタイムが短くて、高速の成膜速度で特性のすぐれたシリコン系薄膜と、それを含む半導体素子。さらにこのシリコン系薄膜を用いた密着性、耐環境性などに優れた半導体素子を提供することを目的とする。

【解決手段】 i型半導体層と前記i型半導体層の下地層である前記p型半導体層またはn型半導体層との界面領域であって前記i型半導体層と前記p型半導体層またはn型半導体層との界面から1.0nm以上20nm以下の界面領域の微結晶が(100)面に優先配向しており、前記i型半導体層の層厚方向における前記微結晶のエックス線または電子線による(220)面の回折強度の全回折強度に対する割合である(220)面の配向性が前記i型半導体層の下地層である前記p型半導体層又は前記n型半導体層側では小さく、前記下地層から離れるに伴って大きくなるように変化する。

(もっと読む)

半導体基板の作製方法及び光電変換装置の作製方法

【課題】低温での固相エピタキシャル成長法を用いて、結晶性の高いシリコン層を厚く形成した半導体基板を提供することを課題の一とする。その際、従来の気相エピタキシャル成長法と比べ、結晶成長速度を大きくすることを課題の一とする。

【解決手段】絶縁層を介してベース基板に設けられた単結晶シリコン層上に、堆積初期の一部で、単結晶シリコン層と結晶面の配列の揃った針状シリコン層が気相エピタキシャル成長するようにシリコン層を形成し、針状シリコン層を種結晶として、シリコン層の他部を固相エピタキシャル成長させて、単結晶及び前記結晶シリコン層の厚さが厚い半導体基板を作製する。

(もっと読む)

半導体複合体構造を形成する方法

【課題】 パターン付けされたシリコン・オン・インシュレータ(SOI)/シリコン・オン・ナッシング(SON)複合構造体を多孔性Si技術によって形成すること。

【解決手段】 パターン付けされたSOI/SON複合構造体及びその形成方法を提供する。SOI/SON複合構造体においては、パターン付けされたSOI/SON構造体が、Siオーバーレイヤと半導体基板の間に挟まれる。パターン付けされたSOI/SON複合構造体を形成する方法は、SOI及びSON構造が共に形成される共有加工処理ステップを含む。本発明はまた、埋没導電/SON構造体を含む複合構造体の形成方法、及び、埋没ボイド平面だけを有する複合構造体の形成方法を提供する。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

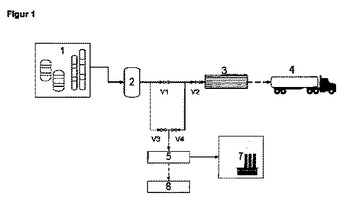

シラン及びゲルマンの純度を間接的に決定するための固有抵抗の使用及び相応する方法

本発明は、固有抵抗を測定するための機器を使用してシラン及びゲルマンの純度を間接的に決定するための方法に関する。本発明はさらに、固有抵抗を測定するための機器を使用した品質管理を含めた、シラン又はゲルマンの工業的製造及び/又は充填のためのプラントに関する。  (もっと読む)

(もっと読む)

SOI基板の作製方法

【課題】低温での固相エピタキシャル成長法を用いて、単結晶半導体層の膜厚の厚いSOI基板を提供することを課題の一とする。その際に、予めシード層となる単結晶半導体層の結晶欠陥を修復しなくとも、良好にエピタキシャル成長が進む方法を提供することを課題の一とする。また、シード層の結晶欠陥を修復する工程を別に設けなくとも、固相エピタキシャル成長によりシード層である単結晶半導体層の結晶性が回復したSOI基板を提供することを課題の一とする。

【解決手段】絶縁層を介して基板に設けられた第1単結晶半導体層上に、非晶質半導体層を形成する。非晶質半導体層は、成膜温度100℃以上275℃以下、シラン系ガスを希釈しないで用いるCVD法により形成する。熱処理を行って、非晶質半導体層を固相エピタキシャル成長させて、単結晶半導体層の膜厚の厚いSOI基板を作製する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】しきい値電圧の経時変化およびホットキャリア劣化が可及的に小さく、かつオン特性の低下が可及的に小さい薄膜トランジスタおよびその製造方法を提供する。

【解決手段】ゲート電極32上に、ゲート絶縁膜36として、第1ゲート絶縁膜50と、第2ゲート絶縁膜51とを形成する。第1ゲート絶縁膜50を窒化シリコン膜で形成し、第2ゲート絶縁膜51を酸化シリコン膜で形成し、第2ゲート絶縁膜51の表面部にAr含有層52を形成する。Ar含有層52に接するように、微結晶シリコン膜62を形成し、さらにi型非晶質シリコン膜63およびN型非晶質シリコン膜61を形成して、活性層37を形成する。これによって、高密度に均一に結晶を成長させることができるので、均一でボイドの少ない微結晶シリコン膜62を形成することができる。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】結晶粒間に鬆がない緻密な結晶性半導体膜(例えば微結晶半導体膜)を作製する技術を提供することを目的とする。

【解決手段】プラズマCVD装置の反応室内における反応ガスの圧力を450Pa〜13332Paとし、当該プラズマCVD装置の第1の電極と第2の電極の間隔を1mm〜20mm、好ましくは4mm以上16mm以下として、前記第1の電極に60MHz以下の高周波電力を供給することにより、第1の電極および第2の電極の間にプラズマ領域を形成し、プラズマ領域を含む気相中において、結晶性を有する半導体でなる堆積前駆体を形成し、堆積前駆体を堆積させることにより、5nm以上15nm以下の結晶核を形成し、結晶核から結晶成長させることにより微結晶半導体膜を形成する。

(もっと読む)

立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置

【課題】低コストの立方晶炭化ケイ素(3C−SiC)単結晶薄膜を得るための立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置を提供する。

【解決手段】立方晶炭化ケイ素単結晶薄膜の製造方法において、基板101の表面に犠牲層102を形成する第1の工程と、犠牲層の表面に少なくとも表面層が立方晶構造である立方晶半導体層103を形成する第2の工程と、立方晶半導体層の表面に立方晶炭化ケイ素単結晶層104を形成する第3の工程と、犠牲層をエッチング除去して、立方晶半導体層と立方晶炭化ケイ素単結晶層との積層体を剥離する第4の工程とを備える。

(もっと読む)

半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子

【課題】Si結晶層上に半導体素子を備えたSi以外の半導体単結晶層を備えた半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子を提供する。

【解決手段】Si(111)基板(第1の基板)101の表面にバッファ層102と半導体単結晶層103とを順次形成する第1の工程と、半導体単結晶層101aとバッファ層102aとSi(111)基板の所定の厚さ部分102bとを含む分離島150を形成する第2の工程と、分離島の表面を覆う被覆層200を形成する第3の工程と、被覆層をマスクに前記Si(111)基板をSi(111)面に沿ってエッチングして剥離する第4の工程と、分離島の剥離面を別の基板(第2の基板)201の表面に接合する第5の工程とを備える。

(もっと読む)

半導体装置の作製方法

【課題】外部から局所的に圧力がかかっても破損しにくい半導体装置を提供する。また、

外部からの局所的押圧による非破壊の信頼性が高い半導体装置を歩留まり高く作製する方

法を提供する。

【解決手段】非単結晶半導体層を用いて形成された半導体素子を有する素子層上に、有機

化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体を設け、加熱圧着す

ることにより、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体

及び素子層が固着された半導体装置を作製する。

(もっと読む)

半導体製造方法

【課題】ガラス上に高効率な薄膜多結晶シリコン(Si)太陽電池を実現することを目的とした半導体製造方法。

【解決手段】半導体励起(ダイオード励起)された固体連続波レーザーを利用して(110)と(111)に配向制御した大粒径多結晶シリコン(Si)薄膜をガラス上に形成し、このSi膜を種(シード)結晶として多結晶Si層を直接成長する。

その後、本薄膜に対してSi層が溶融しない条件でエネルギービームを照射してSiの固相成長を行うことを特徴とした太陽電池用半導体製造方法。

(もっと読む)

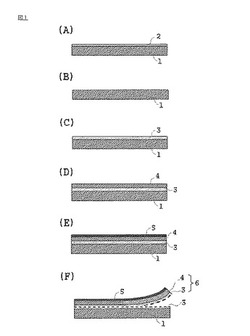

ダイヤモンド半導体及び作製方法

【課題】従来技術と比較して、室温で十分に高いキャリア濃度を有するダイヤモンド半導体及び作製方法を提供すること。

【解決手段】ダイヤモンド基板11(図5(a))上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとし、基板温度700℃でダイヤモンド薄膜12を1ミクロン積層する(図5(b))。ダイヤモンド薄膜12にイオン注入装置を用い、不純物1(VI族又はII族元素)を打ち込む(図5(c))。その後、不純物2(III族又はV族元素)を打ち込んだが(図5(d))、注入条件は、打ち込んだ不純物がそれぞれ表面から0.5ミクロンの厚さの範囲内で、1×1017cm-3となるようにシミュレーションにより決定した。その後、2種類のイオンが注入されたダイヤモンド薄膜13をアニールすることにより(図5(e))、イオン注入された不純物の活性化を行い、ダイヤモンド半導体薄膜15を得た(図5(f))。

(もっと読む)

薄膜トランジスタの作製方法

【課題】絶縁層上に結晶性の高い微結晶半導体層を形成することを課題とする。また、電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供することを課題とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極上に、窒素を含む絶縁層を形成する。次に、窒素を含む絶縁層上に、シリコンを含む堆積性気体と、窒素を含む酸化気体と、水素とを用い、プラズマを発生させて、酸化珪素層を形成する。次に、酸化珪素層上に、シリコンまたはゲルマニウムを含む堆積性気体と、水素とを用い、プラズマを発生させて、微結晶半導体層を形成する。

(もっと読む)

1 - 20 / 98

[ Back to top ]