Fターム[5F152LL03]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 気相 (1,473) | CVD、VPE (918)

Fターム[5F152LL03]の下位に属するFターム

プラズマCVD (98)

MOCVD、MOVPE (333)

Fターム[5F152LL03]に分類される特許

121 - 140 / 487

炭化シリコン膜の製造方法

【課題】良好な膜質であり所望の導電型や導電性に制御された炭化シリコン膜を低コストで効率よく製造する方法を提供する。

【解決手段】本発明の炭化シリコン膜の製造方法は、不純物領域を有する炭化シリコン膜の製造方法である。表層にシリコン膜16aを有する基板11のシリコン膜16aを炭化処理して、炭化された膜を含んだ炭化シリコン膜13を形成する工程を有する。不純物領域になる部分のシリコン膜を炭化処理する前に、この部分に不純物を注入する。

(もっと読む)

炭化シリコン膜の製造方法

【課題】エッチングが困難な炭化シリコン膜をエッチングすることなく、一つのチップに炭化シリコンのデバイスとシリコンのデバイスを容易に混載させ、かつ、炭化シリコンのデバイスとシリコンのデバイスが電気的に絶縁された構造とすることが可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上に下地層12を形成する工程と、下地層12上にシリコン膜を形成する工程と、シリコン膜をパターニングするパターニング工程と、パターニング工程の後にシリコン膜を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、炭化シリコン膜13をマスクに用いて、マスクが形成されていない領域の下地層12をエッチングする工程と、を有することを特徴とする。

(もっと読む)

III族窒化物半導体成長用基板、III族窒化物半導体エピタキシャル基板、III族窒化物半導体素子およびIII族窒化物半導体自立基板、ならびに、これらの製造方法

【課題】成長温度が1050℃以下のAlGaNやGaNやGaInNだけでなく、成長温度が高い高Al組成のAlxGa1-xNにおいても結晶性の良いIII族窒化物半導体エピタキシャル基板、III族窒化物半導体素子、III族窒化物半導体自立基板およびこれらを製造するためのIII族窒化物半導体成長用基板、ならびに、これらを効率よく製造する方法を提供する。

【解決手段】少なくとも表面部分がAlを含むIII族窒化物半導体からなる結晶成長基板と、前記表面部分上に形成されたスカンジウム窒化物膜とを具えることを特徴とする。

(もっと読む)

炭化シリコン膜の製造方法

【課題】高温で長時間の処理が必要なエピタキシャル成長を用いることなく、熱応力の発生を抑え、信頼性に優れた、所望の膜厚の炭化シリコン膜を容易に得ることができ、かつ低コストや大口径化が可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含む第1シリコン膜14aを形成する工程と、第1シリコン膜14aを炭化処理し第1炭化シリコン膜13aを形成する工程と、第1炭化シリコン膜13aを形成した後に、第2シリコン膜14bを形成する工程と、第2炭化シリコン膜13bを形成する工程と、を少なくとも1回有することを特徴とする。

(もっと読む)

積層構造物

【課題】過度に複雑な、成長後の加工処理(post growth processing)が最小限に抑えられ、第2のいっそう厚い層と比べて非常に異なる特性を有する薄いダイヤモンド層を有する構造体を合成することが可能となる方法を提供する。

【解決手段】互いに接触している少なくとも2つの層(20,22)であって、各々の層は広いバンドギャップの材料でできており、各々の層は少なくとも1つの性質が他の層と相違している前記少なくとも2つの層(20,22)を有する生成物を製造する方法。

(もっと読む)

おもて面と裏面とを有するシリコン単結晶基板及び前記おもて面上に堆積されたSiGeの層を含んでなるウェーハを製造する方法

【課題】おもて面と裏面とを有するシリコン単結晶基板及び前記おもて面上に堆積されたSiGeの層を含んでなるウェーハを製造する方法。

【解決手段】本方法は、次の順序で工程:前記シリコン単結晶基板のおもて面及び裏面を同時に研磨する工程;応力補償層を前記シリコン単結晶基板の裏面上に堆積させる工程;前記シリコン単結晶基板のおもて面を研磨する工程;前記裏面上に堆積された応力補償層を有する前記シリコン単結晶基板を洗浄する工程;及びSiGeの完全に又は部分的に緩和された層を前記シリコン単結晶基板の前記おもて面上に堆積させる工程を含んでなる。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】単一半導体基板上にHBTおよびFETのような複数異なる種類のデバイスを形成するに適した半導体基板を製造する方法を提供する。

【解決手段】半導体を結晶成長させる反応容器内に第1不純物原子を構成要素として有する単体または化合物を含む第1不純物ガスを導入する段階を含む複数の段階を繰り返して、複数の半導体基板を製造する方法であって、第1不純物ガスを導入する段階の後に、製造された半導体基板を取り出す段階と、反応容器内に第1半導体を設置する段階と、反応容器内に、第1半導体内で第1不純物原子と反対の伝導型を示す第2不純物原子を構成要素として有する単体または化合物を含む第2不純物ガスを導入する段階と、第1半導体を第2不純物ガスの雰囲気中で加熱する段階と、加熱した前記第1半導体上に第2半導体を結晶成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

基板から分離された窒化ガリウムの膜をエピタキシーにより製造する方法

【課題】本発明は、欠陥密度レベルの減少した、エピタキシーによる窒化ガリウム膜の製造に関する。それは、GaNのエピタキシャル付着により窒化ガリウム(GaN)膜を製造するための方法に関する。

【解決手段】本発明は、それが少なくとも1ステップのエピタキシャル横方向成長を含んでなり、それがGaN基板への直接的イオン注入による脆化でその基板からGaN層の一部を分離させるステップを含んでなることで特徴付けられる。本発明は、上記方法で得られる膜、並びに該窒化ガリウム膜を備えた光電子および電子部品にも関する。

(もっと読む)

III族窒化物半導体成長用基板、III族窒化物半導体エピタキシャル基板、III族窒化物半導体素子およびIII族窒化物半導体自立基板、ならびに、これらの製造方法

【課題】成長温度が1050℃以下のAlGaNやGaNやGaInNだけでなく、成長温度が高い高Al組成のAlxGa1-xNにおいても結晶性の良いIII族窒化物半導体エピタキシャル基板、III族窒化物半導体素子、III族窒化物半導体自立基板およびこれらを製造するためのIII族窒化物半導体成長用基板、ならびに、これらを効率よく製造する方法を提供する。

【解決手段】少なくとも表面部分がAlを含むIII族窒化物半導体からなる結晶成長基板と、前記表面部分上に形成されたスカンジウム窒化物膜とを具えることを特徴とする。

(もっと読む)

半導体基板、半導体装置及び半導体基板の製造方法

【課題】所望の電気的特性を得やすい半導体基板、半導体装置及び半導体基板の製造方法を提供すること。

【解決手段】半導体基板の製造方法は、第1エピタキシャル層を形成する第1エピタキシャル層形成工程S1と、第1エピタキシャル層にトレンチを形成するトレンチ形成工程S2と、第1エピタキシャル層及びトレンチ内にエピタキシャル層を、異なる成長速度を含む複数の成長条件を用いて、トレンチ内を埋めるように形成し、複数の成長条件のそれぞれにおいてエピタキシャル層に取り込まれるドーパント濃度を一定にするエピタキシャル層形成工程S3、S4、S5と備える。

(もっと読む)

半導体装置およびその製造方法

【課題】組立ラインのクリーン度を向上させても、半導体装置の製造歩留まりを、ある一定値以上に向上させることが困難であった

【解決手段】エピタキシャル成長法により半導体基板1にエピタキシャル層2を設ける成膜工程と、前記エピタキシャル層2に半導体素子3を設ける工程と、前記半導体基板1を除去して、前記エピタキシャル層のみを残す除去工程とを備える。

(もっと読む)

半導体基板、半導体基板の製造方法、電子デバイス、および電子デバイスの製造方法

【課題】結晶薄膜を有する半導体基板の設計および上記結晶薄膜の膜質および膜厚の制御を容易にできる半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に、一体にまたは分離して設けられ、化合物半導体の結晶成長を阻害する阻害層とを備え、阻害層は、ベース基板まで阻害層を貫通する複数の開口を有する複数の第1開口領域を有し、複数の第1開口領域のそれぞれは、内部に同一の配置で設けられた複数の第1開口を含み、複数の第1開口の一部は、電子素子が形成されるべき第1化合物半導体が設けられている第1素子形成開口であり、複数の第1開口の他の一部は、電子素子が形成されない第1ダミー開口である半導体基板を提供する。

(もっと読む)

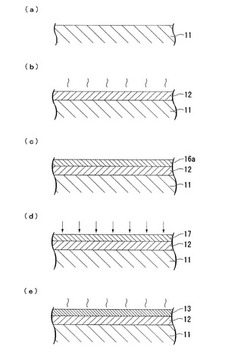

半導体基板の製造方法及び半導体基板

【課題】良好な立方晶の炭化珪素膜を形成可能な半導体基板の製造方法及び半導体基板を提供すること。

【解決手段】シリコン基板11の上面に多孔質な多孔質シリコン層12を形成する工程と、水素ガス及び炭化水素系ガスの混合ガスまたは炭化水素系ガスを供給し、多孔質シリコン層12の表面を結晶化及び炭化して炭化珪素膜13を形成する工程と、を備える。

(もっと読む)

半導体基板の製造方法

【課題】良好な立方晶の炭化珪素膜を形成可能な半導体基板の製造方法を提供すること。

【解決手段】シリコン基板11上にバッファ層12を形成する第1の工程と、バッファ層12上にシリコン膜15を形成する第2の工程と、シリコン膜15を炭化して炭化珪素膜13を形成する第3の工程と、を含み、バッファ層12は、シリコンの格子定数と炭化珪素膜13の格子定数との間の格子定数を有する金属酸化物で構成され、第3の工程は、炭化水素系ガスの雰囲気下で行われる。

(もっと読む)

3次元集積回路装置及びその製造方法

【課題】ガラス基板上に薄膜半導体層を形成した3次元集積回路装置を提供する。

【解決手段】ガラス基板11上に、単結晶もしくは準単結晶の2層の薄膜半導体層13,16が層間絶縁層14を介して積層され、2層の薄膜半導体層13,16は、下層の第1層の薄膜半導体層13と上層の第2層の薄膜半導体層16とが異なる材料であり、2層の薄膜半導体層13,16が、層間絶縁層14に形成された開口内を埋めて形成された、エピタキシャル層15によって接続され、エピタキシャル層15の表面部は、第2層の薄膜半導体層16と同じ材料の層であり、第1層の薄膜半導体層13及び第2層の薄膜半導体層16のうち、1層以上に能動素子Tr21,Tr22が形成されている3次元集積回路装置10を構成する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

窒化物系化合物半導体層を支持基板上に有する基板生産物を製造する方法、及び半導体デバイスの製造方法

【課題】窒化物系化合物半導体層を支持基板上に有する基板生産物を製造するために、異種基板同士を貼り合わせる工程を含む方法において、所望の半導体デバイスに適した基板を選択可能な方法を提供する。

【解決手段】窒化物系化合物半導体から成る第1の基板10の表層と、窒化物系化合物半導体とは異なる材料から成る第2の基板20の表面20aとを互いに接合させる。第1の基板10のうち表層を含む部分を層状に残して他の部分を除去することにより、窒化物系化合物半導体層30を第2の基板20上に形成する。窒化物系化合物半導体層30の表面30aと、窒化物系化合物半導体層30及び第2の基板20の双方と異なる材料から成る支持基板40の表面40aとを互いに接合させたのち、第2の基板20を窒化物系化合物半導体層30から剥離させる。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に化合物半導体の結晶成長を阻害する阻害層が設けられ、阻害層はSi結晶層にまで貫通する開口を有し、開口の内部にシード結晶を備え、化合物半導体はシード結晶に格子整合または擬格子整合している半導体基板を提供する。サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられ化合物半導体の結晶成長を阻害する阻害層であって、Si結晶層にまで貫通する開口を有する阻害層と、開口の内部に設けられたシード結晶と、シード結晶に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

窒化物単結晶の製造方法、テンプレート基板、および窒化物単結晶基板

【課題】窒化物単結晶膜におけるクラックの発生を抑制する窒化物単結晶膜の製造方法、クラックの発生が抑制された窒化物単結晶基板、およびクラックの発生が抑制された窒化物単結晶膜を備えるテンプレート基板を提供する。

【解決手段】窒化物単結晶膜の製造方法は、(11−20)面からのオフ角が5°以下である下地基板1を準備する工程と、上記下地基板1の主表面上に窒化物単結晶膜3を形成する工程とを備える。前記下地基板1はSiCまたはサファイアからなることが好ましく、また、前記窒化物単結晶膜3を形成する工程における成膜温度範囲は1700℃以上2400℃以下であることが好ましい。これにより、前記テンプレート基板4の窒化物単結晶膜3はクラックの密度が低く、また、前記テンプレート基板4から下地基板1を取り除いた窒化物単結晶基板についても同様に、クラックの密度が低くなる。

(もっと読む)

121 - 140 / 487

[ Back to top ]