Fターム[5F152LL03]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 気相 (1,473) | CVD、VPE (918)

Fターム[5F152LL03]の下位に属するFターム

プラズマCVD (98)

MOCVD、MOVPE (333)

Fターム[5F152LL03]に分類される特許

141 - 160 / 487

半導体装置の製造方法及び半導体装置

【課題】 電界効果型トランジスタの動作速度を向上させる半導体装置の製造方法、及び半導体装置を提供する。

【解決手段】 ゲルマニウム基板の上にシリコンゲルマニウムを含むエピタキシャル成長層を形成する工程と、エピタキシャル成長層上に酸化物層を形成する工程と、エピタキシャル成長層を熱処理する熱処理工程と、を含み、熱処理工程における熱処理は、加熱温度が600℃以上900℃以下であり、ゲルマニウム基板の上にシリコンゲルマニウムからなるエピタキシャル成長層を形成する工程は、エピタキシャル成長層にシリコンが5%以上20%以下、及びゲルマニウムが80%以上95%以下の割合で含有するように形成する。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法およびシリコンエピタキシャルウェーハ

【課題】N型の超低抵抗率(2mΩ・cm以下)のシリコン単結晶基板を用いた、ミスフィット転位の発生を抑制することができるシリコンエピタキシャルウェーハの製造方法とシリコンエピタキシャルウェーハを提供する。

【解決手段】少なくとも、チョクラルスキー法によって育成したシリコン単結晶棒を加工してシリコン単結晶基板を作製し、該シリコン単結晶基板の主表面上にシリコン薄膜を気相成長させるシリコンエピタキシャルウェーハの製造方法であって、前記チョクラルスキー法で前記シリコン単結晶棒を育成する際に、該シリコン単結晶棒に抵抗率が2mΩ・cm以下となるように燐をドープし、かつ前記シリコン薄膜の気相成長前に、前記シリコン単結晶基板に対して前記燐の拡散長が0.24μm以上となるように時間と温度を調整した熱処理を行うことを特徴とするシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

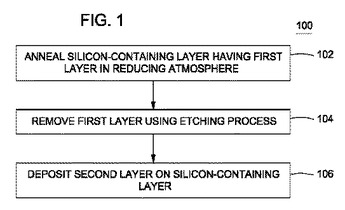

界面汚染を低減した層を堆積させる方法

本明細書では、界面汚染を低減した層の堆積方法を開示する。発明の方法は、有利には、堆積させた層間の汚染、例えば堆積させた層とその下にある基板または膜との間の界面の汚染を減少させる。幾つかの実施形態では、層の堆積方法は、第1の層が上に配置されたシリコン含有層を還元性雰囲気中でアニールすることと、アニールの後で、シリコン含有層を露出させるエッチングプロセスを使用して第1の層を除去することと、露出したシリコン含有層の上に第2の層を堆積させることとを含むことができる。  (もっと読む)

(もっと読む)

非極性または半極性(Ga、Al、In、B)N基板上に成長させられる素子

非極性または半極性の(Ga、Al、In、B)N基板上の(Ga、Al、In、B)N薄膜の成長形態を改良する方法であって、(Ga、Al、In、B)N薄膜は、非極性または半極性の(Ga、Al、In、B)N基板あるいはテンプレート上に直接成長させられ、成長の際に使用されるキャリアガスの一部は、不活性ガスから構成される。非極性または半極性の窒化物LEDおよびダイオードレーザは、本発明によって成長させられる平滑(Ga、Al、In、B)N薄膜上に成長させられてもよい。  (もっと読む)

(もっと読む)

歪シリコンSOI基板の製造方法

【課題】少なくとも埋め込み酸化膜から歪シリコン層までの距離が十分に短く、かつ中間層であるSiGe層が完全に歪緩和した半導体基板の製造方法を提供する。

【解決手段】SOI基板上に設定した濃度のGeを含むSiGeエピタキシャル層とシリコン薄膜とを順次エピタキシャル成長を形成した後で、SOI基板の埋め込み酸化膜とSi層との界面に水素原子を注入し、続いて、450〜550℃で15分以上の低温熱処理を施し、その後、酸化雰囲気下でSiGe層中のGe濃度で決定されるSi−Ge2元系状態図における固相線以下の温度と時間で酸化熱処理を1回以上行ない、酸化熱処理の後でSiGe層中のGe濃度を計算し、次に酸化膜を除去した後にシリコン薄膜を形成する事を特徴とする歪シリコンSOI基板の製造方法である。

(もっと読む)

半導体装置基板の製造方法および半導体装置基板

【課題】特定方向の基板反りを抑制できる半導体装置基板の製造方法を実現する。

【解決手段】ガラス基板11の裏面に、ストライプ形状にパターニングされた応力制御層51を形成する。応力制御層51の形成後に、ガラス基板11のおもて面にCLC技術を用いて多結晶シリコン膜を形成する。応力制御層51のストライプの長手方向は、CLC技術において使用される連続波レーザの走査方向と垂直な方向に一致させる。

(もっと読む)

半導体基板の製造方法、半導体デバイスの製造方法、半導体基板および半導体デバイス

【課題】低抵抗な窒化物層を基板へ貼り合わせた半導体基板の製造方法、半導体デバイスの製造方法、半導体基板および半導体デバイスを提供する。

【解決手段】半導体基板10の製造方法は、以下の工程を備えている。主面と、主面と反対側の裏面とを有する窒化物基板を準備する。窒化物基板の裏面に、気相のイオンを注入する。窒化物基板の裏面と、異種基板11とを貼り合わせることにより、貼り合わせ基板を形成する。貼り合せ基板から窒化物基板の一部を剥離する。700℃を超える温度で熱処理する。

(もっと読む)

ダイヤモンド半導体及び作製方法

【課題】従来技術と比較して、室温で十分に高いキャリア濃度を有するダイヤモンド半導体及び作製方法を提供すること。

【解決手段】ダイヤモンド基板11(図5(a))上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとし、基板温度700℃でダイヤモンド薄膜12を1ミクロン積層する(図5(b))。ダイヤモンド薄膜12にイオン注入装置を用い、不純物1(VI族又はII族元素)を打ち込む(図5(c))。その後、不純物2(III族又はV族元素)を打ち込んだが(図5(d))、注入条件は、打ち込んだ不純物がそれぞれ表面から0.5ミクロンの厚さの範囲内で、1×1017cm-3となるようにシミュレーションにより決定した。その後、2種類のイオンが注入されたダイヤモンド薄膜13をアニールすることにより(図5(e))、イオン注入された不純物の活性化を行い、ダイヤモンド半導体薄膜15を得た(図5(f))。

(もっと読む)

半導体材料の薄層の形成

GaAs、またはSiGeのようなゲルマニウム材料のいずれかの層を形成する方法を開示する。例えばゲルマニウム材料は、GaAs面上にエピタキシャル成長することができる。ゲルマニウム材料を一部の残留GaAsと共にレシーバ基板に転写するために、層転写が使用される。次いで残留GaAsは、GaAsとゲルマニウム材料との間の境界がエッチストップとなり、選択的エッチングによって除去することができる。 (もっと読む)

炭化珪素単結晶基板および炭化珪素単結晶エピタキシャルウェハ

【課題】デバイス特性の劣化や、歩留まりの低下を抑制するため、貫通転位の転位線の方向を規定する方法を提供する。

【解決手段】貫通転位3の転位線の方向が揃えられ、貫通転位3の転位線の方向と[0001]c軸との為す角度θが22.5°以下となるようにする。[0001]c軸方向に転位線を持つ貫通転位3は、基底面転位の転位線の方向と垂直であるため、C面内の拡張転位とはならず、積層欠陥を発生させることがない。このため、貫通転位3の転位線の方向が[0001]c軸であるSiC単結晶基板1に対して電子デバイスを形成すれば、デバイス特性は良好となり、劣化が無く、歩留まりも向上したSiC半導体装置。

(もっと読む)

複合基板、エピタキシャル基板、半導体デバイス及び複合基板の製造方法

【課題】支持基板上に高品質の窒化物半導体層が形成された複合基板、エピタキシャル基板、半導体デバイス及び複合基板の製造方法を提供する。

【解決手段】複合基板は、支持基板と、窒化物半導体層と、支持基板と窒化物半導体層との間に設けられた接合層とを備える。窒化物半導体層の転位密度は、1×108個/cm2以下である。窒化物半導体層は、接合層側の第1面と、第1面とは反対側の第2面とを有している。第1面における転位密度と第2面における転位密度との差が1×102個/cm2以下である。

(もっと読む)

非極性III族窒化物層を有する多層構造及びその製造方法

【課題】非極性III族窒化物層を有する多層構造及びその製造方法を提供する。

【解決手段】基板上に複数の核形成層を形成する工程と、該核形成層上に非極性III族窒化物層を形成する工程とを備え、複数の核形成層がそれぞれ独立して下記式(I)で表される窒化物から選択される。

上記式において、AとBは異なっており、B、Al、Ga、IN又はTlから選択され、且つ0≦x≦1である。該複数の核形成層によって、応力の緩和、格子不整合(mismatch)の減少、転位延長の阻止、転位密度の低減に有利になるため、表面が平坦で且つ結晶品質の良いIII族窒化物層を形成することができる。

(もっと読む)

シリコンエピタキシャルウェーハ及びシリコンエピタキシャルウェーハの製造方法並びにエピタキシャル成長用シリコン単結晶基板

【課題】抵抗率が20[mΩ・cm]以下のようなミスフィット転位が発生しやすいシリコン単結晶基板にシリコンエピタキシャル層を成長させるに際して、ミスフィット転位の発生を効果的に抑制することができるシリコンエピタキシャルウェーハ及びその製造方法並びにエピタキシャル成長用シリコン単結晶基板を提供する。

【解決手段】シリコン単結晶基板上にシリコンエピタキシャル層が形成されたシリコンエピタキシャルウェーハであって、前記シリコン単結晶基板はドープ剤として少なくともボロンとガリウムの両方が添加されたものであり、かつ抵抗率が20[mΩ・cm]以下であることを特徴とするシリコンエピタキシャルウェーハ。

(もっと読む)

半導体材料を形成するためのエピタキシャル方法および構造

改良された特性を備えた半導体材料、基板、およびデバイスの製造方法および構造が開示される。歪みが低減された構造を形成するための構造および方法が、複数の実質的に歪み緩和されたアイランド構造を形成し、半導体材料の歪み緩和された実質的に連続した層を引き続きさらに成長するために、このようなアイランド構造を利用することを含む。 (もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

シリコン膜の形成方法、pn接合の形成方法、及びこれを用いて形成されたpn接合

【課題】マイクロヒーターを利用して、多結晶シリコンからなるシリコン膜を形成する方法、pn接合を形成する方法、及びこれを用いて形成されたpn接合を提供する。

【解決手段】シリコン膜は、基板10及び基板と離間した金属パターン30を含むマイクロヒーターを利用して形成されうる。マイクロヒーターの金属パターンに電圧を印加して金属パターンを加熱し、シリコンを含むソース気体にマイクロヒーターを露出させて金属パターン上にシリコン膜100を形成することができる。シリコン膜は、多結晶シリコンからなりうる。pn接合は、基板10、基板上の導電層20、及び基板と離間した金属パターン30を含むマイクロヒーターを利用して形成されうる。マイクロヒーターの金属パターンに電圧を印加して金属パターンを加熱することで、金属パターンと導電層との間にpn接合を形成することができる。pn接合は、多結晶シリコンを含みうる。

(もっと読む)

III族窒化物基板、それを備える半導体デバイス、及び、表面処理されたIII族窒化物基板を製造する方法

【課題】 安定した表面を有するIII族窒化物基板を提供する。

【解決手段】 一実施形態に係るIII族窒化物基板は、表面層を有している。当該表面層は、3at.%の〜25at.%の炭素を含み、且つ、5×1010原子/cm2〜200×1010原子/cm2のp型金属元素を含んでいる。このIII族窒化物基板は、安定した表面を有するものとなる。

(もっと読む)

エピタキシャル成長用内部改質基板及びそれを用いて作製される結晶成膜体、デバイス、バルク基板及びそれらの製造方法

【課題】窒化物半導体層のエピタキシャル成長に用いるサファイア基板において、効率良く基板の反り形状及び/又は反り量を精密に制御することができ、且つ、成膜中に生じる基板の反りを抑制、それを用いて作製される窒化物半導体層成膜体、窒化物半導体デバイス、窒化物半導体バルク基板及びそれらの製造方法を提供する。

【解決手段】サファイア基板の内部に、前記サファイア基板の研磨面側を通してパルスレーザを集光し、走査し、前記パルスレーザによる多光子吸収を利用して改質領域パターンを形成し、サファイア基板の反り形状及び/又は反り量を制御する。本発明により得られたサファイア基板を用いて窒化物半導体層を形成すると、成膜中の基板の反りを抑制し、基板の反り挙動を小さくすることができるため、膜の品質及び均一性が向上し、窒化物半導体デバイスの品質及び歩留まりを向上させることができる。

(もっと読む)

基板上に単結晶半導体層を作製する方法

【課題】基板上に高品質の単結晶半導体層を形成する。

【解決手段】基板上に単結晶の半導体材料の層を形成する方法に関し、この方法は、基板1を準備する工程と、基板上に少なくとも1つの半導体材料の単分子層2を含むテンプレートをエピタキシャル成長する工程と、テンプレート上に半導体材料のアモルファス層3を堆積する工程と、熱処理またはレーザアニールを行い、半導体材料のアモルファス層を、半導体材料の単結晶層に完全に変える工程とを含む。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】基板と当該基板に形成される化合物半導体とを電気的に絶縁しつつ、結晶性に優れた化合物半導体を備えた半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に設けられたシード結晶と、シード結晶の上方に設けられた化合物半導体と、シード結晶と化合物半導体との間に設けられ、シード結晶よりも大きな抵抗率を有する高抵抗層とを備え、シード結晶と化合物半導体とが格子整合または擬格子整合している半導体基板を提供する。

(もっと読む)

141 - 160 / 487

[ Back to top ]