Fターム[5F152LN12]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | バッファ層、動作層 (308) | 超格子 (44)

Fターム[5F152LN12]に分類される特許

21 - 40 / 44

窒化物半導体厚膜基板

【課題】複数の窒化物半導体層を含む発光素子構造を成長させるために望ましい窒化物半導体厚膜基板を提供し、ひいてはその基板を用いて優れた特性を有する窒化物半導体発光装置を提供する。

【解決手段】複数の窒化物半導体層を含む発光素子構造を成長させるための窒化物半導体厚膜基板であって、基板は対向する第1と第2の主面を有し、基板の第1主面は3×1018cm-3以上1×1019cm-3以下の高不純物濃度の第1の層領域で形成されており、基板は3×1018cm-3以下1×1017cm-3以上でかつ第1層領域より低い低不純物濃度の第2の層領域をも少なくとも含み、基板の第1主面はその上に前記発光素子構造を成長させるための面であり、発光素子構造の形成後に第1主面の側で部分的に露出される基板の領域が電極を形成するための領域として使用されることを特徴とする。

(もっと読む)

化合物半導体基板

【課題】ラマン分光法を用いた簡易な応力測定方法を見出し、これに基づいて、GaN活性層を有する化合物半導体基板において、バッファ層における応力を制御し、全体として応力フリーの化合物半導体基板を提供する。

【解決手段】厚さ100〜1000μmの六方晶SiC、単結晶Si、単結晶Si上に立方晶SiC層が形成されたもののうちのいずれかからなる台基板1上に、バッファ層2、厚さ0.5〜5μmのGaN活性層3を順次積層し、前記バッファ層2を、厚さ3〜250nmのAlxGa1-xN単結晶層(0.5<x≦1)2a‐1の上に、厚さ3〜250nmのAlyGa1-yN単結晶層(0.2≦y≦0.3)2b‐1が形成され、さらに、厚さ3〜250nmのAlxGa1-xN単結晶層2a‐nおよび厚さ3〜250nmのAlzGa1-zN単結晶層(0≦z<0.5)2c‐nの2層を1組としたものが1〜500組積層されている構成とする。

(もっと読む)

SiGeオンインシュレータ基板材料

【課題】 向上された緩和、かなり低い欠陥密度、および改善された表面品質を有する

緩和されたSiGeオンインシュレータ基板を形成する方法を提供すること。

【解決手段】 方法が、第1の単結晶Si層の表面上にSiGe合金層を形成するステ

ップを含む。第1の単結晶Si層は、Ge拡散に対する耐性がある下の障壁層との界面を

有する。次に、界面での、または界面付近での機械的な分断を可能にする欠陥を形成する

ことができるイオンが構造内に注入され、その後、注入されたイオンを含む構造に、第1

の単結晶Si層およびSiGe層を通るGeの相互拡散を可能にする加熱ステップを施し

て、障壁層の上に、実質的に緩和された単結晶であり均質のSiGe層を形成する。改善

された性質を有するSiGeオンインシュレータ、およびそれを含むヘテロ構造も提供さ

れる。

(もっと読む)

窒化物半導体素子の製造方法

【課題】結晶性の良い窒化物半導体よりなる窒化物半導体基板を用い裏面に電極を形成した発光素子、受光素子等の窒化物半導体素子を提供する。

【解決手段】窒化物半導体と異なる材料よりなる基板の上に、窒化物半導体を100μm以上の膜厚で成長させ、前記基板を除去することによって得られた窒化物半導体基板であり、該窒化物半導体基板の表面の凹凸差が±1μm以下になるまで表面研磨した研磨面に成長される。好ましくは、前記表面の凹凸差が±0.5μm以下である。前記窒化物半導体基板はn型不純物がドープされている。

(もっと読む)

窒化物半導体単結晶

【課題】Si基板上に、半極性面である(10-1m)面(m:自然数)の窒化物半導体膜が厚さ1μm以上で形成され、発光デバイスにも好適に用いることができる窒化物半導体単結晶を提供する。

【解決手段】Si(100)に対して、<100>から<110>方向へのオフカット角度が1〜35°であるSi基板1上に、SiCまたはBPのいずれか1種以上からなるバッファー層2a(2b)およびAlNバッファー層3を介して、GaN(10-1m)、AlN(10-1m)またはInN(10-1m)からなる単結晶膜4、あるいはまた、GaN(10-1m)およびAlN(10-1m)の超格子構造を形成する。

(もっと読む)

半導体ウエーハ及び半導体素子及び製造方法

【課題】 シリコン基板上に窒化物半導体領域を設けると、半導体ウエーハに反りが発生する。

【解決手段】 シリコン基板2の上に窒化物半導体から成るバッファ領域3を介してHEMT用の窒化物半導体から成る主半導体領域4を設ける。前記バッファ領域4を、第1の多層構造バッファ領域5と第2の多層構造バッファ領域8とで構成する。第1の多層構造バッファ領域5を複数のサブ多層構造バッファ領域6と複数の単層構造バッファ領域7で構成する。サブ多層構造バッファ領域6を、交互に配置された複数の第1及び第2の層で構成する。第1の層をアルミニウムを第1の割合で含む窒化物半導体で形成する。第2の層をアルミニウムを含まない又は前記第1の割合よりも小さい第2の割合で含む窒化物半導体で形成する。第2の多層構造バッファ領域8を第3及び第4の層で構成する。第3の層のアルミニウム割合を第1の割合よりも低くする。

(もっと読む)

半導体電子デバイス

【課題】異種基板上のバッファ層の結晶性を向上させた窒化物系化合物半導体を有する半導体電子デバイスを提供する。

【解決手段】窒化物系化合物半導体を有する半導体電子デバイスにおいて、基板10上に窒化物系化合物半導体からなるバッファ層20及び半導体動作層30を順次積層してなり、前記バッファ層20は、第1の層22と第2の層23が積層された複合層を1層以上有し、第1の層22と第2の層23との各格子定数の差は0.2%以上であり、第1の層22の厚さは、100nm以上、1000nm以下である。

(もっと読む)

温度センサおよびその製造方法

【課題】シリコン/ゲルマニウム(SiGe)超格子温度センサをその製造方法とともに提供する。

【解決手段】上記製造方法では、第1のシリコン基板に能動CMOS素子を形成するとともに、第2のSOI(Si-on-insulator)基板上にSiGe超格子構造を形成する。次に、第1の基板を第2の基板に貼り合わせて、貼り合わせ基板を形成する。そして、SiGe超格子構造とCMOS素子とを接続する電気接続配線を形成し、SiGe超格子構造と貼り合わせ基板との間に空洞を形成する。

(もっと読む)

堆積途中でアニーリングを行うことによってバンドが設計された超格子を有する半導体素子の作製方法

半導体素子の作製方法は、各々が複数の層からなる複数の群を積層した状態で有する超格子を作製する工程を有して良い。複数の層からなる群の各々は、基礎となる半導体部分を画定する、複数の積層された基礎となる半導体分子層、及び隣接する基礎となる半導体部分の結晶格子の内部に束縛された少なくとも1の非半導体分子層を有して良い。当該方法はまた、その超格子が完全に形成される前に少なくとも1回のアニーリングを行う工程をも有して良い。  (もっと読む)

(もっと読む)

歪み薄膜の緩和方法

本発明は、歪み薄膜を緩和するための方法に関する。歪み薄膜は、初期支持体の第一の主面によって固定され、薄膜の第二の主面は接触面として知られ、この方法は、以下の連続するステップを有している:

---接触面として知られている主自由面を具備し、ポリマーの熱膨張率が薄膜のそれよりも大きいポリマー層を有する中間支持体を提供するステップと、

---歪み薄膜の接触面とポリマー層の接触面とを接着して接触させるステップと、

---初期支持体(9)を取り除くことによって、しわの形成によって薄膜(8)の緩和を引き起こし、薄膜の第一の主面を露呈させるステップと、

---緩和させられた薄膜(8)を伸ばして、しわを取り除くために、ポリマー層(2)の温度を増加させるステップと、

---受け入れ基板(10)の一つの面で薄膜(8)の第一の主面を固定するステップと、

---受け入れ基板と一体になった緩和させられた薄膜を得るために、中間支持体を取り除くステップ。  (もっと読む)

(もっと読む)

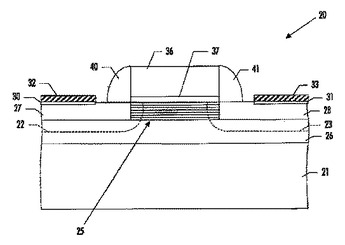

非半導体モノレイヤーを有するチャネルを含む半導体デバイス、及びその製造方法

半導体デバイスは、半導体基板及びその上の少なくとも1つのMOSFETを含んでいる。このMOSFETは、空間的に隔てられたソース領域及びドレイン領域、ソース領域とドレイン領域との間のチャネル、及びチャネルの上に位置しチャネルとの界面を画成するゲートを含んでいる。ゲートは、チャネルの上に位置するゲート誘電体と、ゲート誘電体の上に位置するゲート電極とを含んでいる。また、このチャネルは、積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体モノレイヤーの結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。上記少なくとも1つの非半導体モノレイヤーは、チャネルとゲート誘電体との間の界面に対しておよそ4−100モノレイヤーの深さに位置付けられている。  (もっと読む)

(もっと読む)

歪み超格子とその上の応力層とを含む半導体デバイス、及びその製造方法

半導体デバイスは、積層された複数の層群を有する歪み超格子層(325)、及び歪み超格子層の上方の応力層を含んでいる。歪み超格子層の各層群は、ベース半導体部分を画成する積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体部分の結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。  (もっと読む)

(もっと読む)

III族窒化物半導体素子用エピタキシャル基盤

【課題】 優れた発光効率、逆耐電圧特性および静電耐圧特性等を有するIII族窒化物半導体発光素子の製造に適したIII族窒化物半導体素子用エピタキシャル基盤を提供すること。

【解決手段】 表面粗さ(Ra)が1nm以下の基板と該基板上に直接積層されたIII族窒化物半導体層とからなり、該III族窒化物半導体層は互いに接する複数の層からなり、該複数の層の少なくとも一層は転位密度が1×107cm-2以下の層であるIII族窒化物半導体素子用エピタキシャル基盤。

(もっと読む)

窒化物半導体素子の製法

【課題】 高温のアニール処理を長時間に亘って行うことにより発生する窒素空孔の形成という問題を生じさせることなく、アクセプタの活性化を行い、キャリア濃度の高い(低抵抗の)p形の窒化物半導体層を有する窒化物半導体素子の製法を提供する。

【解決手段】 基板1上に窒化物半導体からなる半導体積層部6を形成し、その半導体積層部6の表面側から、λ=h・c/E以下(EはMgとHとの結合を切り離し得るエネルギー)の波長λのレーザ光を照射する。その後に、300〜400℃の熱処理を行う。そして、通常の窒化物半導体LEDの製造工程と同様に透光性導電層7を設け、半導体積層部6の一部をエッチングにより除去して露出するn形層3にn側電極9を、透光性導電層7の表面にp側電極8を形成する。

(もっと読む)

自立(Al,In,Ga)Nウェーハ製作のためのウェーハ分離技術

異種基板から厚くエピタキシャル成長した窒化物薄膜をin situ分離することによる自立(Al,In,Ga)N基板を作製する方法が開示される。(Al,In,Ga)N薄膜の成長に適した基板が選択され、異種イオンが該基板に注入されて比較的急峻な濃度分布を形成する。(Al,In,Ga)N薄膜が該基板上に成膜され、該成膜された薄膜を降温して、熱膨張不整に関係した歪を導入すると、該薄膜は該基板から自然に分離する。  (もっと読む)

(もっと読む)

構造均一性を有する半導体構造

組成変動を有する半導体層を備えている半導体構造を形成する。この半導体層の最上表面は、実質的にヘイズを有していない。  (もっと読む)

(もっと読む)

窒化物系半導体素子の製造方法及び窒化物系半導体素子

【課題】材料的な制限を必要とせず、ウェハの反りの微調整が可能な調整層を用い、ウェハの反りに起因する支持基板との不均一な接合を低減する窒化物系半導体素子を提供する。

【解決手段】窒化物系半導体素子は、成長用基板1上に、少なくとも1層以上の窒化物系半導体素子層3を形成する工程と、窒化物系半導体素子層3上に、支持基板10の一方の主面を接合する工程と、接合された窒化物系半導体素子層3及び支持基板10から成長用基板1を除去する工程とによって製造される。窒化物系半導体素子は、支持基板10の他方の主面上に、支持基板10とは熱膨張係数の異なる材料からなる調整層11を備える。

(もっと読む)

半導体装置の製造方法

【課題】 ゲルマニウム濃度の高いシリコン・ゲルマニウム層を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 シリコン及び酸素を含む層15とシリコン・ゲルマニウム層13aとを含み、シリコン及び酸素を含む層がシリコン・ゲルマニウム層と基板11との間に位置する積層構造を形成する工程と、シリコン・ゲルマニウム層を酸化性雰囲気中での熱処理により酸化して、シリコン・ゲルマニウム層の上部にゲルマニウムがほとんど残存しないシリコン酸化層16aを形成することにより、シリコン・ゲルマニウム層の膜厚を減少させ、シリコン・ゲルマニウム層のゲルマニウム濃度を増加させる工程と、を有する。

(もっと読む)

除去構造を含んでなるウェハーの、その薄層を除去した後の、機械的手段による循環使用

除去構造を含んでなるウェハーの、その薄層を除去した後の、機械的手段による循環使用。半導体材料から選択された材料を含んでなる有用な層を除去した後、ドナーウェハー(10)を循環使用する方法。ドナーウェハー(10)は、順に、基材(1)および除去構造(I)を含んでなり、該除去構造(I)は、除去前は、除去すべき有用な層を含んでなり、本方法は、除去が行われる側にある物質を除去することを含んでなり、物質の除去が、物質を除去した後、除去構造の少なくとも一部(I’)が残り、この除去構造の少なくとも一部(I’)が、少なくとも一個の他の有用な層(該層は、有用な層を再形成する補充工程無しに、循環使用の後に除去できる)を包含するように、機械的手段を使用することを含んでなることを特徴とする。本願は、同様に、本発明により循環使用できるドナーウェハー(10)から薄層を除去する方法、および本発明により循環使用できるドナーウェハー(10)にも関する。  (もっと読む)

(もっと読む)

改善された熱伝導率をもつ歪みシリコン材料を形成するための方法

【課題】 改善された熱伝導率をもつ歪みシリコン材料を形成するための方法を提供すること。

【解決手段】 改善された熱伝導率を有するSiGe層上に歪みSi層を形成するための方法が開示される。第1の堆積ステップにおいて、Si又はGeの第1の層が堆積され、第2の堆積ステップにおいて、他方の要素の第2の層が堆積され、第1の堆積ステップ及び第2の堆積ステップが繰り返されて、複数のSi層と複数のGe層とを有する複合SiGe層が形成される。Si層及びGe層のそれぞれの厚さは、複合SiGe層の望ましい構成比による。複合SiGe層は、Si及びGeのランダム合金のものより大きい熱伝導率を有するSi及びGeのデジタル合金として特徴付けられる。この方法は、さらに、Si層を複合SiGe層に堆積するステップをさらに含み、複合SiGe層は緩和SiGe層として特徴付けられ、Si層は歪みSi層である。SiGe層におけるより大きな熱伝導率のためには、第1の層及び第2の層は、各々が、本質的に、単一の同位体で構成されるように堆積することができる。

(もっと読む)

21 - 40 / 44

[ Back to top ]