Fターム[5F152LN34]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | 選択成長 (227) | マスク、基板の加工等 (51)

Fターム[5F152LN34]に分類される特許

1 - 20 / 51

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、ベース基板の上に、接着層、バッファ層および活性層をエピタキシャル成長法により順次形成する層形成工程を有し、接着層形成工程が、第1結晶層を形成する工程と第2結晶層を形成する工程と、を有し、第1結晶層の形成後であって第2結晶層の形成前の第1の段階、および、第2結晶層の形成後であってバッファ層の形成前の第2の段階、からなる群から選択された少なくとも1つの段階において、3族原料ガスの供給を停止するとともに成長室の内部を、アンモニアを含むガスの雰囲気に一定時間だけ維持する雰囲気維持工程を有する半導体基板の製造方法を提供する。

(もっと読む)

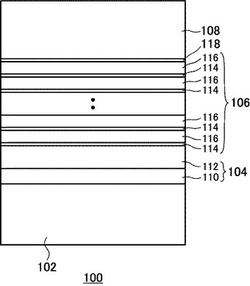

半導体基板および半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板であって、前記バッファ層が、第1結晶層と第2結晶層が交互に複数積層された積層構造体であり、前記第1結晶層が、AlmGa1−mN、(但し0≦m≦1)で表される結晶からなり、前記第2結晶層が、AlnGa1−nN、(但し0≦n≦1、m>n)で表される結晶からなり、前記第1結晶層の格子緩和度が、前記第2結晶層の格子緩和度より大きい半導体基板を提供する。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板の製造方法であって、前記ベース基板をエピタキシャル結晶成長装置の成長室に設置した後に、前記ベース基板の温度を1000℃以上に維持しつつ前記ベース基板の表面をアンモニアガスとキャリアガスとの混合ガスに暴露するアンモニアガス暴露工程と、前記アンモニアガス暴露工程の後に、前記ベース基板の上に、前記接着層、前記バッファ層および前記活性層をエピタキシャル成長法により順次形成する層形成工程と、を有する半導体基板の製造方法を提供する。

(もっと読む)

単結晶炭化シリコン膜の製造方法及び単結晶炭化シリコン膜付き基板の製造方法

【課題】結晶欠陥の少ない高品質なエピタキシャル膜を得ることが可能な単結晶炭化シリコン膜の製造方法及び単結晶炭化シリコン膜付き基板の製造方法を提供する。

【解決手段】シリコン基板11上に単結晶炭化シリコン膜14を形成する単結晶炭化シリコン膜14の製造方法であって、シリコン基板11の表面に炭化シリコン膜12を形成する第1の工程と、炭化シリコン膜12の表面にマスク材13を形成する第2の工程と、マスク材13に開口部13hを形成し、炭化シリコン膜12の一部を露出させる第3の工程と、原料ガスを含むガス雰囲気中でシリコン基板11を加熱し、炭化シリコン膜12を基点として単結晶炭化シリコンをエピタキシャル成長させ、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14を形成する第4の工程と、を含み、原料ガスを含むガス雰囲気の圧力は、5.0×10−4Pa以上かつ0.5Pa以下である。

(もっと読む)

窒化物半導体結晶層の製造方法及び窒化物半導体結晶層

【課題】より良質な窒化物半導体結晶層を製造する方法及び窒化物半導体結晶層を提供する。

【解決手段】実施形態によれば、表面にシリコン酸化膜が形成された基体の上に設けられた20μm以下の厚さのシリコン結晶層の上に、1μm以上の厚さの窒化物半導体結晶層を形成する。シリコン結晶層の上に、窒化物半導体結晶層のうちの第1の部分を形成した後、第1の部分よりも高い温度で第2の部分を形成する。シリコン結晶層は、シリコン結晶層の層面に対して平行な面内において、0.5mm以上、10mm以下の特性長さを持つ島状に区分されている。区分されたシリコン結晶層のそれぞれの上に選択的に互いに離間した複数の窒化物半導体結晶層を形成する。シリコン結晶層の少なくとも一部を窒化物半導体結晶層に取り込ませ、シリコン結晶層の厚さを減少させる。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル領域に応力を印加するよう作用する階段状のソース/ドレイン・エピタキシャル領域を、製造プロセスを有意に複雑あるいは冗長とすることなく形成する。

【解決手段】 ゲート電極をマスクとしてドーパントを注入し、半導体基板内にドーパント注入領域を形成する(S2)。サイドウォールの形成(S3)後、ゲート電極及びサイドウォールをマスクとして半導体基板内に第1のリセスを形成する(S4)。このとき、第1のリセスの内壁の一部からドーパント注入領域が露出される。その後、上記ドーパント注入領域を選択エッチングにより除去し、第1のリセスに連通し且つ第1のリセスより浅い第2のリセスを形成する(S5)。それにより、階段状のリセスが形成される。そして、第1のリセス及び第2のリセス内に、チャネル領域へのストレッサとして作用する半導体材料を成長させてソース/ドレイン領域を形成する(S6)。

(もっと読む)

半導体基板上での逆相境界の無いIII−V化合物半導体材料およびその製造方法

【課題】逆相境界(APB)の無いIII−V化合物半導体材料およびその製造方法を提供する。

【解決手段】III−V化合物半導体材料の製造方法は、a){001}配向を有する第1半導体材料からなる基板と、基板の上に位置し、これと接触する絶縁層と、絶縁層内に、少なくとも部分的に基板を露出させる凹部領域を用意する工程と、b)凹部領域において露出基板の上に位置し、これと接触するバッファ層を形成する工程工程と、c)バッファ層の表面を粗面化するために、熱処理を印加する工程とを含み、バッファ層が、熱処理の印加後に二重ステップ表面を有する丸み形状をなし、d)凹部領域を、バッファ層の二重ステップ表面の上に位置し、これと接触するIII−V化合物半導体材料で少なくとも部分的に充填する工程をさらに含む。

(もっと読む)

能動領域の欠陥が低減されユニークな接触スキームを有する半導体デバイス

【課題】本発明は、能動領域の欠陥を低減した半導体デバイスの制作方法を提供する。

【解決手段】本願発明は、表面照射光センサを製作する方法であって、

(a)能動領域の半導体ピクセルのアレイを形成する工程と、

(b)各ピクセル内に、隔離された互いに反対の導電性タイプの接触領域を形成する工程と、

(c)前記接触領域への金属コンタクトを形成し、各ピクセル内で、前記金属コンタクトが、前記接触領域の上部表面面積の総計の少なくとも約30%を覆う工程とを含む、方法に関する。

(もっと読む)

半導体装置の製造方法

【課題】解像度限界より小さい寸法のパターンを規則的に形成する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、構造体としての第1及び第2のパターン13a、13b間に露出する種結晶としての半導体基板10からエピタキシャル結晶としての単結晶膜14を形成し、単結晶膜14を単結晶膜14の融点以下の温度で加熱することにより単結晶膜14を流動させ、流動した単結晶膜14が凝集することにより複数の凝集体15を第1及び第2のパターン13a、13b間に形成することを含む。

(もっと読む)

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】中間層としてGe結晶を用いる場合の化合物半導体へのGe原子の混入を抑制する。

【解決手段】ベース基板と、ベース基板上に形成された第1結晶層と、第1結晶層を被覆する第2結晶層と、第2結晶層に接して形成された第3結晶層とを備え、第1結晶層が、ベース基板における第1結晶層と接する面と面方位が等しい第1結晶面、及び、第1結晶面と異なる面方位を有する第2結晶面を有し、第2結晶層が、第1結晶面と面方位が等しい第3結晶面、及び、第2結晶面と面方位が等しい第4結晶面を有し、第3結晶層が、第3結晶面及び第4結晶面のそれぞれの少なくとも一部に接しており、第1結晶面に接する領域における第2結晶層の厚みに対する第2結晶面に接する領域における第2結晶層の厚みの比が、第3結晶面に接する領域における第3結晶層の厚みに対する第4結晶面に接する領域における第3結晶層の厚みの比よりも大きい半導体基板を提供する。

(もっと読む)

半導体ウェハの製造方法、半導体素子の製造方法、半導体ウェハ、半導体素子および電子装置

【課題】 歩留まりが大幅に改善された半導体ウェハの製造方法を提供する。

【解決手段】 本発明の半導体ウェハの製造方法は、基板301上の一部にストライプ状の保護膜302を形成する保護膜形成工程と、前記保護膜形成工程後、前記基板301上における前記保護膜302形成部位以外の部位に半導体結晶を成長させて半導体層を形成する半導体層形成工程とを含み、前記基板301として、前記保護膜302の長さ方向と平行な方向のオフ角θpの絶対値|θp|が、前記保護膜302の長さ方向と直交する方向のオフ角θoの絶対値|θo|よりも小さく、且つ、|θp|≦0.2°を満たすものを用いることを特徴とする。

(もっと読む)

半導体素子の製造方法

【課題】ピッティング不良が抑制され、簡単な工程を通じて形成することができる高性能の半導体素子の製造方法を提供する。

【解決手段】半導体基板にゲート電極を形成する段階と、ゲート電極に側壁スペーサを形成する段階と、側壁スペーサの両側の半導体基板を一部エッチングしてトレンチを形成する段階と、トレンチ内にSiGe混晶層を形成する段階と、SiGe混晶層上にシリコン層を形成する段階と、シリコン層の面の結晶方向に従って、エッチング率が異なるエッチング液を利用してシリコン層の一部をエッチチングすることによって111傾斜面を有するシリコンファセット(Si facet)を含むキャッピング層を形成する段階と、を有する。キャッピング層を含むことによって半導体素子でホールの移動度が高まる。キャッピング層内のピッティング不良が減少することによって半導体素子の特性が良好になる。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加しつつ、基板やソース/ドレイン領域においてリーク電流の発生が効果的に抑制された半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の不純物を含み、素子形成領域170を有する半導体基板101と、素子形成領域170上にゲート絶縁膜132を挟んで形成されたゲート電極125と、ゲート電極125の両側方に形成され、第2導電型の不純物を含むソース/ドレイン領域150とを備える。素子形成領域170のうちゲート電極の両側方に位置する領域には、半導体基板101の主面に対して傾いた半導体単結晶のファセット面を露出させる側壁を有し、コーナー部が丸められたリセス130が形成されており、ソース/ドレイン領域150は、リセス130に埋め込まれたシリコン混晶で構成されている。

(もっと読む)

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】単一のシリコン基板上に種類の異なる半導体結晶層をエピタキシャル成長させる場合に、表面の平坦性を向上し、半導体デバイスの信頼性を高める。

【解決手段】第1窪みおよび第2窪みが形成されたシリコン結晶を表面に有するベース基板と、第1窪みの内部に形成され、露出されている第1のIVB族半導体結晶と、第2窪みの内部に形成された第2のIVB族半導体結晶と、第2窪みの内部の第2のIVB族半導体結晶上に形成され、露出されているIII−V族化合物半導体結晶とを備える半導体基板を提供する。

(もっと読む)

半導体基板及び半導体基板の製造方法

【課題】半導体基板のアライメントマークを繰り返し使用する。

【解決手段】ベース基板にアライメントマークを形成する段階と、アライメントマークを形成する段階の後に、ベース基板上のアライメントマークを含む領域に、結晶成長を阻害する阻害層を形成する段階と、アライメントマークの位置を基準とする開口を形成すべき位置を示す情報に基づいて、阻害層におけるアライメントマークが設けられていない領域に、ベース基板を露出する開口を形成する段階と、開口内に半導体結晶を成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】シリコン基板を用いてGaN系の良質な半導体結晶層を形成する。

【解決手段】第1領域と第2領域とを表面に有する基板と、前記第1領域の上方に形成された第1半導体と、を含み、前記基板は、表面がSixGe1−x(0≦x≦1)であり、前記第1領域は、前記第2領域により囲まれ、前記第1半導体は、窒素原子を含有する3−5族化合物半導体であり、単結晶であり、且つ前記SixGe1−xと格子整合または擬格子整合し、前記第2領域は、前記第1領域とは性状が異なる半導体基板を提供する。

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】シリコン基板を用いてGaAs系の良質な半導体結晶膜を形成する。

【解決手段】第1領域と第2領域とを表面に有する基板と、前記第1領域の上方に形成された第1半導体と、を含み、前記基板は、表面がSixGe1−x(0≦x≦1)であり、前記第1領域は、前記第2領域により囲まれ、前記第1半導体は、砒素を含有する3−5族化合物半導体であり、単結晶であり、且つ前記SixGe1−xと格子整合または擬格子整合し、前記第2領域は、前記第1領域とは性状が異なる半導体基板を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】 微細化したMOSFETにおいて、ボイドやシームの発生無しに素子分離領域

に絶縁膜を埋め込むことができ、キャリアの移動度向上が可能な半導体装置及び半導体装

置の製造方法を提供する。

【解決手段】 本発明では、シリコンを主成分とする半導体基板101と、半導体基板の

素子形成領域上にゲート絶縁膜105を介して形成されたゲート電極平行方向に伸びるゲ

ート電極106と、素子形成領域に前記ゲート電極下のチャネル領域を挟むように前記半

導体基板中に形成された拡散層と、素子形成領域を囲むように設けられ、ゲート電極平行

方向に対して垂直なゲート電極垂直方向に伸びる第1の素子分離絶縁膜112と、ゲート

電極平行方向に伸び、第1の素子分離絶縁膜と幅または深さが異なる第2の素子分離絶縁

膜113とからなる素子分離絶縁膜とを有する半導体装置が得られる。

(もっと読む)

ナノスケールのエピタキシー技術(Nano−ScaleEpitaxyTechnology)を用いた高品質のヘテロエピタキシー

【課題】ナノスケールのエピタキシー技術を用いた高品質のヘテロエピタキシーを提供する。

【解決手段】集積回路構造は、第一半導体材料からなる半導体基板と、半導体基板の二つの絶縁体と、二つの絶縁体間にあってそれらの側壁に隣接する半導体領域とを備える。半導体領域は、第一半導体材料と異なる第二半導体材料からなり、幅は約50 nmより小さい。

(もっと読む)

1 - 20 / 51

[ Back to top ]