Fターム[5F152NN09]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 3−5族 (475) | 窒化物 (171)

Fターム[5F152NN09]に分類される特許

161 - 171 / 171

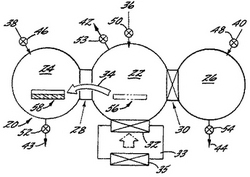

高性能/高スループット複数チャンバMOCVD成長装置

【課題】反応チャンバにおいて反応体メモリーを防止しながら、複数工程複数チャンバ化学気相堆積を行う方法を提供する。

【解決手段】第一気相堆積チャンバ24において気相堆積を用いて基板56上に半導体材料の層を堆積させる工程、次いで、堆積成長後及び前記チャンバ24を開ける前に、前記第一堆積チャンバ中に残留している気相堆積原料ガスを減少させるために成長チャンバ24から排気する工程を含む。第二堆積チャンバ26から第一堆積チャンバ24を分離して第一堆積チャンバ24中に存在する反応体が第二堆積チャンバ26における堆積に影響を及ぼさないようにしながら、また、成長停止効果を最小限に抑えるか又は排除する環境を維持しながら、基板56を第二堆積チャンバ26へと搬送する。搬送工程の後、異なる半導体材料の追加の層を、第二チャンバ26において、気相堆積によって第一堆積層の上に堆積させる。

(もっと読む)

III族窒化物半導体積層体及びIII族窒化物半導体発光素子、並びにそれらの製造方法

【課題】 低抵抗で、しかも連続性のあるn型III族窒化物半導体層を安定して得る方法、及びこの方法によって得られるIII族窒化物半導体積層体を提供する。

【解決手段】 n型不純物のドーピング濃度が高いIII族窒化物半導体の層である高濃度ドープ層(104a)と、n型不純物のドーピング濃度がこれよりも低いIII族窒化物半導体の層である低濃度ドープ層(104b)とを交互に、ドーピングされるn型不純物の濃度以外のリアクタ内の成長条件も更に異ならせて、積層することを含む、III族窒化物半導体積層体の製造方法、並びにこの方法を含むIII族窒化物半導体発光素子の製造方法とする。また、これらの方法によって得ることができるIII族窒化物半導体積層体、及びIII族窒化物半導体発光素子とする。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。したがって、埋込み部を形成する際のエッチングにより損傷をきたした埋込みゲートを提供することによって生じ得るゲート領域劣化が低減された、高品質のゲートコンタクトおよびオーミックコンタクトを提供することができる。  (もっと読む)

(もっと読む)

材料複合体ウェーハの製造方法

【課題】

材料複合体ウェーハの製造方法に関し、特に非均質材料複合体に関し、また特に、異なる物理的特性及び/又は化学的特性、特に異なる熱膨張係数を備えた少なくとも2種類の材料を含む非均質材料複合体に関し、よりよい品質の材料複合体ウェーハ及びより高い製品歩留まりを達成する。

【解決手段】ソース基板に所定の分割領域を形成するステップと、ソース‐ハンドル複合体を形成するためにソース基板をハンドル基板に取り付けるステップと、ソース基板を所定の分割領域において脆弱化するためにソース基板を熱アニールするステップとを含む。本方法は更に、脆弱化された所定の分割領域の物理的な強度を特徴づけている脆弱化の程度を測定するステップを含み、この測定するステップが熱アニールステップの間及び/又は後で実行される。

(もっと読む)

窒化ガリウム材料及び方法

窒化ガリウム材料領域を含む半導体材料、及びこのような構造と関連する方法が提供される。前記半導体構造は前記構造の中に形成される歪み吸収層を含む。前記歪み吸収層は前記基板(例えばシリコン基板)と上部層の間に形成されてよい。前記歪み吸収層が非常に薄く、非晶質構造を有し、窒化ケイ素からなる材料から形成されることが好ましい場合がある。前記歪み吸収層は、他の優位点の中で、他の上部層(たとえば窒化ガリウム材料領域)における他の種類の欠陥の形成を制限する、上部層(例えば、窒化物からなる材料層)において形成されるミスフィット転位数を削減できる。したがって、歪み吸収層の存在は、素子性能の改善につながることがある窒化ガリウム材料領域の質を改善できる。  (もっと読む)

(もっと読む)

決定可能な熱膨張係数を有する基板

本発明は、結晶材料から選択された材料で作られた転写層(20)を受ける目的の複合支持基板(10)に関し、したがって、その集合体は、エピタキシャル用基板(30)を形成し、主要表面と平行に対称な長手方向の平面(100)を有し、且つ規定の温度Tで第1熱膨張係数を有し、対称平面のどちらの側にも横方向に延在する中央第1層(1)と、少なくとも1対の横方向の層(2、2’;3、3’)、即ち、互いに向き合う層を有する各対の層であって、前記対称平面に関して、ほぼ対称である複合支持基板(10)内の配列、前記温度Tで互いにほぼ同一である第2熱膨張係数、互いにほぼ同一である厚さ、である前記各対の層と、からなり、並びに、前記複合支持基板(10)が前記温度Tで転写層(20)の材料の熱膨張係数に近い全体的熱膨張係数を前記温度Tで有するように、前記複合支持基板(10)の層を構成する材料が、選択されていることを特徴とする。本発明は、前記複合支持基板上に有効層を形成する工程及びエピタキシャル基板を含む構造にも関係する。  (もっと読む)

(もっと読む)

ダイアモンド基板上炭化珪素並びに関連するデバイス及び方法

ワイドバンドギャップ材料内に、接合温度低下、動作中の高電力密度化、及び定格電力密度における信頼性向上を達成する高電力デバイスを形成する方法を、結果的に得られる半導体構造及びデバイスと共に開示する。本方法は、ダイアモンドの層を炭化珪素ウェハに添加して、得られる複合ウェハの熱伝導率を高め、その後、炭化珪素の上におけるエピタキシャル成長を支持するためにその十分な厚さを保持しつつ、複合ウェハの炭化珪素部分の厚さを削減し、複合ウェハの炭化珪素面を、その上におけるエピタキシャル成長のために、準備し、第III族窒化物ヘテロ構造を、ウェハの準備した炭化珪素面に添加することを含む。  (もっと読む)

(もっと読む)

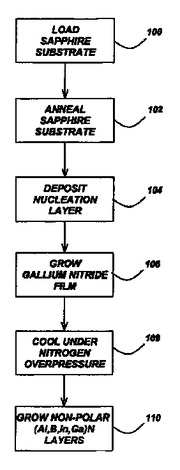

非極性(Al、B、In、Ga)N量子井戸

非極性a面GaN/(A1、B、In、Ga)N多重量子井戸(MQW)を製造する方法。a面MQWは、有機金属化学気相成長法(MOCVD)によって適切なGaN/サファイアテンプレート層上に成長し、井戸幅は20Å〜70Åの範囲である。a面MQWからの室温光ルミネセンス(PL)放射エネルギーは、自己無頓着ポアソン−シュレディンガー(SCPS)計算を使用してモデリングされた正方井戸傾向を伴った。最適PL放射強度は、a面MQWについて52Åの量子井戸幅で得られる。  (もっと読む)

(もっと読む)

半導体チップの製造方法

本発明によれば、成長基板ウエハ(1)が設けられ、前記成長基板ウエハ(1)の主平面(100)に対して平行に存在する分離ゾ−ン(4)が当該成長基板ウエハ(1)内に形成され、前記成長基板ウエハ(1)に補助支持体ウエハ(2)が接合され、前記分離ゾーン(4)の層から成長基板ウエハ(1)の補助支持体ウエハ(2)とは反対側部分(11)が当該分離ゾーン(4)に沿って分離され、前記補助支持体ウエハ(2)上に残った成長基板ウエハの残留部分(12)上に、後続の半導体層列(5)のエピタキシャル成長のための成長面(121)が形成され、前記成長面(121)上に半導体層列(5)がエピタキシャル成長され、前記半導体層列(5)上にチップ基板ウエハ(7)が被着され、前記補助支持体ウエハ(2)が分離され、前記半導体層列(5)とチップ基板ウエハ(7)の接続部が、相互に分離された半導体チップ(20)に個別化される。  (もっと読む)

(もっと読む)

応力のかかるシステムのための基板および当該基板上での結晶成長法

本発明は、核生成層(2)、多結晶性または多孔性緩衝層(4)、および支持体基板(6)を含む結晶成長用支持体を提供する。 (もっと読む)

マスクを通るラテラル成長による窒化ガリウム基板の製造とそれから製作されたデバイス

多段を用いたエピタキシャルラテラルオーバーグロースにより窒化ガリウム基板の成長を行う。開口部領域を有するマスクされた基板上で、選択的成長により最初に三角形ストライプを作成すると、大部分の貫通転位は90°曲がる。第2段では、成長条件を変化させてラテラル成長速度を高め、平坦な(0001)面を生じさせる。この段階で、表面上の転位密度は<5×107cm-2である。転位は主に、2つのラテラル成長したファセットがぶつかり合って合体した合体領域に存在する。転位密度をさらに低下させるため、2回目のマスキング工程を開口部が1回目のそれの真上にくるように行う。合体領域の貫通転位(TD)は上層には伝播しない。したがって、転位密度は全表面にわたって<1×107cm-2まで低下する。  (もっと読む)

(もっと読む)

161 - 171 / 171

[ Back to top ]