Fターム[5F152NN09]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 3−5族 (475) | 窒化物 (171)

Fターム[5F152NN09]に分類される特許

41 - 60 / 171

半導体基板、半導体基板の製造方法、および電磁波発生装置

【課題】複数の異なる周波数を出力する半導体基板を提供する。

【解決手段】p型半導体またはn型半導体を含む第1の不純物半導体と、第1の不純物半導体に接する複数の空乏領域を有する空乏化半導体とを備え、複数の空乏領域のそれぞれは、第1の不純物半導体との第1界面と、第1界面と対向する表面とを有し、複数の空乏領域のそれぞれは、第1界面に垂直な方向における第1界面と表面との平均距離および組成の少なくとも一つが異なる半導体基板を提供する。

(もっと読む)

エピタキシャル構造、その形成方法、および、それを含むデバイス

半導体ウェハの製造方法、半導体素子の製造方法、半導体ウェハ、半導体素子および電子装置

【課題】 歩留まりが大幅に改善された半導体ウェハの製造方法を提供する。

【解決手段】 本発明の半導体ウェハの製造方法は、基板301上の一部にストライプ状の保護膜302を形成する保護膜形成工程と、前記保護膜形成工程後、前記基板301上における前記保護膜302形成部位以外の部位に半導体結晶を成長させて半導体層を形成する半導体層形成工程とを含み、前記基板301として、前記保護膜302の長さ方向と平行な方向のオフ角θpの絶対値|θp|が、前記保護膜302の長さ方向と直交する方向のオフ角θoの絶対値|θo|よりも小さく、且つ、|θp|≦0.2°を満たすものを用いることを特徴とする。

(もっと読む)

発光素子および発光素子の製造方法

【課題】本発明は、信頼性が向上し、発光構造物のクラック及びひび割れなどの損傷を防止し、発光効率を向上させる発光素子の製造方法を提供するためのものである。

【解決手段】本発明に従う発光素子の製造方法は、多数のチップ領域及びアイソレーション領域を含む基板の上に多数の化合物半導体層を形成するステップと、前記各チップ領域に発光構造物を形成し、前記アイソレーション領域に緩衝構造物を形成するために前記化合物半導体層をエッチングするステップと、前記発光構造物及び前記緩衝構造物の上に伝導性支持部材を形成するステップと、レーザリフトオフ工程を用いて前記基板を除去するステップと、前記発光構造物を分離するステップと、を含み、前記緩衝構造物は前記発光構造物から離隔する。

(もっと読む)

イオン・インプラント・アイソレーションによるLED製作

【課題】電気的に隔離された発光ダイオードを提供する。

【解決手段】半導体発光ダイオードは、半導体基板51と、基板上にあるn型III群窒化物のエピタキシャル層52と、n型エピタキシャル層上にあり当該n型層と共にp−n接合部を形成する、III群窒化物のp型エピタキシャル層53と、n型エピタキシャル層上にありp型エピタキシャル層に隣接し、p−n接合部58の一部を電気的に隔離する抵抗性窒化ガリウム領域54とを含む。p型エピタキシャル層上に金属接点層55を形成する。方法の実施形態では、p型エピタキシャル領域上に打ち込みマスクを形成し、p型エピタキシャル領域の部分にイオンを打ち込んでp型エピタキシャル領域の部分を半絶縁性にすることによって、抵抗性窒化ガリウム境界を形成する。フォトレジスト・マスク又は十分に厚い金属層を、打ち込みマスクとして用いることができる。

(もっと読む)

GaN基板およびその製造方法、GaN層接合基板の製造方法、ならびに半導体デバイスの製造方法

【課題】加工しろが小さく一様な加工が容易なGaN基板およびその製造方法、かかるGaN基板を用いたGaN層接合基板および半導体デバイスの製造方法を提供する。

【解決手段】本GaN基板20は、第1領域20jと、第1領域20jに比べてGa/N組成比が高い第2領域20iとを含み、第2領域20iは、一方の主面20mから所定の深さDを中心に深さD−ΔDから深さD+ΔDまで広がり、深さDにおけるGa/N組成比と第1領域20jの深さD+4ΔD以上の深さにおけるGa/N組成比との差が、深さD+ΔDにおけるGa/N組成比と第1領域20jの深さD+4ΔD以上の深さにおけるGa/N組成比との差の3倍であり、第2領域20iのGa/N組成比が、第1領域20jの深さD+4ΔD以上の深さにおけるGa/N組成比に対して1.05以上である。

(もっと読む)

エピタキシャル基板および半導体素子

【課題】逆方向耐圧を向上可能な構造を有するIII族窒化物半導体素子を提供する。

【解決手段】ショットキダイオード11で窒化ガリウム支持基体13は、第1の面13aと第1の面の反対側の第2の面13bとを有しており、1×1018cm−3を超えるキャリア濃度を示す。窒化ガリウムエピタキシャル層15は、第1の面13a上に設けられている。オーミック電極17は、第2の面13b上に設けられている。ショットキ電極19は、窒化ガリウムエピタキシャル層15に設けられている。窒化ガリウムエピタキシャル層15の厚さD1は5マイクロメートル以上1000マイクロメートル以下である。また、窒化ガリウムエピタキシャル層15のキャリア濃度は、1×1014cm−3以上1×1017cm−3以下である。

(もっと読む)

複合基板

【課題】本発明の目的は、優れたエピタキシャル層の特性やデバイス特性を得ることができるように窒化物系化合物半導体の状態が制御された複合基板を提供することにある。

【解決手段】本発明の複合基板は、窒化物系化合物半導体からなる第1の基板と、該第1の基板を構成する窒化物系化合物半導体以外の物質からなる第2の基板とを貼り合わせてなるエピタキシャル層成長用の複合基板であって、該窒化物系化合物半導体は、六方晶の結晶構造を有し、該第1の基板に対して<0001>方向からレーザ光を入射させることにより後方散乱配置Z(X,X)−Z+Z(X,Y)−Zにて得られるバックグラウンドを除いたラマン散乱スペクトルのE2Hモードのピーク強度をI1とし、370cm-1±15cm-1または670cm-1±15cm-1のピーク強度をI2とする場合、下記式(I)を満たすことを特徴とする。

0≦I2/I1≦0.35 ・・・(I)

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】シリコン基板を用いてGaN系の良質な半導体結晶層を形成する。

【解決手段】第1領域と第2領域とを表面に有する基板と、前記第1領域の上方に形成された第1半導体と、を含み、前記基板は、表面がSixGe1−x(0≦x≦1)であり、前記第1領域は、前記第2領域により囲まれ、前記第1半導体は、窒素原子を含有する3−5族化合物半導体であり、単結晶であり、且つ前記SixGe1−xと格子整合または擬格子整合し、前記第2領域は、前記第1領域とは性状が異なる半導体基板を提供する。

(もっと読む)

III族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法

【課題】発光のブルーシフトが抑制された発光デバイスの製造に好適なIII族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本III族窒化物結晶基板1は、III族窒化物結晶基板1の任意の特定結晶格子面のX線回折条件を満たしながら結晶基板の主表面1sからのX線侵入深さを変化させるX線回折測定から得られる特定結晶格子面の面間隔において、0.3μmのX線侵入深さにおける面間隔d1と5μmのX線侵入深さにおける面間隔d2とから得られる|d1−d2|/d2の値で表される結晶基板の表面層の均一歪みが1.7×10-3以下であり、主表面の面方位が、結晶基板のc軸を含む面から[0001]方向に−10°以上10°以下の傾斜角を有する。

(もっと読む)

歪み補償半導体構造および歪み補償半導体構造を製作する方法

【課題】歪みの程度がGaNの割れの閾値を上回るならば、GaNが割れ、GaNの半導体デバイスへの使用を受容できないものにする可能性がある。

【解決手段】この半導体構造は、第1の面内無歪み格子定数を有する基板と、基板上に設けられ、第1の面内無歪み格子定数とは異なる第2の面内無歪み格子定数を有する、第1の半導体材料を含む第1の層と、基板と第1の層の間に配置され、第2の半導体材料を含む可変不整合層とを含む半導体構造、およびこの半導体構造の製作方法が提供される。可変不整合層は、第1の層を基板上に直接成長させる場合に生じる応力を下回る程度にまで第1の層の応力が低減されるように構成される。可変不整合層は、第1の層の無歪み格子定数と実質的に整合する面内歪み格子定数を有する層であってもよい。

(もっと読む)

III族窒化物半導体成長用基板、III族窒化物半導体エピタキシャル基板、III族窒化物半導体素子およびIII族窒化物半導体自立基板、ならびに、これらの製造方法

【課題】成長温度が1050℃以下のAlGaNやGaNやGaInNだけでなく、成長温度が高い高Al組成のAlxGa1-xNにおいても結晶性の良いIII族窒化物半導体エピタキシャル基板、III族窒化物半導体素子、III族窒化物半導体自立基板およびこれらを製造するためのIII族窒化物半導体成長用基板、ならびに、これらを効率よく製造する方法を提供する。

【解決手段】少なくとも表面部分2がAlを含むIII族窒化物半導体からなる結晶成長基板3と、前記表面部分2上に形成され、結晶化されたZrまたはHfからなる単一金属層4と、前記単一金属層4上に形成され、AlxGa1-xN(0≦x≦1)からなる少なくとも一層のバッファ層からなる初期成長層5と、を具える。

(もっと読む)

イオン注入III族窒化物半導体基板ならびにIII族窒化物半導体層接合基板およびIII族窒化物半導体デバイスの製造方法

【課題】反りが小さいイオン注入III族窒化物半導体基板、ならびにかかる基板を用いたIII族窒化物半導体層接合基板およびIII族窒化物半導体デバイスの製造方法を提供する。

【解決手段】本イオン注入III族窒化物半導体基板2は、両主面20a,20b側に両主面20a,20bからそれぞれ所定の深さDa,Dbで形成されているイオン注入領域20ia,20ibを含む。

(もっと読む)

半導体素子およびその製造方法

【課題】基板の表面上に積層される半導体素子層に発生する所定の方向の歪みを低減することが可能な半導体素子を提供する。

【解決手段】この半導体素子1は、第1方向(A方向)および第2方向(B方向)に平行な主表面を有するとともに第1方向に沿って延びる段差部2aが形成された窒化物系半導体からなる基板2と、基板2上に形成され、窒化物系半導体からなる下地層3、第1半導体層4および第2半導体層5とを備える。そして、下地層3および第2半導体層5の無歪みの状態における第2方向の格子定数は、それぞれ、基板2の無歪みの状態における第2方向の格子定数よりも大きく、下地層3および第2半導体層5の基板2の主表面上に形成された状態における第2方向の格子定数は、それぞれ、基板2の第2方向の格子定数よりも大きい。

(もっと読む)

半導体素子およびその製造方法

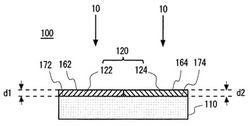

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

III族窒化物半導体層接合基板およびIII族窒化物半導体デバイスの製造方法

【課題】III族窒化物半導体層の欠落部分の少ない高品質のIII族窒化物半導体層接合基板の製造方法を提供する。

【解決手段】本III族窒化物半導体接合基板の製造方法は、主表面20mに現れる表面異状領域22の大きさおよび密度が所定の範囲内のIII族窒化物半導体基板20を準備する工程と、III族窒化物半導体基板20の主表面20m側にイオンを注入する工程と、III族窒化物半導体基板20の主表面20mに異種基板10を接合する工程と、III族窒化物半導体基板20をイオンが注入された領域20iで分離して異種基板10に接合したIII族窒化物半導体層20aを形成することにより、III族窒化物半導体層接合基板1を得る工程と、を備える。

(もっと読む)

デバイスのためのガリウム及び窒素含有超薄型エピタキシャル構造のための高速成長方法及び構造

ガリウム及び窒素含有材料の高速成長のための方法が記載される。本方法は、バルクガリウム及び窒素含有基板を提供することを含んでいる。第1の厚さの第1のエピタキシャル材料が、好ましくは擬似形態的プロセスによって、基板上に形成される。本方法は、第1の層上に第2のエピタキシャル層をも形成し、これによってスタック構造がもたらされる。スタック構造は、約2ミクロン未満の全体厚さで構成される。 (もっと読む)

Znがドープされた3B族窒化物結晶、その製法及び電子デバイス

【課題】高抵抗且つ低転位密度のZnドープ3B族窒化物結晶を提供する。

【解決手段】本発明のZnドープ3B族窒化物結晶は、比抵抗が1×102Ω・cm以上、3B族窒化物結晶中のZn濃度が1.0×1018atoms/cm3以上2×1019atoms/cm3以下、エッチピット密度が5×106/cm2以下のものである。この結晶は、液相法(Naフラックス法)により得ることができる。

(もっと読む)

GaN単結晶体およびその製造方法、ならびに半導体デバイスおよびその製造方法

【課題】GaN単結晶体を成長させる際および成長させたGaN単結晶体を基板状などに加工する際、ならびに基板状のGaN単結晶体上に少なくとも1層の半導体層を形成して半導体デバイスを製造する際に、クラックの発生が抑制されるGaN単結晶体およびその製造方法ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本GaN単結晶体10は、ウルツ型結晶構造を有し、30℃において、弾性定数C11が348GPa以上365GPa以下かつ弾性定数C13が90GPa以上98GPa以下、または、弾性定数C11が352GPa以上362GPa以下である。

(もっと読む)

III族窒化物半導体成長用基板、III族窒化物半導体エピタキシャル基板、III族窒化物半導体素子およびIII族窒化物半導体自立基板、ならびに、これらの製造方法

【課題】成長温度が1050℃以下のAlGaNやGaNやGaInNだけでなく、成長温度が高い高Al組成のAlxGa1-xNにおいても結晶性の良いIII族窒化物半導体エピタキシャル基板、III族窒化物半導体素子、III族窒化物半導体自立基板およびこれらを製造するためのIII族窒化物半導体成長用基板、ならびに、これらを効率よく製造する方法を提供する。

【解決手段】少なくとも表面部分がAlを含むIII族窒化物半導体からなる結晶成長基板と、前記表面部分上に形成されたスカンジウム窒化物膜とを具えることを特徴とする。

(もっと読む)

41 - 60 / 171

[ Back to top ]