Fターム[5F152NN09]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 3−5族 (475) | 窒化物 (171)

Fターム[5F152NN09]に分類される特許

121 - 140 / 171

半導体装置の製造方法

【課題】SBSI法において第1半導体層及び第2半導体層の膜形成の所要時間を短縮で

きるようにした半導体装置の製造方法を提供する。

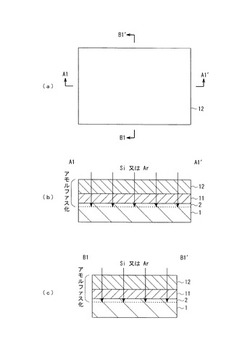

【解決手段】単結晶の半導体基板1の表面領域2上にアモルファス又は多結晶構造の第1

半導体層11を形成する工程と、第1半導体層11上にアモルファス又は多結晶構造の第

2半導体層12を形成する工程と、第2半導体層12上から半導体基板1の表面領域2に

向けてSi又はArをイオン注入して、半導体基板1の表面領域2と、第1半導体層11

及び第2半導体層12をアモルファス化する工程と、イオン注入によるアモルファス化を

行った後で半導体基板1に熱処理を施して、半導体基板1の表面領域2と、第1半導体層

11及び第2半導体層12を単結晶化する工程と、を含む。

(もっと読む)

半導体発光素子およびウエハ

【課題】製造工程を増やすことなく、光取り出し効率の向上を図ることが可能な半導体発光素子およびウエハを提供する。

【解決手段】単結晶基板に化合物半導体層3を積層し、単結晶基板を分割して個片化することで形成された半導体発光素子1において、分割された単結晶基板である個片基板2の側面21〜24は、単結晶基板における結晶構造の劈開面とは異なる面となるように、個片基板2の基準とした側面21を、(1−100)面に対して15°の角度を成すように形成されている。

(もっと読む)

AlN系III族窒化物結晶の作製方法およびAlN系III族窒化物厚膜

【課題】比較的簡便な手法によって低転位のAlN系III族窒化物厚膜を得ることができる方法を提供する。

【解決手段】所定の基材上にMOCVD法によってAlN系III族窒化物成長下地層が形成されてなるエピタキシャル基板の上に、HVPE法によってAlN系III族窒化物厚膜をエピタキシャル形成する場合に、MOCVD法における加熱温度よりも高い温度で該エピタキシャル基板を加熱処理した上で、厚膜層の形成を行うようにすることで、厚膜層の低転位化を実現することができる。すなわち、HVPE法を用いた厚膜成長に先立って、加熱処理という比較的簡便な処理を施すだけで、HVPE法による成長に際して特別の構成を有する装置を用いたり、あるいは成長条件に特段の限定を加えたりしなくとも、低転位のAlN系III族窒化物からなる厚膜層を形成することができる。

(もっと読む)

半導体の処理方法、半導体装置およびその製造方法

【課題】GaとNとを含む系半導体層の表面近くのリーク電流を低減することが可能な半導体の処理方法、半導体装置およびその製造方法を提供すること。

【解決手段】本発明は、GaN系半導体層(20)の表面にシリコンを含有する第1絶縁膜(24)を形成する工程と、GaN系半導体層(20)の表面に形成された第1絶縁膜(24)を除去する工程と、を有することを特徴とする半導体の処理方法、半導体装置およびその製造方法である。本発明によれば、GaN系半導体層の表面のGaとNの組成比を化学量論的組成比に近づけることができる。

(もっと読む)

GaN結晶の製造方法、GaN結晶基板および半導体デバイス

【課題】転位密度が低く結晶性のよいGaN結晶の製造方法、GaN結晶基板、およびそのGaN結晶基板を含む半導体デバイスを提供する。

【解決手段】GaN結晶の製造方法は、昇華法により成長させたAlN種結晶の少なくとも一部で形成されているAlN種結晶基板3を用いて、HVPE法によりGaN結晶4を成長させるGaN結晶の製造方法であって、AlN種結晶基板の反りの曲率半径が5m以上であることを特徴とする。

(もっと読む)

半導体膜の製造方法及びそれを用いた電子部品の製造方法

【課題】幅広い材料選択が可能で生産性に優れた半導体膜の製造方法を提供する。

【解決手段】膜成長用基板1の表面の一部の領域に導電体層2を形成する工程と、

膜成長用基板1の表面の一部の領域以外の領域から半導体をエピタキシャル成長させ、導電体層2を覆う半導体膜3を形成する工程と、

誘導加熱用コイル4での電磁誘導により導電体層2を発熱させることで、半導体膜3を膜成長用基板1から分離する工程とを含む、半導体膜3の製造方法。

(もっと読む)

III族窒化物半導体結晶、III族窒化物半導体基板、半導体装置およびIII族窒化物半導体結晶の製造方法

【課題】 抵抗値の高いIII族窒化物半導体結晶、III族窒化物半導体基板、半導体装置およびIII族窒化物半導体結晶の製造方法を提供すること。

【解決手段】 GaN基板1のFeドープGaN層14は、遷移金属原子であるFe原子が添加されたIII族窒化物半導体結晶であって、Ga原子空孔密度が1×1016cm−3以下である。FeドープGaN層14のFe原子の密度は、5×1017cm−3〜1020cm−3である。また、FeドープGaN層14のFe原子の密度は、FeドープGaN層14中の酸素原子およびシリコン原子の合計の密度よりも高い。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】半導体基板に汚染物質が付着することを抑えトランジスタの特性を劣化させることなく製造することができる半導体基板の製造方法及び半導体装置の製造方法を提供する。

【解決手段】半導体基板41の製造方法は、シリコン基板11上におけるSOI素子形成領域13のみに、シリコンバッファ層18及びシリコンゲルマニウム層15が成長する条件でエピタキシャル成長させる。次に、シリコン基板11上の全面にシリコン層16を成長させる。そのあと、シリコンゲルマニウム層15に代えて埋め込み絶縁層31を埋め込む。これにより、引き続く工程において、シリコン基板11上に汚染の原因であるシリコンゲルマニウム層15が残ることを少なくすることができ、処理を行う炉の中にゲルマニウムが広がることを抑えることが可能となる。

(もっと読む)

窒化物半導体成長基板及びその製造方法

【課題】ガリウム酸化物基板を用い、このガリウム酸化物基板上に窒化物半導体を成長させるのに好ましいバッファ層として、(0001)の面方位以外の面方位に形成した窒化物半導体成長基板及びその製造方法を提供する。

【解決手段】ガリウム酸化物基板と、ガリウム酸化物基板上に600℃以下の成長温度条件で、水素キャリアにより所定の面方位に形成された窒化物半導体のバッファ層とを有する窒化物半導体成長基板とする。これにより、バッファ層の上に成長させた窒化物半導体は分極が小さく、あるいは、分極なしに形成できるので、発光効率の高い発光素子を形成するのに適した窒化物半導体成長基板及びその製造方法が可能となる。

(もっと読む)

半導体エピタキシャルウェハ及びその製造方法

【課題】基板上にエピタキシャル層を成長させる際、新たな保護膜の形成や除去の工程を必要とすることなく、清浄で鏡面のオリエンテーションフラットを維持することを可能とする。

【解決手段】半導体エピタキシャルウェハは、劈開により形成されたオリエンテーションフラット2を有する基板1と、該基板1上に形成された半導体のエピタキシャル層とからなり、前記基板1のオリエンテーションフラット2の両端2aが、前記基板内側へ所定距離入った領域まで被覆部材15で覆い隠された状態で前記基板1上にエピタキシャル層が形成され、前記被覆部材15を前記基板1から取り除いた状態で前記エピタキシャル層が形成されていない未成長部が前記オリエンテーションフラット2の両端2aに存在する。

(もっと読む)

窒化物半導体ウェーハ及び窒化物半導体素子

【課題】多結晶AlN基板を用いつつ結晶性にすぐれた窒化物半導体ウェーハ及び窒化物半導体素子を提供する。

【解決手段】配向性を有する多結晶窒化アルミニウムからなり、主面上に複数のステップ10Sが形成された基板10と、前記基板の前記主面上に設けられた単結晶の窒化物半導体層25とを備えた窒化物半導体ウェーハ1及び前記窒化物半導体層25の上に設けられた電極を備えた窒化物半導体素子。

(もっと読む)

半導体ウェハの横方向に分断する方法およびオプトエレクトロニクス構成素子

半導体ウェハ(1)を横方向に分断する本発明の方法では、成長基板(2)を準備し、この成長基板(2)に半導体層列(3)をエピタキシ成長させる。ここではこの半導体層列には、分離層(4)として設けられた層と、成長の方向に見てこの分離層に続く少なくとも1つの機能半導体層(5)とが含まれている。引き続いてこの機能半導体層(5)を通して分離層(4)にイオン打ち込み、半導体層をこの分離層(4)に沿って分断し、上記の成長基板(2)を含む半導体ウェハ(1)の部分(1a)が切り離される。  (もっと読む)

(もっと読む)

半導体ウエハの横方向分断のための方法及びオプトエレクトロニクス構成素子

本発明は、成長基板(2)と半導体層列(3)を含んでいる半導体ウエハの横方向切断のための方法に関している。この方法は成長基板(2)を設けるステップと、前記成長基板(2)において機能性半導体層(5)を含んだ半導体層列(3)をエピタキシャル成長させるステップと、マスキング領域(11)と非マスキング領域(12)の作成のために前記半導体層列(3)の部分領域にマスク層(10)を被着させるステップと、半導体ウエハ(1)におけるイオン打込み領域(13)作成のために非マスキング領域(12)を通してイオンを打ち込むステップと、前記イオン打込み領域(13)に沿って半導体ウエハ(1)を切断するステップとを有し、前記成長基板(2)又は少なくともその一部が半導体ウエハから分離されるようにしたことを特徴とする。  (もっと読む)

(もっと読む)

III族窒化物の単結晶作製方法およびIII族窒化物単結晶層を含む積層体

【課題】簡便な方法によってAlNを含むAlN系III族窒化物の自立した状態の単結晶を作製する方法を提供する。

【解決手段】サファイア基材1の上にAlNの成長下地層2を形成した下地基板3の上に、第1中間層4を形成したうえで、さらにAlN単結晶層7をHVPE法によって形成し、積層体10を得る。ここで、第1中間層4は単結晶層7よりも分解温度の低い物質、好ましくはAlGaNなどのIII族窒化物により形成される。この積層体10を第1中間層4の分解温度よりも高く単結晶層7の分解温度よりも低い温度、例えば1650℃に加熱すると、第1中間層4が分解消失し、主としてAlN単結晶層7の部分からなる自立した状態のAlN系III族窒化物単結晶7aを得ることが出来る。

(もっと読む)

III族窒化物結晶の形成方法、積層体、およびエピタキシャル基板

【課題】従来よりも結晶品質の優れたIII族窒化物結晶およびその形成方法を提供する。

【解決手段】所定の基材に第1のIII族窒化物結晶を成長下地層2としてエピタキシャル形成してなる下地基板に対して、1250℃以上の所定の温度で熱処理を行う。これにより、成長下地層2の表面には、島状結晶2Iによる三次元的な微細な凹凸形状が形成される。係る下地基板の上に、結晶層4として、第2のIII族窒化物をエピタキシャル形成する。結晶層4と下地基板3との界面には多数の微細な空隙5を介在することになるが、該空隙5の存在により、下地基板3からの転位の伝搬が抑制されるので、結晶層4の転位密度は低下する。結果的に、良好な結晶品質の結晶層4を得ることが出来る。

(もっと読む)

加工基板上へのシリコンCMOS及びAlGaN/GaN広帯域増幅器を集積する新規方法

高速シリコンCMOS回路及び高電力AlGaN/GaN増幅器が、同じウェハー上に集積される。高抵抗シリコンの薄層が、基板上に結合される。ボンディングに続いて、AlGaN/GaN構造を結合したシリコン層上に成長させる。次いで、窒化シリコン又は酸化シリコン層をAlGaN/GaN構造上に堆積させる。これに続いて、シリコンの薄層を窒化シリコン/酸化シリコン層に結合させる。AlGaN/GaN装置の形成領域が規定され、シリコンがこれらの領域から離れてエッチングされる。これに続いて、CMOS装置がシリコン層上に形成され、AlGaN/GaN装置がAlGaN/GaN表面上に形成される。 (もっと読む)

光電子応用のための(Al,Ga,In)NとZnOの直接ウェーハ・ボンディング構造とその作製方法

光が導電性のあるZnOを通過し、(Al,Ga,In)NとZnOが直接ウェーハ・ボンディングされた発光ダイオード(LED)を提供する。(Al,Ga,In)NとZnOのウェーハの両方に平坦で清潔な表面を準備する。次に(Al,Ga,In)NとZnOウェーハの間でウェーハ・ボンディング工程を行うが、これは(Al,Ga,In)NとZnOウェーハを互いに張り合わせて、そこで窒素雰囲気中で一軸性圧力の下、設定温度で設定された時間ウェーハ・ボンディングを行う。ウェーハ・ボンディング工程の後、ZnOはLEDの内部から光取り出し量を増加させるために整形される。  (もっと読む)

(もっと読む)

電力用途へのウェハーボンディングを介して得られた多層基板

多層半導体装置は、ウェハーボンディングを介して移行させた単結晶膜の電気的特性を有する多結晶基板の良好な熱的及び電気的特性を利用している。装置構造は、研磨された多結晶、例えば炭化シリコン基板を含む。シリコンの平坦化層が表面に形成され、続いて化学的機械研磨される。次いで、基板は、バルクリシコンウェハー又はsilicon-on-insulator(SOI)ウェハーに結合される。シリコン(SOI)ウェハーは所望厚さに薄肉化される。 (もっと読む)

化合物半導体基板、エピタキシャル基板、化合物半導体基板の製造方法及びエピタキシャル基板の製造方法

【課題】 表面において所望の電気的特性を有する化合物半導体基板、エピタキシャル基板、化合物半導体基板の製造方法及びエピタキシャル基板の製造方法を提供する。

【解決手段】 化合物半導体基板10は、p型の化合物半導体からなる基板12と、基板12の表面12aに結合しておりp型の不純物原子を含む物質14とを備える。

(もっと読む)

III族窒化物結晶の表面平坦性改善方法、エピタキシャル成長用基板、および半導体素子

【課題】作製条件に特段の制限を設けることなく、III族窒化物結晶における表面平坦性の向上を実現する方法を提供する。

【解決手段】単結晶の基材1とその主面上にエピタキシャル形成されたIII族窒化物結晶膜からなる上部層2とで構成されたエピタキシャル基板10を、窒素雰囲気下で1250℃以上の温度で加熱処理する。

【効果】表面におけるピットが低減することにより表面平坦性が改善し、また、III族窒化物結晶内の転位密度が熱処理前の1/2以下となる。

(もっと読む)

121 - 140 / 171

[ Back to top ]