Fターム[5F152NP05]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 半導体 (836) | 3−5族 (413)

Fターム[5F152NP05]の下位に属するFターム

Fターム[5F152NP05]に分類される特許

61 - 76 / 76

格子整合されなかった基板上に応力緩和層構造を形成する方法及び電子素子及び/又は光導電素子内でのこのような層組織の使用

【課題】

本発明は、その都度異なる格子構造を有する基板上に1つ又は多数の層を有する単結晶応力緩和層構造を形成する方法に関する。特殊な構造では、この方法は、好ましくは応力緩和したSi−Ge層構造上にひずみシリコンを形成するために使用される。さらに本発明は、このような層組織を、例えばMOSFET,MODFET,共振トンネルダイオード,フォト検出器や量子カスケード・レーザのような素子で使用することに関する。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 SOI基板を用いることなく、絶縁体上に形成される半導体層の面積を拡大する。

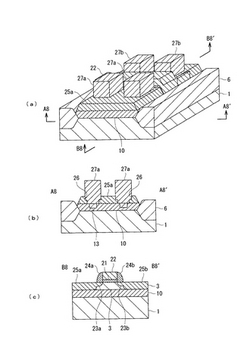

【解決手段】 開口部7を介して空洞部9内の半導体基板1および第2半導体層3の熱酸化を行うことにより、半導体基板1と第2半導体層3との間の空洞部9に埋め込み絶縁膜10を形成した後、ソース/ドレイン層25a、25bの表面に露出している埋め込み絶縁膜10、13および第2半導体層3をパターニングすることにより、開口部7の周囲のソース/ドレイン層25a、25bの側壁を露出させるコンタクトホール26を形成し、コンタクトホール26を介してソース/ドレイン層25a、25bにそれぞれ接続された配線層27a、27bを形成する。

(もっと読む)

半導体基板及び半導体装置並びにそれらの製造方法

【課題】多孔質層或いは多孔質領域上に良質の半導体層を形成することを目的とする。

【解決手段】半導体基板の製造方法は、第1材料で構成される基板11上に、基板11の格子定数と異なる格子定数を有する第2材料からなる層を含む第1半導体層12を形成する工程と、少なくも第1半導体層11の表面を多孔質化して多孔質層12”を形成する工程と、多孔質層12”上に第1材料で構成される第2半導体層14を形成する工程とを含む。

(もっと読む)

構造均一性を有する半導体構造

組成変動を有する半導体層を備えている半導体構造を形成する。この半導体層の最上表面は、実質的にヘイズを有していない。  (もっと読む)

(もっと読む)

半導体ウェハ

【課題】GaAs基板からの能動層への転位の伝播を抑止する半導体結晶基板の構造を提供すること。

【解決手段】GaAs基板1と能動層40との間に、平面内にInAs核をドット状(島状)に形成し、その上にInAs核が埋まる程度にIII−V族化合物半導体のバッファ層20を成長した構造を設ける。

(もっと読む)

溶融層を用いた歪み層の歪み緩和

界面層が支持基板に結合された結晶ウェハの製造方法。第1の層が、歪み状態で界面層に結合される。界面層は、第1の層の歪みを緩和して歪み状態から歪み緩和状態にするために、第1の層を支持基板から実質的に引き離すのに十分な程度に溶融される。界面材料は、第1のウェハを獲得するために、歪み緩和状態にある第1の層とともに固化される。 (もっと読む)

薄層を除去した後の多層構造を備えるウェハのリサイクル

半導体材料から選ばれた材料を含む有用層を除去した後にドナーウェハ(10)をリサイクル方法であって、ドナーウェハ(10)は基板(1)と多層構造(I)とを順次に備え、除去前の多層構造(I)は除去すべき有用層を備え、そのプロセスは除去が行われた側での物質除去を含み、物質除去の後に多層構造(I’)の少なくとも部分が残り、このバッファ構造(I’)の少なくとも部分は除去することができる別の有用層を1つ以上含み、有用層を再形成する補足的段階をともなわないことを特徴とする。本書はまた:本発明による少なくとも1つのリサイクル可能ドナーウェハ(10)から薄層を除去する方法、本発明によるリサイクル可能ドナーウェハ(10)に関する。  (もっと読む)

(もっと読む)

内部ゲッタリングされたヘテロエピタキシャル半導体ウエハ及びその製造方法

【課題】 SOIウエハ及びそのウエハの製造方法の提供。

【解決手段】 SOIウエハは、前方表面及び後方表面、前記前方表面と後方表面との間の中央平面、及び前記前方表面と後方表面とを連絡する周囲縁部を有してなり、第1の材料を含んでなるヘテロエピタキシャル半導体ウエハであって、該ウエハの前方表面を形成し、前記第1の材料の結晶構造と異なる結晶構造を有する第2の材料を含むヘテロエピタキシャル層;前記第1の材料を含み、前記第2の材料を含まず、前記ヘテロエピタキシャル層に隣接する表面層;並びに前記第1の材料を含み、前記第2の材料を含まず、前記表面層に隣接して、中央平面を通って延びるバルク層を有してなるヘテロエピタキシャル半導体ウエハである。

(もっと読む)

除去構造を含んでなるウェハーの、その薄層を除去した後の、機械的手段による循環使用

除去構造を含んでなるウェハーの、その薄層を除去した後の、機械的手段による循環使用。半導体材料から選択された材料を含んでなる有用な層を除去した後、ドナーウェハー(10)を循環使用する方法。ドナーウェハー(10)は、順に、基材(1)および除去構造(I)を含んでなり、該除去構造(I)は、除去前は、除去すべき有用な層を含んでなり、本方法は、除去が行われる側にある物質を除去することを含んでなり、物質の除去が、物質を除去した後、除去構造の少なくとも一部(I’)が残り、この除去構造の少なくとも一部(I’)が、少なくとも一個の他の有用な層(該層は、有用な層を再形成する補充工程無しに、循環使用の後に除去できる)を包含するように、機械的手段を使用することを含んでなることを特徴とする。本願は、同様に、本発明により循環使用できるドナーウェハー(10)から薄層を除去する方法、および本発明により循環使用できるドナーウェハー(10)にも関する。  (もっと読む)

(もっと読む)

半導体素子のための支持構造体を作製する方法

半導体素子を作製する方法を記述する。この方法において、所望の欠陥密度レベル(好ましくないドーピングレベルに終わる)を有し、充分な厚さを有する出発基板を選択する。その後、出発基板上に、所望のドーピングレベルを有する半導体層を形成する。生じた半導体層は、最終製品用途に関する所望の欠陥密度及びドーピングレベルを有する。動的素子と、導電体と、他の所要の構造体とを半導体層上に形成した後、出発基板を取り除き、所望厚の半導体層を残す。VECSEL用途において、動的素子はゲインキャビティーであることができ、この半導体層は、ウォールプラグ効率(WPE)を最大化するのに、必要な欠陥密度及びドーピングレベルを有する。態様のひとつでは、半導体層のドーピングは均一でない。例えば、層の大部分を低レベルでドープし、そして残りの部分をさらに高いレベルでドープする。より多くドープ化した材料の場合、これによって、特定の厚さにおいて、改良されたWPEがもたらされる。  (もっと読む)

(もっと読む)

CMOSプロセス中に歪み半導基板層を保護する方法

Si/SiGeヘテロ構造をベースとしたウェハで不都合な表面材料の多量の消費を回避する酸化方法を、様々な中間CMOS熱酸化ステップに代えて行う。まず、酸化物堆積法を利用して、表面シリコンをほとんどまたは全く消費することなく、任意の厚さの酸化物を形成する。このような酸化物、例えばスクリーン酸化物およびパッド酸化物は、表面層との反応および表面層の消費によってではなく、表面層への堆積によって形成される。別の態様では、酸化物の堆積は、短時間の熱酸化ステップ、例えば急速熱酸化によって行われる。この場合、熱酸化が短時間であるために、表面Siはほとんど消費されず、Si/酸化物境界面は高い品質を有する。次に、堆積によって、この酸化物の厚みを所望の最終厚さにまで増大させる。さらに、この薄い熱酸化物層は、バリヤ層として働くことができ、これにより、後続の酸化物堆積と関連する汚染を防ぐことができる。  (もっと読む)

(もっと読む)

格子調整半導体基板の作製

格子調整半導体基板を形成する方法が、転位が優先的に形成されるストライプ領域(16)を、シリコン基板(10)の表面上に形成する工程と、ストライプ上に第1SiGe層(18)を成長させ、ストライプ領域の間の第1SiGe層を横切って第1転位(20)を優先的に延ばし、ストライプ(16)に直交する方向の、第1SiGe層中の歪を緩和する工程と、第1SiGe層の上に第2SiGe層を成長させ、第2SiGe層中に第2転位(22)を優先的に形成し、第1転位(20)に直交する方向に第2SiGe層中の歪を緩和する工程とを含む。そのように形成された転位は、2つの互いに直交した方向に材料を緩和し、一方、2組の転位は相互作用しないように間隔をおいて配置されている。これにより、貫通転位の密度と、表面粗さが大幅に低減され、能動デバイス中で電子を散乱し電子の移動速度を低減する原子格子の崩壊を減らすことにより、仮想基板の特性を向上させる。  (もっと読む)

(もっと読む)

半導体エピタキシャル基板

【目的】エピタキシャル成長面の凹凸が小さく、良好な特性を有し、生産性に優れた半導体エピタキシャル基板を提供する。

【構成】基板の結晶学的面方位が、1つの{100}面の結晶学的面方位から傾いており、その傾きの大きさが0.05°以上0.6°以下である単結晶砒化ガリウム基板上にエピタキシャル成長により結晶が形成されており、エピタキシャル結晶の少なくとも一部がInx Ga(1-x) As結晶(ただし0<x<1)であり、かつエピタキシャル成長が熱分解気相成長方法によって行われることを特徴とする半導体エピタキシャル基板。

(もっと読む)

半導体基板及びその製造方法

【課題】ヘテロエピタキシャル成長膜の、応力の緩和と、緩和に伴って発生し表面へ貫通する結晶欠陥の密度の抑制を両立させるために要求される、膜厚に対する制限を低減し、プロセス設計の自由度を向上させる。

【解決手段】半導体基板の製造方法は、第1単結晶半導体10の上に第2単結晶半導体12を成長させる成長工程と、第2単結晶半導体12に阻止層12aを形成する阻止層形成工程と、阻止層12aよりも深い部分に結晶欠陥15を発生させて第2単結晶半導体12に作用する応力を緩和する緩和工程とを含む。阻止層12aは、例えば多孔質層で構成され、阻止層12aよりも深い部分の結晶欠陥が第2単結晶半導体12の表面に伝播することを防止する。

(もっと読む)

絶縁構造部上の半導体チャンネル

半導体装置基板上に貫通誘電体層を形成するステップと、貫通誘電体層の上部にトレンチ誘電体層を形成するステップと、貫通誘電体層を露出させるため、トレンチ誘電体層を貫通する溝を形成するステップと、基板を露出させるため、前記溝内の貫通誘電体層に貫通孔を形成するステップと、溝内および前記貫通孔内に半導体材料を形成するステップと、を有する方法を示した。装置基板と、該装置基板の表面に形成された誘電体層と、誘電体層上に形成された、装置基板と相間する結晶構造を有する装置基部と、を有する装置を示した。  (もっと読む)

(もっと読む)

エピタキシャル基板の製造方法

本発明は、エピタキシャル基板、例えば、GaN,SiGe,AlNまたはInNのエピタキシャル基板の製造方法、およびエピタキシャル基板上またはその中に作製された電子デバイスに関する。本発明の目的は、基板の影響を更に軽減することが可能であると同時に経済的に実行可能な、エピタキシャル基板の製造方法を提供することである。この目的は、以下のように達成することが出来る。すなわち、結晶性基板を用意し、原子種を基板に注入して脆性層を作成し、第1の温度で、基板の表面にエピタキシャル補強層を設け、第2の温度範囲で補強層を基板の副層とともに基板の残部から分離させて、これによって、この分離した材料によって、その上にホモエピタキシャル層またはヘテロエピタキシャル層の形成する擬似基板が作成される。 (もっと読む)

61 - 76 / 76

[ Back to top ]