Fターム[5F152NP06]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 半導体 (836) | 3−5族 (413) | GaAs (56)

Fターム[5F152NP06]に分類される特許

1 - 20 / 56

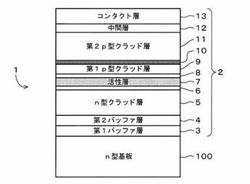

発光素子用エピタキシャルウェハ及び発光素子

【課題】1枚のウェハからより多くのチップを取得することができる高性能な発光素子用エピタキシャルウェハを提供する。

【解決手段】加熱したn型基板100上にIII族原料ガス及びV族原料ガスを供給し、n型基板100上に少なくともn型クラッド層5、活性層7、p型クラッド層9,11及びコンタクト層13からなるIII−V族半導体層2を積層する発光素子用エピタキシャルウェハ1において、III−V族半導体層2のいずれかの層に不可避不純物として混入するS(硫黄)の濃度を1.0×1015cm-3以下にすべく、その層の成長時の基板温度を620℃以上とし、かつV族原料ガスとIII族原料ガスの実流量比を130以上とした。

(もっと読む)

半導体基板上での逆相境界の無いIII−V化合物半導体材料およびその製造方法

【課題】逆相境界(APB)の無いIII−V化合物半導体材料およびその製造方法を提供する。

【解決手段】III−V化合物半導体材料の製造方法は、a){001}配向を有する第1半導体材料からなる基板と、基板の上に位置し、これと接触する絶縁層と、絶縁層内に、少なくとも部分的に基板を露出させる凹部領域を用意する工程と、b)凹部領域において露出基板の上に位置し、これと接触するバッファ層を形成する工程工程と、c)バッファ層の表面を粗面化するために、熱処理を印加する工程とを含み、バッファ層が、熱処理の印加後に二重ステップ表面を有する丸み形状をなし、d)凹部領域を、バッファ層の二重ステップ表面の上に位置し、これと接触するIII−V化合物半導体材料で少なくとも部分的に充填する工程をさらに含む。

(もっと読む)

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】中間層としてGe結晶を用いる場合の化合物半導体へのGe原子の混入を抑制する。

【解決手段】ベース基板と、ベース基板上に形成された第1結晶層と、第1結晶層を被覆する第2結晶層と、第2結晶層に接して形成された第3結晶層とを備え、第1結晶層が、ベース基板における第1結晶層と接する面と面方位が等しい第1結晶面、及び、第1結晶面と異なる面方位を有する第2結晶面を有し、第2結晶層が、第1結晶面と面方位が等しい第3結晶面、及び、第2結晶面と面方位が等しい第4結晶面を有し、第3結晶層が、第3結晶面及び第4結晶面のそれぞれの少なくとも一部に接しており、第1結晶面に接する領域における第2結晶層の厚みに対する第2結晶面に接する領域における第2結晶層の厚みの比が、第3結晶面に接する領域における第3結晶層の厚みに対する第4結晶面に接する領域における第3結晶層の厚みの比よりも大きい半導体基板を提供する。

(もっと読む)

半導体基板及び半導体基板の製造方法

【課題】半導体基板のアライメントマークを繰り返し使用する。

【解決手段】ベース基板にアライメントマークを形成する段階と、アライメントマークを形成する段階の後に、ベース基板上のアライメントマークを含む領域に、結晶成長を阻害する阻害層を形成する段階と、アライメントマークの位置を基準とする開口を形成すべき位置を示す情報に基づいて、阻害層におけるアライメントマークが設けられていない領域に、ベース基板を露出する開口を形成する段階と、開口内に半導体結晶を成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

歪み補償半導体構造および歪み補償半導体構造を製作する方法

【課題】歪みの程度がGaNの割れの閾値を上回るならば、GaNが割れ、GaNの半導体デバイスへの使用を受容できないものにする可能性がある。

【解決手段】この半導体構造は、第1の面内無歪み格子定数を有する基板と、基板上に設けられ、第1の面内無歪み格子定数とは異なる第2の面内無歪み格子定数を有する、第1の半導体材料を含む第1の層と、基板と第1の層の間に配置され、第2の半導体材料を含む可変不整合層とを含む半導体構造、およびこの半導体構造の製作方法が提供される。可変不整合層は、第1の層を基板上に直接成長させる場合に生じる応力を下回る程度にまで第1の層の応力が低減されるように構成される。可変不整合層は、第1の層の無歪み格子定数と実質的に整合する面内歪み格子定数を有する層であってもよい。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】 p型不純物が隣接する半導体結晶層中へ拡散することを抑え、ひいては良好で安定した特性を持つ半導体装置を提供する。

【解決手段】 P−InP基板401と、P−InP基板401に格子整合し、かつ、p型の不純物が注入されたp−ZnドープInPバッファ層402と、p−ZnドープInPバッファ層402よりも上層にあって、P−InP基板401に格子整合し、かつ、p型不純物、n型不純物のいずれか一方を含むn−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405と、を備え、n−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405に、Sbを含ませる。

(もっと読む)

半導体基板の製造方法

【課題】選択エッチング層のエッチング時の自然酸化による影響で化合物半導体層の損傷、結晶の転移が発生せず、信頼性の高い半導体基板の製造方法を提供する。

【解決手段】化合物半導体基板8上に、選択エッチング層3、応力緩和層9および応力緩和層9より大きいヤング率を有するIII−V族化合物半導体から成る化合物半導体層4をエピタキシャル成長法により順次積層させる積層工程と、選択エッチング層3、応力緩和層9および化合物半導体層4を所定パターンとなるようにエッチング除去するエッチング工程と、Si基板5の主面に化合物半導体層4の上面を直接接合法により接合させて、選択エッチング層3、応力緩和層9および化合物半導体層4が積層された化合物半導体基板8を貼りあわせる接合工程と、前記エッチング工程で残った選択エッチング層3をさらにエッチング除去することにより、Si基板5と化合物半導体基板8とを分離する分離工程とを含む。

(もっと読む)

光デバイス、半導体基板、光デバイスの製造方法、および半導体基板の製造方法

【課題】高品質な光デバイスをシリコン基板上にモノリシックに形成する。

【解決手段】シリコンを含むベース基板と、ベース基板上に設けられた複数のシード結晶と、複数のシード結晶に格子整合または擬格子整合する複数の3−5族化合物半導体とを備え、複数の3−5族化合物半導体のうちの少なくとも1つに、供給される駆動電流に応じて光を出力する発光半導体、または光の照射を受けて光電流を発生する受光半導体を含む光電半導体が形成されており、複数の3−5族化合物半導体のうち、光電半導体を有する3−5族化合物半導体以外の少なくとも1つの3−5族化合物半導体にヘテロ接合トランジスタが形成されている光デバイスを提供する。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】単一半導体基板上にHBTおよびFETのような複数異なる種類のデバイスを形成するに適した半導体基板を製造する方法を提供する。

【解決手段】半導体を結晶成長させる反応容器内に第1不純物原子を構成要素として有する単体または化合物を含む第1不純物ガスを導入する段階を含む複数の段階を繰り返して、複数の半導体基板を製造する方法であって、第1不純物ガスを導入する段階の後に、製造された半導体基板を取り出す段階と、反応容器内に第1半導体を設置する段階と、反応容器内に、第1半導体内で第1不純物原子と反対の伝導型を示す第2不純物原子を構成要素として有する単体または化合物を含む第2不純物ガスを導入する段階と、第1半導体を第2不純物ガスの雰囲気中で加熱する段階と、加熱した前記第1半導体上に第2半導体を結晶成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置

【課題】低コストの立方晶炭化ケイ素(3C−SiC)単結晶薄膜を得るための立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置を提供する。

【解決手段】立方晶炭化ケイ素単結晶薄膜の製造方法において、基板101の表面に犠牲層102を形成する第1の工程と、犠牲層の表面に少なくとも表面層が立方晶構造である立方晶半導体層103を形成する第2の工程と、立方晶半導体層の表面に立方晶炭化ケイ素単結晶層104を形成する第3の工程と、犠牲層をエッチング除去して、立方晶半導体層と立方晶炭化ケイ素単結晶層との積層体を剥離する第4の工程とを備える。

(もっと読む)

発光サイリスタ、発光素子アレイ、発光装置および画像形成装置

【課題】 ベース層のキャリア濃度および厚み寸法を大きく設定することなく、発光強度に対する電流増幅率βの影響を抑制することのできる発光サイリスタ、発光素子アレイ、発光装置および画像形成装置を提供することである。

【解決手段】 発光サイリスタは、基板上に第1半導体層、第1半導体層と反対導電型の第2半導体層、第1半導体層と同じ導電型の第3半導体層、および第1半導体層と反対導電型の第4半導体層がこの順に積層されており、第3半導体層のバンドギャップは、第2半導体層のバンドギャップと略同一、かつ、第1および第4半導体層のバンドギャップより狭幅であり、第3半導体層は、基板側の第1領域と基板と反対側の第2領域とからなり、かつ、第1領域の不純物濃度は1×1016(cm−3)未満である。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層とをこの順に有する半導体基板であって、SixGe1−x結晶層上に設けられる阻害層と、SixGe1−x結晶層に格子整合または擬格子整合している化合物半導体とを備え、阻害層はSixGe1−x結晶層にまで貫通する開口を有し、かつ化合物半導体の結晶成長を阻害する半導体基板を提供する。また、上記開口の内部でSixGe1−x結晶層に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に化合物半導体の結晶成長を阻害する阻害層が設けられ、阻害層はSi結晶層にまで貫通する開口を有し、開口の内部にシード結晶を備え、化合物半導体はシード結晶に格子整合または擬格子整合している半導体基板を提供する。サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられ化合物半導体の結晶成長を阻害する阻害層であって、Si結晶層にまで貫通する開口を有する阻害層と、開口の内部に設けられたシード結晶と、シード結晶に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体デバイス用基板、半導体デバイス装置、設計システム、製造方法、および設計方法

【課題】結晶薄膜の膜質および膜厚を均一にする。

【解決手段】半導体デバイスを形成するためのデバイス用薄膜と、デバイス用薄膜を囲み、デバイス用薄膜の前駆体が結晶に成長することを阻害する阻害部と、前駆体が結晶に犠牲成長することによって形成された犠牲成長部であって、デバイス用薄膜の周辺に阻害部で隔てられて設けられた犠牲成長部と、犠牲成長部の上部を覆い、かつデバイス用薄膜の上部を露出する保護膜を備えた。保護膜はポリイミドであってもよい。

(もっと読む)

ウェーハおよびウェーハの製造方法

【課題】異なる格子の基板上に成長した良質なエピタキシャル層を備えたウェーハおよびウェーハ製造方法の提供。

【解決手段】単結晶の第1の材料の基板はオンアクシスシリコン基板であり、オンアクシスシリコン基板上に第2の材料を成長させるウェーハの製造方法に関し、第2の材料が、第1の材料上にエピタキシャル成長し、第1の材料の格子とは異なる格子を持っている。オンアクシスシリコン基板を研磨ステップ104で研磨して、ウェーハ表面粗さを増大させる。SiGe層である傾斜バッファ層及び緩和層をウェーハ上に形成した後、CMP最終研磨108を実施する。上述のタイプの方法により解決され、基板の最終表面仕上げの前に第2の材料の成長を実施する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上する。

【解決手段】シリコン基板と、シリコン基板の上に形成された絶縁膜であってシリコン基板に達する開口部を有する絶縁膜と、開口部に形成されたGe結晶と、Ge結晶を核として成長された化合物半導体結晶であって絶縁膜の表面より凸に形成されたシード化合物半導体結晶と、シード化合物半導体結晶の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層と、を備えた半導体基板を提供する。

(もっと読む)

エピタキシャル成長のための基板の作成方法

【課題】本発明は、補助基板上に緩和エピタキシャルベース層を得ることを含む、エピタキシャル成長のための基板の作製方法に関する。本発明の目的は、望ましい格子パラメータを有する材料が、異なる格子パラメータを有する別の材料の上で、より効率的に、熱力学的及び結晶学的に高い安定性を有してエピタキシャル成長することを可能にする基板を作ることにある。

【解決手段】この目的は、上記のタイプの方法であって、エピタキシャルベース層の少なくとも一部をキャリア基板上に移してベース基板を形成することと;エピタキシャルベース層の材料をキャリア基板上でさらに成長させることとをさらに含む方法により達成される。

(もっと読む)

多層膜構造体およびその形成方法

【課題】半導体素子用の多層膜構造体を基板上に形成する多層膜構造体であって、大きな伸張歪を半導体層に印加できる多層膜構造体の形成方法を提供する。

【解決手段】半導体素子用の多層膜構造体10を基板上に形成する際に、基板11上に、当該基板11を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、圧縮歪を有する圧縮歪半導体層12を形成する。その圧縮歪半導体層12の上方に、圧縮歪半導体層12を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、無歪の無歪半導体層13を積層する。圧縮歪半導体層12の圧縮歪を緩和させることにより、無歪半導体層13に伸張歪を印加する。それにより、大きな伸張歪を無歪半導体層13に印加することができる。

(もっと読む)

1 - 20 / 56

[ Back to top ]