Fターム[5F152NP05]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 半導体 (836) | 3−5族 (413)

Fターム[5F152NP05]の下位に属するFターム

Fターム[5F152NP05]に分類される特許

21 - 40 / 76

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に化合物半導体の結晶成長を阻害する阻害層が設けられ、阻害層はSi結晶層にまで貫通する開口を有し、開口の内部にシード結晶を備え、化合物半導体はシード結晶に格子整合または擬格子整合している半導体基板を提供する。サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられ化合物半導体の結晶成長を阻害する阻害層であって、Si結晶層にまで貫通する開口を有する阻害層と、開口の内部に設けられたシード結晶と、シード結晶に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】基板と当該基板に形成される化合物半導体とを電気的に絶縁しつつ、結晶性に優れた化合物半導体を備えた半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に設けられたシード結晶と、シード結晶の上方に設けられた化合物半導体と、シード結晶と化合物半導体との間に設けられ、シード結晶よりも大きな抵抗率を有する高抵抗層とを備え、シード結晶と化合物半導体とが格子整合または擬格子整合している半導体基板を提供する。

(もっと読む)

磁性半導体素子

【課題】基板と格子整合し、キュリー温度Tcが室温であるII−IV−V2族化合物磁性半導体材料で量子井戸層あるいは強磁性電極を構成した磁性半導体素子を提供する。

【解決手段】

磁性半導体素子10は、InPからなる基板11と、Mnが添加されたZnSnAs2からなりかつ基板11の上に結晶成長された量子井戸層13と、InAlAs及び/又はInGaAsからなり基板11の上に結晶成長されかつ量子井戸層13を挟持する一組の障壁層12,14と、を備える。障壁層12,14にInAlAsを採用した場合、Al組成は0.43〜0.53%であることが好ましくは、InGaAsを採用した場合、Ga組成が0.42〜0.52%であることが好ましい。

(もっと読む)

低減した格子ひずみを備えた半導体材料、同様に包含する半導体構造体、デバイス、および、加工された基板を製造する方法

半導体装置を製作する方法または構造体は、従順な材料の層の上に横たわっている半導体材料の構造体を形成することを含み、その後半導体材料構造体を緩和させる従順な材料の粘性を変えて、緩和した半導体材料の連続層を形成する際の種子層として、緩和した半導体材料構造体を利用する。ある実施形態では、半導体材料の層は、III-Vタイプ半導体材料(例えばインジウム窒化ガリウム)から成る。新しい中間構造体が、この種の方法の間、形成される。加工された基板は、緩和した格子の構造体を有する半導体材料の連続層を含む。  (もっと読む)

(もっと読む)

半導体デバイス用基板、半導体デバイス装置、設計システム、製造方法、および設計方法

【課題】結晶薄膜の膜質および膜厚を均一にする。

【解決手段】半導体デバイスを形成するためのデバイス用薄膜と、デバイス用薄膜を囲み、デバイス用薄膜の前駆体が結晶に成長することを阻害する阻害部と、前駆体が結晶に犠牲成長することによって形成された犠牲成長部であって、デバイス用薄膜の周辺に阻害部で隔てられて設けられた犠牲成長部と、犠牲成長部の上部を覆い、かつデバイス用薄膜の上部を露出する保護膜を備えた。保護膜はポリイミドであってもよい。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上する。

【解決手段】シリコン基板と、シリコン基板の上に形成された絶縁膜であってシリコン基板に達する開口部を有する絶縁膜と、開口部に形成されたGe結晶と、Ge結晶を核として成長された化合物半導体結晶であって絶縁膜の表面より凸に形成されたシード化合物半導体結晶と、シード化合物半導体結晶の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層と、を備えた半導体基板を提供する。

(もっと読む)

グレーデッドエピタキシャル成長を用いた半導体品の製造プロセス

【課題】緩和III−V族またはII−VI族マテリアルオンインシュレータの製造方法の提供。

【解決手段】緩和Si1−yGey層104を有する半導体構造の形成プロセスは、第1の基板上へのグレーデッドSi1−xGexバッファ層102の堆積であって、前記Ge濃度xはゼロから値yまで増加するものである堆積、緩和Si1−yGey層104の堆積、前記緩和Si1−yGey層104中にイオンを導入して第1のヘテロ構造を規定、前記第1のヘテロ構造を第2の基板108に接合して第2のヘテロ構造を規定、および前記導入されたイオンの領域での前記第2のヘテロ構造の分割であって、前記緩和Si1−yGey層104の表層部分は前記第2の基板上108に残るものである分割を含む。

(もっと読む)

シリコン上にバッファ層構造を形成する方法および当該方法により形成された構造

【解決手段】 微小電子デバイスを形成する方法および対応する構造を記載する。当該方法は、基板にGaSb核生成層を形成する段階と、GaSb核生成層にGa(Al)AsSbバッファ層を形成する段階と、Ga(Al)AsSbバッファ層にIn0.52Al0.48As下側バリア層を形成する段階と、In0.52Al0.48As下側バリア層にInxAl1−xAsグレーデッド層を形成する段階とを備えるとしてよい。当該方法によれば、欠陥の少ない、勾配をつけたInGaAsベースの量子井戸構造を有するデバイスを製造することができる。 (もっと読む)

エピタキシャル成長のための基板の作成方法

【課題】本発明は、補助基板上に緩和エピタキシャルベース層を得ることを含む、エピタキシャル成長のための基板の作製方法に関する。本発明の目的は、望ましい格子パラメータを有する材料が、異なる格子パラメータを有する別の材料の上で、より効率的に、熱力学的及び結晶学的に高い安定性を有してエピタキシャル成長することを可能にする基板を作ることにある。

【解決手段】この目的は、上記のタイプの方法であって、エピタキシャルベース層の少なくとも一部をキャリア基板上に移してベース基板を形成することと;エピタキシャルベース層の材料をキャリア基板上でさらに成長させることとをさらに含む方法により達成される。

(もっと読む)

半導体基板

【課題】従来に比べ極めて薄いバッファ層を用いて、工業的に安定でかつ低コストで、基板と格子定数の異なる良質の薄膜を形成した半導体基板を提供すること。

【解決手段】基板1は、格子定数xを有するものである。第1の半導体層2は、基板1上に形成され、格子定数yを有し、少なくともSbを含んでいる。第2の半導体層3は、第1の半導体層2上に形成され、格子定数yからzまで格子定数を段階的又は連続的に変化させものである。第3の半導体層4は、第2の半導体層3上に形成され、格子定数zを有するものある。これらの格子定数の関係は、x<z<yの関係を有している。基板1上に格子定数の異なる薄膜を形成する際に、まずSbを含む半導体を形成し、その上層に格子定数を変化させるためのバッファ層を形成することで、従来に比べ薄いバッファ層で結晶欠陥のない薄膜形成が可能となる。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上する。

【解決手段】シリコン基板と、シリコン基板の上に形成された絶縁膜であってシリコン基板に達する開口部を有する絶縁膜と、開口部に形成されたGe結晶と、Ge結晶を核として成長された化合物半導体結晶であって絶縁膜の表面より凸に形成されたシード化合物半導体結晶と、シード化合物半導体結晶の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層と、を備えた半導体基板を提供する。

(もっと読む)

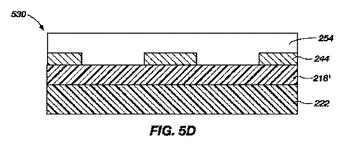

回折格子埋め込み型半導体の製作方法

半導体レーザー構造に回折格子プロファイルを形成する方法は、ウエハ基板、前記ウエハ基板上に配置されるエッチストップ層、前記エッチストップ層上に配置される回折格子層、前記回折格子層上に配置されるエッチングマスク層、および前記エッチングマスク層上に配置されるフォトレジスト層を備えた半導体ウエハを提供し、フォトレジスト回折格子パターンを形成し、乾式エッチングを通じて前記フォトレジスト回折格子パターンを前記回折格子層内に移し、前記フォトレジスト層を除去し、前記回折格子層を選択的にウェットエッチングして前記回折格子層に前記回折格子プロファイルを形成する、各工程を有してなる。前記エッチングマスクとエッチストップ層との間に前記回折格子層を配置することによって、前記選択的ウェットエッチング工程を調節する。本方法はまた、前記回折格子プロファイルを変更することなく選択的ウェットエッチングを通じて前記エッチングマスク層を除去し、上部クラッド層を再生して前記半導体レーザー構造を生産する工程も有してなる。  (もっと読む)

(もっと読む)

III−V族化合物半導体層の製造方法、半導体光素子の製造方法、および半導体光素子

【課題】N原子を含むIII−V族化合物半導体層の結晶性をより向上させ得るIII−V族化合物半導体層の製造方法、半導体光素子の製造方法、および半導体光素子を提供する。

【解決手段】N原子を含むIII−V族化合物半導体層を製造する方法であって、III−V族化合物半導体層を構成する半導体結晶を半導体基板上に成長させてエピタキシャルウェハ1を形成する工程と、エピタキシャルウェハ1上におもり104を載せることで該半導体結晶に対して荷重を付与しつつ、該半導体結晶に対しその成長温度より高い温度で熱処理を行うアニール工程とを備える。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板上に結晶成長され、孤立した島状に形成されたGe層と、Ge層の上に結晶成長され、Pを含む3−5族化合物半導体層からなるバッファ層と、バッファ層の上に結晶成長された機能層と、を備える半導体基板を提供する。Ge層は、アニールした場合に、アニールの温度および時間において結晶欠陥が移動する距離の2倍を越えない大きさの島状に形成する。あるいはGe層は、アニールした場合に、アニールの温度において基板であるSiとの熱膨張係数の相違によるストレスが剥離を発生させない大きさの島状に形成する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板の上に形成され、結晶成長を阻害する阻害層とを備え、阻害層は、基板の一部を覆う被覆領域と、被覆領域の内部に基板を覆わない開口領域とを有し、さらに開口領域に結晶成長されたGe層と、Ge層上に結晶成長された機能層と、を備える半導体基板を提供する。当該半導体基板において、Ge層は、結晶欠陥が移動できる温度および時間でアニールされることにより形成されてよい。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板の上に形成され、結晶成長を阻害する阻害層とを備え、阻害層は、基板の一部を覆う被覆領域と、被覆領域の内部に基板を覆わない開口領域とを有し、さらに開口領域に結晶成長されたGe層と、Ge層の上に結晶成長され、Pを含む3−5族化合物半導体層からなるバッファ層と、バッファ層の上に結晶成長された機能層と、を備える半導体基板を提供する。当該半導体基板において、Ge層は、結晶欠陥が移動できる温度および時間でアニールされることにより形成されてよい。

(もっと読む)

半導体基板およびその製造方法、ならびに半導体装置

【課題】圧縮歪層と引張歪層とを利用して、InP系半導体デバイスを成長させるメタモルフィック基板の欠陥(例えば転位)の低減を可能にする。

【解決手段】ガリウムヒ素基板100と、前記ガリウムヒ素基板100上に形成されたバッファ層101と、前記バッファ層101上に、前記バッファ層101よりも面内方向の格子定数が小さい材料からなる引張歪層105aと、前記バッファ層101よりも面内方向の格子定数大きい材料からなる圧縮歪層105bとを積層して形成された歪補償構造層105とを有することを特徴とする。

(もっと読む)

化合物半導体基板

【課題】化合物半導体単結晶層に残留するキャリアを抑制することによって、高速および高耐電圧デバイスに好適な窒化物半導体単結晶層を有する化合物半導体基板を提供する。

【解決手段】Si単結晶基板1上に、B,Al,V,Ni,Fe,Mg,Pt,Cr,Mo,W,Ta,Nb,Sc,Ti,Au,Co,Cuのうちの少なくともいずれか1種の不純物元素を1014〜1021/cm3含む、厚さ0.05〜2μmの3C−SiC単結晶バッファー層2と、C,V,Ni,Fe,Mg,Pt,Cr,Mo,W,Ta,Nb,Sc,Ti,Au,Co,Cuのうちの少なくともいずれか1種の不純物元素を1014〜1021/cm3含む、厚さ0.05〜5μmのGaN単結晶層3とが順次積層された構成とする。

(もっと読む)

21 - 40 / 76

[ Back to top ]