Fターム[5F152NQ07]の内容

再結晶化技術 (53,633) | 動作層、活性層、素子構成層の材料 (2,604) | 半導体 (2,300) | 3−5族 (966) | InAs (20)

Fターム[5F152NQ07]に分類される特許

1 - 20 / 20

半導体ウェハ

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体ウェハ及びその製造法

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

半導体基板、半導体基板の製造方法、および電磁波発生装置

【課題】複数の異なる周波数を出力する半導体基板を提供する。

【解決手段】p型半導体またはn型半導体を含む第1の不純物半導体と、第1の不純物半導体に接する複数の空乏領域を有する空乏化半導体とを備え、複数の空乏領域のそれぞれは、第1の不純物半導体との第1界面と、第1界面と対向する表面とを有し、複数の空乏領域のそれぞれは、第1界面に垂直な方向における第1界面と表面との平均距離および組成の少なくとも一つが異なる半導体基板を提供する。

(もっと読む)

多結晶薄膜、その成膜方法、及び薄膜トランジスタ

【課題】十分に結晶化された多結晶薄膜を提供する。

【解決手段】インジウム元素及び酸素元素を含有した非晶質膜をスパッタリング装置で成膜し加熱することで、X線回折測定において2θが25deg〜35degの範囲に観測される(222)配向のロッキングカーブの半値全幅が0.4deg以下である多結晶薄膜を形成する。又、金属酸化物をスパッタリングによって成膜するに際し、プラズマの照射を2〜5秒間隔として成膜しその後結晶化する。

(もっと読む)

ハニカムヘテロエピタキシーを含む半導体装置

【課題】ハニカムヘテロエピタキシーを含む半導体装置を提供する。

【解決手段】ハニカムヘテロエピタキシーを含む半導体装置とその製造方法が開示される。一実施例は、貫通する複数のナノサイズの開口を有するマスクをシリコン基板上に定義するステップと、定義ステップ後、マスク開口を介して露出したシリコン基板表面の一部に、本質的に無欠陥の非シリコン半導体ナノアイランドを作成するステップと、作成ステップ後、ナノアイランド上に、高kゲート誘電体を蒸着するステップと、蒸着ステップ後、ナノアイランド上に、トランジスタを構成するステップとを備える方法である。

(もっと読む)

半導体デバイスおよび半導体構造の製造方法

【課題】 半導体結晶材料の作製またはこの半導体結晶材料を含む構造を提供する。

【解決手段】 第1の半導体結晶材料の表面の粗さは、低減されている。半導体デバイスは、第1の結晶材料の表面上に低欠陥の歪んだ第2の半導体結晶材料を含む。歪んだ第2の半導体結晶材料の表面の粗さは、低減されている。一実施例は、第1および第2の半導体結晶材料間の界面境界の不純物を減少させるプロセスパラメータを作成することによって、粗さが低減された表面を得ることを含む。一実施の形態では、第1の半導体結晶材料は、アスペクト比トラッピング技術を用いて欠陥をトラップするのに十分なアスペクト比を有する絶縁体の開口によって限定されることができる。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】 p型不純物が隣接する半導体結晶層中へ拡散することを抑え、ひいては良好で安定した特性を持つ半導体装置を提供する。

【解決手段】 P−InP基板401と、P−InP基板401に格子整合し、かつ、p型の不純物が注入されたp−ZnドープInPバッファ層402と、p−ZnドープInPバッファ層402よりも上層にあって、P−InP基板401に格子整合し、かつ、p型不純物、n型不純物のいずれか一方を含むn−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405と、を備え、n−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405に、Sbを含ませる。

(もっと読む)

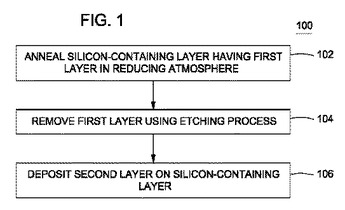

界面汚染を低減した層を堆積させる方法

本明細書では、界面汚染を低減した層の堆積方法を開示する。発明の方法は、有利には、堆積させた層間の汚染、例えば堆積させた層とその下にある基板または膜との間の界面の汚染を減少させる。幾つかの実施形態では、層の堆積方法は、第1の層が上に配置されたシリコン含有層を還元性雰囲気中でアニールすることと、アニールの後で、シリコン含有層を露出させるエッチングプロセスを使用して第1の層を除去することと、露出したシリコン含有層の上に第2の層を堆積させることとを含むことができる。  (もっと読む)

(もっと読む)

多層膜構造体およびその形成方法

【課題】半導体素子用の多層膜構造体を基板上に形成する多層膜構造体であって、大きな伸張歪を半導体層に印加できる多層膜構造体の形成方法を提供する。

【解決手段】半導体素子用の多層膜構造体10を基板上に形成する際に、基板11上に、当該基板11を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、圧縮歪を有する圧縮歪半導体層12を形成する。その圧縮歪半導体層12の上方に、圧縮歪半導体層12を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、無歪の無歪半導体層13を積層する。圧縮歪半導体層12の圧縮歪を緩和させることにより、無歪半導体層13に伸張歪を印加する。それにより、大きな伸張歪を無歪半導体層13に印加することができる。

(もっと読む)

半導体ウェハ及びその製造法

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

化合物半導体積層体

【課題】InAs層等の活性層を直接GaAs等の基板上に形成した構造の化合物半導体積層体であって、信頼性が高く、かつ、バルク単結晶に対して電子移動度の低下が小さい化合物半導体積層体を提供すること。

【解決手段】本発明に係る化合物半導体積層体は、GaAs基板上にInAs層を0.3μm以上と厚く形成し、そのInAs層上にInAs層と基板に平行方向の格子定数が等しく、基板に垂直方向の格子定数差が3%以内の化合物半導体保護層を形成することを特徴とする。すなわち、GaAs、InP、Siのバルク単結晶板、またはそれらの薄膜基板上に、直にInxGa1−xAsySb1−y(0≦x≦0.5、0≦y≦1)を活性層として、0.3μm以上3μm以下の厚さで形成する。この活性層には、導電性の小さな半導体層を保護層として直に形成する。

(もっと読む)

高性能CMOS技術のための低コストの歪みSOI基板

【課題】エピタキシャル成長及びその後のウェハ接合処理ステップを回避するSSOI構造の製造方法を提供する。

【解決手段】歪み半導体オン・インシュレータ(SSOI)構造体を製造する。SOI基板上に歪み半導体領域を生成するために、歪み記憶技術が用いられる。半導体領域が歪んでいるので、歪み半導体領域上に形成されたトランジスタは、より高いキャリア移動度を有する。(i)薄いアモルファス化層を生成するためのイオン注入と、(ii)アモルファス化層上への高応力膜の堆積と、(iii)アモルファス化層を再結晶させるための熱アニールと、(iV)高応力膜の除去とを含む。再結晶化プロセスの間、SOI基板は応力を受けたので、最終的な半導体層も、応力を受ける。応力の量及び応力の極性(引張又は圧縮)は、高応力膜のタイプ及び厚さによって制御することができる。

(もっと読む)

半導体作製装置および半導体作製方法

【課題】真空雰囲気下において脱着可能なメタルマスクを用いて、半導体基板上に半導体層を選択的に再現性よく形成することが可能な半導体作製装置を提供する。

【解決手段】半導体基板が搭載される試料ホルダと、半導体基板に選択的に結晶を成長させるための少なくとも1つ以上の第1の開口を有するマスクと、半導体基板およびマスクを試料ホルダとの間に挟み、試料ホルダと組み合わされるマスクホルダと、マスクとマスクホルダとの間に設けられた弾性体とを有する構成である。

(もっと読む)

ハイブリッド・チャネル配向を有するCMOSデバイスおよびファセット形成エピタキシを用いてハイブリッド・チャネル配向を有するCMOSデバイを作製するための方法

【課題】別々の表面配向(すなわちハイブリッド表面配向)を有する半導体基板を提供する。

【解決手段】第一のデバイス領域2は、第一の等価結晶面の組の一つの方位に配向した実質的に平坦な表面16Aを有し、第二のデバイス領域は、第二の、別の等価結晶面の組の方位に配向した複数の交差する表面16Bを有する突起形半導体構造物18を含む。そのような半導体基板を用いて、半導体デバイス構造を形成することができる。詳しくは、第一のデバイス領域に第一の電界効果トランジスタ(FET)を形成することができ、第一のFETは、第一のデバイス領域の実質的に平坦な表面に沿って延在するチャネルを含む。第二のデバイス領域に第二の、相補FETを形成することができ、第二の、相補FETは、第二のデバイス領域にある突起形半導体構造物の複数の交差する表面に沿って延在するチャネルを含む。

(もっと読む)

半導体量子ドット構造の製造方法

【課題】従来のMOVPE成長を用いた半導体量子ドットの製造方法における限界あるいは欠点を解決するためになされたもので、良好な光学特性、高い面密度、高い均一性を兼ね備えた半導体量子ドットをMOVPE成長により実現することを目的とする。

【解決手段】MOVPEを用いて形成する半導体量子ドット構造の製造方法であって、TMIとTBAs、或いはTMIとTIPGとTBAsを主たる原料とし、且つ成長温度が300℃以上、450℃未満とし、且つ成長条件においてV族原料とIII族原料との供給比すなわちV/III比(モル比)が150以上、或いはTBAsの分圧が30Pa以上、又は、前記V/III比(モル比)が300以上、或いはTBAsの分圧が60Pa以上とし、且つ上記量子ドット構造の成長前、或いは成長時にTMBiなどのビスマス原料或いはTMSbなどのアンチモン原料も供給して、量子ドットを成長させる。

(もっと読む)

代替活性エリア材料の集積回路への組み込みのための解決策

結晶半導体基板上に代替材料のエリアを形成する方法、並びにこの方法により形成された構造。このような代替材料のエリアは、MOSFET又は電子デバイス若しくは光電子デバイスにおける活性エリアとしての使用に適している。  (もっと読む)

(もっと読む)

転位の無い歪んだ結晶を作成するための方法

転位が無い歪んだシリコンの薄膜を形成するための方法が、2つの湾曲したシリコン基板を与えるステップを有する。一方の基板は、背面上の二酸化シリコンの存在により湾曲する。他方の基板は、窒化シリコン層の存在により湾曲する。基板のうちの一方が、水素注入を受け、焼鈍処理において2つの基板を互いに接着する。2つの基板を離すと、一方の基板の前面に歪んだシリコン層が残る。そして、二酸化シリコン又は窒化シリコンの背面層を除去して、ほぼ平らな状態に基板を戻す。この方法を採用して転位の無い歪んだシリコン薄膜を形成してよい。この膜は、引張又は圧縮歪みのいずれかの状態でよい。 (もっと読む)

混合結晶配向のチャネル及びソース/ドレイン領域をもつ電界効果トランジスタ

【課題】 混合結晶配向のチャネル及びソース/ドレイン領域をもつ電界効果トランジスタを提供すること。

【解決手段】 ハイブリッド配向基板は、n型電界効果トランジスタ(nFET)が電子移動度に最適な半導体の配向内に配置され、p型電界効果トランジスタ(pFET)が正孔移動度に最適な半導体の配向内に配置される、相補型金属酸化膜半導体(CMOS)回路の製造を可能にする。本発明は、最適な半導体の配向内に完全に形成されたFETの性能利点が、デバイスのチャネルを最適な配向をもつ半導体内に配置することを必要とするだけで実現できることを開示する。様々な新しいFET構造体が説明され、その全ては、FETのチャネルは、FETのソース及び/又はドレインとは異なる配向を有するという特徴を備えている。これらの新しいFETを組み込むことができるハイブリッド基板は、その製造方法と共に説明される。

(もっと読む)

半導体基板を作製する方法

【課題】絶縁体上歪み半導体(SSOI)基板を作製する方法が提供される。

【解決手段】この方法で、歪み半導体は、あらかじめ形成された絶縁体上半導体基板の絶縁体層の上に直接配置された50nm未満の厚さを有する薄い半導体層である。本発明のSSOI基板を形成する際に、ウエハボンディングは使用されない。

(もっと読む)

1 - 20 / 20

[ Back to top ]