Fターム[5H007CA02]の内容

Fターム[5H007CA02]に分類される特許

201 - 220 / 1,588

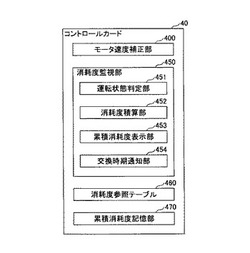

射出成形機及び電力用半導体素子消耗度監視システム

【課題】電力変換装置における電力用半導体素子の消耗度をより正確に且つより低い演算負荷で監視する電力用半導体素子消耗度監視システムを備える射出成形機を提供すること。

【解決手段】電力変換装置10における電力用半導体素子の消耗度を監視する電力用半導体素子消耗度監視システム100を備える射出成形機は、電力変換装置10の運転状態が予め設定された複数の運転パターンの何れに該当するかを判定する運転状態判定部451と、それら複数の運転パターンのそれぞれが実行された場合のその電力用半導体素子の消耗度を予め記憶する消耗度参照テーブル460と、消耗度参照テーブル460を参照して、運転状態判定部451が判定した運転パターンが実行された場合のその電力用半導体素子の消耗度を取得して積算する消耗度積算部452と、を備える。

(もっと読む)

電流検出回路、モータ駆動装置

【課題】少ない部品点数で低コストかつ高精度にインバータ電流を検出することのできる電流検出回路を提供する。

【解決手段】電流検出抵抗8の両端電圧を増幅する増幅回路30と、増幅回路出力の最大値を保持し、かつ増幅回路の出力を増幅するピークホールド回路31を備える。前記ピークホールド回路31は、電源9がインバータ主回路29に供給する電流値を示す検出信号を当該電流検出回路の外部に出力し、前記増幅回路30が出力する信号の信号レベルが最大値より低いレベルとなっている期間において、所定時間の間は、前記最大値を示す信号レベルを保持しつつ当該電流検出回路の外部に前記検出信号を出力し続けることを特徴とする電流検出回路。

(もっと読む)

インバータ装置及びこれを搭載した電動車両

【課題】インバータ回路に対する電源部やモータの誤接続に起因するインバータ回路のスイッチング素子の破損を防止することが可能なモータ制御装置を提供する。

【解決手段】電動車両1のインバータ装置50は、複数のスイッチング素子61〜63が設けられ、直流電力を交流電力に変換するインバータ回路部60と、スイッチング素子の温度を検出する温度検出センサ71〜73と、を備え、インバータ回路部60は、その各相に対応する上アーム側及び下アーム側各々のスイッチング素子61〜63が2個並列にして接続され、温度検出センサ71〜73は各々、並列にして接続されたスイッチング素子61〜63の中間に配置されている。これにより、温度検出センサ71〜73はスイッチング素子61〜63のオープン故障に起因する発熱がもたらす異常な温度上昇を検出する。

(もっと読む)

プリドライバ回路、および、駆動回路

【課題】回生電流がモータ等の負荷から駆動回路を構成するプリドライバ回路側に流れても、駆動回路の制御に影響を与えないようにすること。

【解決手段】第1の電源電圧(VM)に接続された第1の駆動トランジスタと、接地に接続された第2の駆動トランジスタとの間の負荷に接続される接続ノード(N1)を出力端子とするブリッジ回路に接続されたプリドライバ回路において、接続ノード(N1)である出力端子に接続された出力モニタ回路を有し、該出力モニタ回路を用いて、出力端子に現れる電圧(Vout)に基づいて電圧のみをフィードバックさせる第1のフィードバック信号(S1)を生成し、第1のフィードバック信号(S1)に基づいて第2のフィードバック信号(S2)を生成して、出力端子に現れる電圧(Vout)が第1の電源電圧(VM)に近づくように、第1の駆動トランジスタを駆動制御する。

(もっと読む)

電子制御装置

【課題】第1回路基板とその第1回路基板に重合する第2回路基板とを接続する端子ピンの増加による大型化を抑制した制御装置を提供する。

【解決手段】パワーモジュール5と制御モジュールとを接続する複数の信号系端子ピン22を、パワーモジュール側接続部23と制御モジュール側接続部24とが中間連結部25aに対してオフセットするように曲折した形状にそれぞれ形成し、それらの各信号系端子ピン22の中間連結部25aを所定の整列方向で一列に整列配置するとともに、その整列方向で近接する一対の信号系端子ピン22のパワーモジュール6に対する実装姿勢を中間連結部25aを中心とした回転方向で互いに180度異ならしめることにより、各信号系端子ピン22a,22bの両接続部23,24をそれぞれ二列に整列させる。

(もっと読む)

電子装置

【課題】オン駆動用スイッチング素子がオン故障してスイッチング素子をオフできない異常状態になっても、スイッチング素子の熱破壊を防止することができる電子装置を提供する。

【解決手段】制御回路128は、オン駆動用FET121aのゲート電圧がオンしない電圧であるにもかかわらず、ドレイン−ソース間電圧がオンした際の電圧であるとき、オン駆動用FET121aがオン故障していると判断する。そして、駆動用電源回路120の動作を停止させ、駆動用電源回路120からの電圧の供給を遮断する。その結果、ゲート電圧がオン、オフする閾値電圧より低くなり、IGBT110dがオフする。そのため、オン駆動用FET121aがオン故障してIGBT110dをオフできない異常状態になっても、IGBT110dの熱破壊を防止できる。

(もっと読む)

補助基板上の発熱部品の放熱構造

【課題】母基板に実装される補助基板上に実装された発熱対象部品を、省スペースでかつ安価に絶縁距離を確保しながら放熱できる補助基板上の発熱部品の放熱構造を提供する。

【解決手段】補助基板上の発熱部品の放熱構造は、補助基板13と、補助基板13上に実装される放熱対象部品11と、少なくとも放熱対象部品11を覆い、絶縁および熱伝導を兼ねる樹脂製品21と、樹脂部品21を介して少なくとも放熱対象部品11上の対向する面に置かれる放熱板15とを有する補助基板回路部10を備え、補助基板回路部10を母基板7に実装する。

(もっと読む)

電子装置

【課題】スイッチング素子をオフするように制御しているにもかかわらず、オフできない異常状態を検出することができる電子装置を提供する。

【解決手段】IGBT110dに流れる電流が電流閾値より大きくなると、電流検出回路125は、IGBT110dに電流が流れていると判断する。制御回路128は、駆動信号がIGBT110dのオフを指示しているにもかかわらず、電流検出回路125がIGBT110dに電流が流れていると判断すると、IGBT110dをオフできない異常状態にあると判断する。そして、駆動用電源回路120の動作を停止させ、駆動用電源回路120からの電圧の供給を遮断する。その結果、ゲート電圧がオン、オフする閾値電圧より低くなり、IGBT110dがオフする。そのため、駆動信号がIGBT110dのオフを指示しているにもかかわらず、IGBT110dをオフできない異常状態を検出することができ、IGBT110dの熱破壊を防止できる。

(もっと読む)

電源ユニット及び制御装置

【課題】電源ユニットの出力ラインにおける地絡などの故障に対し、電源の保護及び故障の検知を行う。

【解決手段】サブ電源供給ラインLSに、サブ電源101側をソースとして第1MOSFET102を直列に接続し、第1MOSFET102のドレインにドレインを接続させて第2MOSFET103を直列に接続する。制御ユニット200内のサブ電源供給ラインLSにも、サブ電源101側をソースとして第3MOSFET202を直列に接続し、第3MOSFET202のドレインにドレインを接続させて第4MOSFET203を直列に接続し、第1〜第4MOSFETを制御することで、サブ電源101の電力を負荷201に対して供給する。各MOSFETのドレイン電圧、及び、第2MOSFET103と第3MOSFET202との間の電圧をモニタし、MOSFETの故障及びサブ電源供給ラインLSの故障を診断する。

(もっと読む)

パワーモジュール

【課題】複数のパワーデバイスを有するパワーモジュールにおいて、保護機能の信頼性の向上、小型化およびコスト削減を図る。

【解決手段】パワーモジュール100は、2つのスイッチング素子10,20を流れる主電流の大きさに応じたレベルをとる電流検出信号DT1,DT2を生成する電流検出部12,22を備え、駆動制御部13,23は、それぞれ電流検出信号DT1,DT2の両方を受け、そのレベルの組み合わせに基づいて、スイッチング素子10,20の過電流の発生を検知し、スイッチング素子10,20の保護動作を行う。

(もっと読む)

三相インバータ装置およびそれを用いたモータ駆動装置あるいは空気調和機

【課題】双方向素子のゲート駆動をブートストラップ回路を用いた唯一の電源で構成する三相インバータ回路において通電初期から安定したインバータ動作を行うことを目的とする。

【解決手段】第一ゲート端子3には第1のコンデンサ7、第三ゲート端子5は片側を出力に接続した第2のコンデンサ8を通じて通電され、第1のコンデンサ7は第2のコンデンサ8を通じて充電されるブートストラップ回路9と、前記第二ゲート端子4および第四ゲート端子6を駆動するために信号出力する論理素子10を設け、前記論理素子10およびブートストラップ回路9は唯一の定電圧源より供給され、通電当初に論理素子10は第四ゲート端子6を通電する構成としたことにより、通電初期に第2のコンデンサ8を急速に充電させる経路を確保することができることとなるので、ブートストラップ回路9を通電初期から安定した運転を行うことができる三相インバータを得られる。

(もっと読む)

電源回路およびそれを備えた画像形成装置

【課題】インダクタンスや容量の大きさが動的に変化しても矩形波の形状を維持することで、ダンピング抵抗に対する依存性を低下させつつ、安定な現像性を達成する。

【解決手段】変圧手段は交流電圧発生手段から発生される交流電圧を所定の出力電圧に変圧する。調整手段は出力電圧の矩形波に生じる波形歪みに応じて交流電圧発生手段を駆動する駆動パターンを調整する。駆動パターンは、交流電圧の矩形波の半周期において、交流電圧を変圧手段に印加する第1のオン期間、交流電圧を変圧手段に印加しないオフ期間、および、交流電圧を変圧手段に印加する第2のオン期間とを有した信号パターンである。調整手段は、波形歪みが小さくなるように、第1のオン期間、オフ期間および第2のオン期間の割合を調整する。

(もっと読む)

マルチレベルインバータ

【課題】マルチレベルインバータの有利な特徴を生かしつつ、マルチレベルインバータの課題であるトランジスタ等の半導体スイッチング素子の数的増大化を解消すること。

【解決手段】2つのアーム部4、5と、クランプダイオードD7、D8と、を含み、一方のアーム部4内の2つの直列接続のスイッチング素子の直列接続点a3と、他方のアーム部5内の2つのスイッチング素子Q5,Q6の直列接続点a4とを線間電圧出力側とすると共に、一方のアーム部4は、PWM制御し、他方のアーム部5は180度通流制御する。

(もっと読む)

インバータ駆動装置および冷凍空気調和装置

【課題】逆回復における損失低減をはかりつつ、システムの高効率化をはかり、また、素子の損傷等に対応して信頼向上等をはかることができるインバータ駆動装置等を得る。

【解決手段】変換用のスイッチング素子4と、このスイッチング素子4に並列接続された還流ダイオード5とを備えるアームを一対以上有するインバータ駆動装置2であって、スイッチング素子4および還流ダイオード5に、二次側巻線を並列接続する変圧器6と、変圧器6の一次側巻線への電流供給を制御する変圧器駆動回路11とを備えるものである。

(もっと読む)

駆動装置

【課題】消費電力を低減した駆動装置を提供する。

【解決手段】コイルに電流を供給する第1N型MOSFETと、前記第1N型MOSFETと直列接続され、前記コイルから電流が供給される第2N型MOSFETと、前記第2N型MOSFETがオフしているときに前記第1N型MOSFETをオンするように第1駆動信号を出力する第1駆動回路と、前記第1N型MOSFETがオフしているときに前記第2N型MOSFETをオンするように第2駆動信号を出力する第2駆動回路と、ドレインソース路が前記第1駆動回路の出力及び前記第1N型MOSFETのゲートの間に接続されるP型MOSFETと、前記第1N型MOSFET及び前記P型MOSFETのゲートソース間電圧を共に所定電圧にクランプするクランプ回路と、前記P型MOSFETのドレインソースに並列接続される第1抵抗と、を備えた駆動装置である。

(もっと読む)

パワーコンディショナ

【課題】生成した正弦波電圧の波形の一部にスパイク状電圧が発生することを抑制する。

【解決手段】第3パルス電圧列の電圧と正弦波電圧との差電圧の正負に応じてチョッピングするタイミングと、第7、第8スイッチ素子16,17のオンオフデューティの切り替わりタイミングとのずれを演算し、かつ、前記タイミングずれに対応して前記第7、第8スイッチ素子16,17のオンオフデューティを制御する。

(もっと読む)

パワーコンディショナ

【課題】直列接続した一対のスイッチ素子のオンオフにデッドタイム期間を設けた方式の回路において、このデッドタイム期間にいずれか一方のスイッチ素子が有効オンとなることに起因して生成する正弦波電圧の波形の一部における歪みを抑制する。

【解決手段】本パワーコンディショナは、ダイオードが個々に逆並列接続されかつ互いに直列接続された2つのスイッチ素子を含む第1、第2組を含み、第1組の両スイッチ素子を所定のチョッピング周波数で交互にオンオフし、第2組の両スイッチ素子を前記チョッピング周波数より高いPWM周波数で交互にオンオフすると共にこれら各組の両スイッチ素子のオンオフタイミングにデッドタイム期間を設けて制御する場合に、第1組の各スイッチ素子のデッドタイム期間中における前記各ダイオードにより一方のスイッチ素子における有効オン駆動に対応して、前記2組のスイッチ素子のオンオフデューティを調整制御するようにしたパワーコンディショナである。

(もっと読む)

電力変換装置、及び、これを用いた電動パワーステアリング装置

【課題】インバータ部および昇圧回路部を備える電力変換装置において、スイッチング素子のスイッチング回数を減らし、スイッチングロスを低減する。

【解決手段】3相回転電機の電力変換装置のインバータ制御部は、巻線組に印加される電圧に係るデューティ指令信号DLを、最小値が出力可能なデューティ範囲の最小値Rminに一致するように下べた二相変調処理する。これにより、PWM1周期中に、3相のうち1相のスイッチング素子はPWM基準信号Pの谷点OLでスイッチングしないため、スイッチング回数が2/3に減少する。また、昇圧回路制御部は、昇圧PWM基準信号DBの周波数をインバータ部のPWM基準信号Pの周波数と同一とする。これにより、昇圧回路部のスイッチング素子のスイッチング回数は、従来技術に対して半分となる。よって、スイッチングロスを低減することができる。

(もっと読む)

インバータ回路、電力変換回路、及び電気推進車両

【課題】フルブリッジ型のインバータ回路の制御回路において、第1のハーフブリッジ回路及び第2のハーフブリッジ回路を構成するハイサイドトランジスタ及びローサイドトランジスタのスイッチングの制御中のエラーによる、出力される信号の歪みを低減することを目的の一とする。

【解決手段】第1のハーフブリッジ回路と第2のハーフブリッジ回路におけるハイサイドトランジスタ及びローサイドトランジスタのオンまたはオフを制御する信号のパルス幅を小さくする、すなわちデューティ比の小さい信号とするものである。その結果、ハイサイドトランジスタ及びローサイドトランジスタが共にオンになる短絡期間を削減し、信号の歪みを低減するものである。

(もっと読む)

半導体スイッチング装置

【課題】本発明は、ノイズの発生を抑えつつ、ダイオードの逆回復電流を抑制できる半導体スイッチング装置を提供することを目的とする。

【解決手段】本願の発明にかかる半導体スイッチング装置は、誘導負荷への電流の供給を制御するスイッチング素子と、該誘導負荷の還流電流が流れるように該誘導負荷に接続されたダイオードと、該ダイオードの逆回復電流が流れる配線と、該配線の少なくとも一部を覆うように形成された磁界吸収体と、を備えたことを特徴とする。

(もっと読む)

201 - 220 / 1,588

[ Back to top ]