Fターム[5H420EA18]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 主制御部 (1,336) | 主制御素子の種類 (840) | 半導体素子 (707) | トランジスタ (418) | 電流ミラー回路 (40)

Fターム[5H420EA18]に分類される特許

1 - 20 / 40

定電流回路及び定電流回路を使用した発光ダイオード駆動装置

【課題】高精度な出力電流を出力できる出力端子の動作電圧範囲を大幅に拡大することができると共に、効率を高めることができる定電流回路及び定電流回路を使用した発光ダイオード駆動装置を得る。

【解決手段】第1定電流i1と同じ電流値の第4定電流i4を生成してNMOSトランジスタM1と同一導電型のNMOSトランジスタM16に供給し、NMOSトランジスタM16における第4定電流i4が入力されるドレインの電圧をレベルシフトさせてNMOSトランジスタM16のゲートに入力して得られたNMOSトランジスタM16のドレイン電圧を基準電圧とし、電圧調整回路4を構成するNMOSトランジスタM14と定電流源2との接続部の電圧と該基準電圧との電圧を誤差増幅回路OP1で比較して該比較結果を示す信号Doutを出力するようにした。

(もっと読む)

安定化電源回路

【課題】Vin≦Voutになったときであっても、確実にパワートランジスタの駆動電流を停止させ、逆電流を抑止できるようにする。

【解決手段】電圧入力端子3と電圧出力端子1の間に接続されたパワートランジスタQ3と、電圧出力端子1と接地端子2の間の出力電圧を検出して基準電圧Vrefと比較するエラーアンプ4と、該エラーアンプ4の出力電圧によってパワートランジスタQ3を制御するドライブトランジスタQ2と、パワートランジスタQ3の制御性を改善するための抵抗R2と、その抵抗に流れる電流を遮断又は通過させるスイッチトランジスタQ4と、Vin>Voutのときコレクタ電流を流してスイッチトランジスタQ4を動作させ、Vin≦Voutのときコレクタ電流を遮断してスイッチトランジスタQ4を不動作にさせる異常検出トランジスタQ5とを備える。

(もっと読む)

DC−DCコンバータの異常電流防止回路

【課題】回路規模が小さくて遅延が少なく且つ特性に与える素子バラツキの影響が小さいDC-DCコンバータの異常電流防止回路を提供する。

【解決手段】検出抵抗12の電圧は通常時(正常時)には負電圧であるが異常時に逆電流が生じた場合には正電圧が現れるようになる。電流コンパレータ30は検出抵抗12の電圧を監視し、検出抵抗12の電圧が負電圧の間はハイ出力をAND回路20に送ってドライバ10の出力信号がローサイド側スイッチ素子14,19に伝わるようにし、検出抵抗12の電圧が正電圧になると電流コンパレータ30の出力電圧はローになり、ローサイド側スイッチ素子14,19を強制的にOFFにする。電流コンパレータ30は従来の電圧コンパレータに比べ出力電流値を大きくすることができ、異常電流発生の判定に遅延が生じず速度が極めて速くなり、且つ変化幅を大きく取ることができる。

(もっと読む)

充電制御用半導体集積回路

【課題】電流制御用MOSトランジスタに流れる電流をカレントミラー方式で検出して制御する充電制御用ICにおいて、トランジスタのサイズ比がばらついても電流検出精度を向上させることができるようにする。

【解決手段】カレントミラー方式の電流検出回路(13)に、バイアス状態制御用トランジスタ(Q3)と、電流制御用トランジスタ(Q1)と電流検出用トランジスタのドレイン電圧を入力とする演算増幅回路(AMP1)とを設け、該演算増幅回路の出力に基づいて電流検出用MOSトランジスタのバイアス状態が、電流制御用MOSトランジスタのバイアス状態と同一になるように構成するとともに、電流制御用トランジスタと電流検出用トランジスタの各ドレイン電極から演算増幅回路の対応する入力点までの配線の寄生抵抗による電圧降下が同一となるように、電流検出用トランジスタのドレイン配線の長さを調整するようにした。

(もっと読む)

過電流保護回路

【課題】 電路を遮断する精度が環境温度の変化によって低下しない過電流保護回路を実現する。

【解決手段】 検出抵抗R3に流れる過電流を検出するカレントミラー回路9を構成する第1および第2のトランジスタT1,T2は同じ温度特性を有する。第1および第2の制限抵抗R1,R2と、検出抵抗R3と、電流I1,I2とには、R1=R2−(I3/I1)R3の関係があり、過電流が流れる前はI1>I2、過電流が流れた瞬間以降はI2>I1となるように設定されている。上記の式には、ベースエミッタ間電圧など、温度特性によって変動するパラメータが存在しないため、環境温度が変化した場合であっても第2のトランジスタT2が第4のトランジスタT4をオンするタイミングが変動しない。

(もっと読む)

パラメータ制御回路およびその方法

【課題】パッケージに必要な端子数を減らすことができる回路を提供する。

【解決手段】一実施例において、パラメータ制御回路の単一入力端子は、パラメータ制御回路の2つの異なるパラメータを形成するために使用される。第1入力と、入力パスおよびミラー・パスを有する第1電流ミラーのミラー・パスを通る第1電流を有効または無効にするために形成されるスイッチと、第1電流を受け取るために結合されるキャパシタと、入力パスおよびミラー・パスを有する第2電流ミラーであって、前記入力パスは前記第1入力に結合され、前記第2電流ミラーは、前記第1電流を無効にする前記スイッチに応答して、前記キャパシタを放電するために前記ミラー・パスを通して第2電流を形成するために結合され、前記第2電流ミラーは、前記第1電流の第1値と異なる第2値を具備する前記第2電流を形成するために構成される、第2電流ミラーと、を含む。

(もっと読む)

カレントミラー回路

【課題】カレントミラー回路の精度を向上する。

【解決手段】ベース・コレクタ間が短絡されたトランジスタQ1と、トランジスタQ1のベースにベースが接続されたトランジスタQ2とを含み、トランジスタQ1のコレクタにゲートが接続され、ソースが第1および第2トランジスタのベースに接続され、ドレインが電源に接続されたMOS型の補償トランジスタを有する。これによって、トランジスタQ1に流れる電流に応じた電流をトランジスタQ2に流すが、補償トランジスタQ5には、ベース電流が不要となる。

(もっと読む)

電圧生成回路

【課題】回路面積を削減する。

【解決手段】電圧生成回路100は、電源電圧Vddに固定された電源端子50と接地電圧に固定された接地端子52の間に、直列に設けられた可変インピーダンス素子12と、出力トランジスタ10と、を備える。出力トランジスタ10のゲートにバイアス電圧Vbiasを印加し、可変インピーダンス素子12と出力トランジスタ10の接続点24の電圧V1を出力する。定電流源22は、所定の定電流Ic1を生成する。基準トランジスタ20は、定電流Ic1の経路上に設けられる。出力トランジスタ10と基準トランジスタ20をカレントミラー接続される。

(もっと読む)

基準電圧発生回路

【課題】出力される基準電圧を低減可能とし、基準電圧の温度特性の変動幅を狭め基準電圧回路を提供する。

【解決手段】第1乃至第3の電流−電圧変換回路と、第1の電流−電圧変換回路の端子電圧と第2の電流−電圧変換回路の端子電圧が互いに等しくなるように制御する制御手段(AP1)と、前記第1、第2、及び第3の電流−電圧変換回路を駆動するカレントミラー回路(M1、M2、M3)と、を有し、第3の電流−電圧変換回路の所定の電圧を基準電圧(VREF)とし、第1の電流−電圧変換回路はダイオード(D1)からなり、第2の電流−電圧変換回路は、並列接続された複数個のダイオード(D2)と、該複数個のダイオードに並列接続された抵抗(R2)と、該複数個のダイオードと抵抗の並列回路に直列接続された抵抗(R1)からなり、第3の電流−電圧変換回路は抵抗(R3)からなる。

(もっと読む)

基準電圧発生回路

【課題】発生させる基準電圧の電圧レベルが高くなった場合でも、基準電圧を所定の許容範囲内に調整することができる基準電圧発生回路を提供する。

【解決手段】モード切替回路12より、発生させる基準電圧に応じて当該基準電圧の電圧レベルが高くなるほど電流値の大きな供給電流を供給し、調整回路14により、供給電流の通電経路における所定位置の電圧を基準電圧Vrefとして出力すると共に、当該通電経路の抵抗値を変更することにより出力される基準電圧の電圧レベルを調整しており、基準電流制御回路16により、発生させる基準電圧の電圧レベルが高い場合に通電経路に通電される供給電流の一部を分岐させる。

(もっと読む)

レギュレータ回路

【課題】安定性、高速応答性、及び確実に高い精度での電源電圧の発生を実現可能なレギュレータ回路、更にはそれらをより簡単な構成で実現させたレギュレータ回路を提供する。

【解決手段】レギュレータ回路は、負荷駆動アンプAMPLD2、レプリカアンプAMPLD2R、オペアンプ回路AMPF1、抵抗RF1R、RF2Rで構成される分圧回路、抵抗RF1、RF2で構成される分圧回路、及びその抵抗RFに一端が接続されたコンデンサCOUTを備えている。それらのアンプAMPLD2、AMPLD2Rは基本的に同じ構成であり、3つのPMOSトランジスタ、2つのNMOSトランジスタを備えている。2つのNMOSトランジスタは差動対を構成し、その一方のゲートにはオペアンプ回路AMPF1からの信号LDAREFが入力され、他方のゲートには、分圧回路からの信号DIVO1、或いはDIVO1Rが入力される。

(もっと読む)

バンドギャップ回路

【課題】1.35V程度以下の電源電圧でも、周囲温度に依存しないバンドギャップ電圧を生成する。

【解決手段】回路ブロック1では、NPN12のPN接合の順バイアスで温度に反比例する電圧V1を発生させ、抵抗16に印加して温度に反比例する電流Ibを生成する。回路ブロック2では、NPN22と抵抗23で温度に反比例する電圧と比例する電圧の和の電圧V3を発生させ、NPN29で温度に反比例する電圧V4を発生させる。更に電圧V3,V4を各々電流Ic,Idに変換して減算し、温度に比例した電流Ic−Idを生成する。回路ブロック1の電流Ibと回路ブロック2の電流Ic−Idを回路ブロック3に与えると、回路ブロック3には温度特性が打ち消された電流Ieが流れる。電流Ieは1/2に減少されて抵抗45に供給され、バンドギャップ電圧VBGに変換される。

(もっと読む)

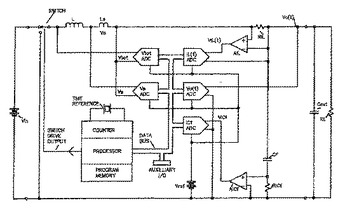

予測エネルギー平衡を用いた電力変換レギュレータ

誘導リアクトルと、出力フィルタ・リアクトルと、誘導リアクトルにエネルギーを入れるためのスイッチとを備える電力変換レギュレータがさらに、誘導リアクトル内の磁束、基準信号、出力電圧、また場合により出力負荷電流に応答する計算回路を備える。この計算回路は、スイッチを駆動する各チョッピング波形周期中に基準信号との所望の関係に出力電圧または電流を調整するために負荷および出力フィルタ・リアクトルに供給しなければならないエネルギーの量を計算するためのものである。誘導リアクトルが入力エネルギー源から充電されるとき、計算回路は、誘導リアクトル内のエネルギーがレギュレーションに十分になったかどうかを予測する。  (もっと読む)

(もっと読む)

電流発生回路

【課題】 電源電圧が低い場合でも正確な基準電流のカレントミラー動作を可能とし、これによって正確な出力電流を得ること。

【解決手段】 トランジスタM143のドレイン端子(出力端子)と、トランジスタM141のドレイン端子との電圧を、差動増幅器op142の入力端子に接続し、差動増幅器op142の出力端子をトランジスタM142のゲートに接続することで、トランジスタM141とトランジスタM142のドレイン電圧を等しくし、正確な電流出力を供給する。

(もっと読む)

定電流回路

【課題】 CMOSプロセスでは、ポリシリコン抵抗等において通常の抵抗素子とは逆の負の温度特性を有する抵抗素子を形成することがあり、それに応じて定電流回路が温度変化の影響を受け易くなる。

【解決手段】 正の温度特性を有する電流I1を流すトランジスタQ1、抵抗素子R1及びバイポーラトランジスタQ6とは並列に、負の温度特性を有する電流I2を流すトランジスタQ8、抵抗素子R2からなる温度補償回路を設ける。I1とI2との和電流Iに基づいて定電流出力を得ることにより、温度変化の影響の少ない出力が得られる。

(もっと読む)

電流制限回路

本発明は、出力端子(out)において、高電流注入に基づき、大きな電流増加を検出および迅速に制限するための回路装置に関する。特に、駆動回路(40)によって、低抵抗素子(R0)を通して制御され、電流オーバーシュートが通過する、ゲート制御式スイッチングデバイス(P0)は、本発明の回路によって代替的に駆動され、一方で、その制御端子が高注入電流によって充電される。よって、正の傾斜を有する急な前部インパルスによって生成された大きな電圧増加が、キャパシタ(C)によって検出され、ゲート端子(GateN)に伝達されると、本発明の回路は、駆動回路(40)をバイパスし、一方で、トランジスタ(P3)から発せられた著しい電流ピークを、ゲート制御式スイッチングデバイス(P0)のゲート端子(GateP)に向けて注入し、これに対して、キャパシタ(C)は、ゲート端子(GateN)を通して非常にゆっくりと放電する。注入電流ピークをもたらす電流増幅は、大きな電流ミラー比を有する電流ミラー(P4+P5,P3)の使用を通してつくられ、ダイオード(D0,D1)の存在によって強化される。静止モードにおいて、すなわち、負の傾斜を有する急な前部インパルスにより生成された大きな電圧減少が、キャパシタ(C)によって検出され、ゲート端子(GateN)に伝達されると、トランジスタ(P4)は、ダイオード(D1)を通して流れる電流を供給する電流源(CS3)により短絡され、これにより、電流ミラー(P4+P5,P3)は、ずっと低い電流ミラー比を有する電流ミラー(P5,P3)によって仮想的に置き換えられる。その結果、減衰電流源(CS2)の低電流は、電流ミラー(P3,P5)によりミラーリングされる、より低い電流を減衰するのに十分であり、次いで、駆動回路(40)が、スイッチングデバイス(P0)の制御を引き継ぐことを可能にする。最後に、この回路装置は、単方向に動作し、一方で、ゲート制御式スイッチングデバイス(P0)を通して、大きな電流増加を制限するが、大きな電流減少は制限しない。  (もっと読む)

(もっと読む)

定電圧生成回路

【課題】位相補償用のコンデンサを外部に設けなくとも、発振を防止し、安定して正確な定電圧を出力できる定電圧生成回路を提供する。

【解決手段】定電圧生成回路は、出力端子21から出力される出力電流を制御するPMOSトランジスタM1と、該出力電流に比例した比例電流を生成するPMOSトランジスタM2と、出力端子21の電位VOと所定の基準電位VIとを比較し、出力電位VOを基準電位VIに保つようにPMOSトランジスタM1,M2を駆動する比較増幅器3と、出力端子21に一端が接続されたPMOSトランジスタM3と、ノード11に一端が接続されたPMOSトランジスタM4からなる第1のカレントミラーと、PMOSトランジスタM3の他端に一端が接続され他端が接地されたNMOSトランジスタM5と、PMOSトランジスタM4の他端に一端が接続され他端が接地されたNMOSトランジスタM6とからなる第2のカレントミラーとを備える。

(もっと読む)

基準電圧発生回路

【課題】 高温特性と低温特性とを両立し,良好な電圧精度が得られる温度範囲を拡大した基準電圧発生回路を提供すること。

【解決手段】 基準電圧出力部1のバンドギャップ電圧生成部10は,NPNトランジスタQ1,Q2,抵抗R1〜R3により,出力電圧VBGを出力するように構成されている。ここにおいて,NPNトランジスタQ1,Q2に対して,NPNトランジスタQ3,Q4をそれぞれ並列に設けた。そしてそれらのエミッタ側にスイッチSW2,SW3を配置した。また,抵抗R4を抵抗R2に対して直列に配置し,スイッチSW1を抵抗R4に対して並列に配置した。さらに,環境温度により出力信号を変更する温度検出回路2を設けた。これにより,低温時にはNPNトランジスタQ3,Q4,抵抗R4が機能せず,高温時のみこれらが機能するようにした。こうして,高温時と低温時とで温度特性を変え,常時ピーク電圧に近い電圧が出力されるようにした。

(もっと読む)

電力供給制御装置

【課題】 外部回路やパワーFETを保護することが可能な電力供給制御装置を提供する。

【解決手段】 短絡電流Is1が流れ続けると、RC並列回路12が次第に高変換率状態となり、通電時間がt1になったときに、端子電圧Voが閾値電圧Vrを超えてコンパレータ32から異常信号S2が出力される。この異常信号S2を受けて保護用論理回路40のRS−FF66はセット状態となってハイレベルの制御信号S4を出力して、パワーMOSFET15及びセンスMOSFET16に自己復帰不能な遮断動作をさせる。

(もっと読む)

電圧発生回路

【課題】パネルの表示特性に最適な階調電圧を供給し、且つ、消費電力を低減可能な電圧発生回路を提供する。

【解決手段】電圧発生回路は、第1の電源電圧VDDと第2の電源電圧VSSとから第1〜第M(Mは2以上の整数)の分割電圧を生成する電圧分割回路80と、第1〜第Mの分割電圧のインピーダンス変換を行うインピーダンス変換回路IP1〜IP10とを含む。第1〜第K(K<M)のインピーダンス変換回路及び第L(K<L<M)〜第Mのインピーダンス変換回路は、その動作範囲が第1の電源電圧VDDと第2の電源電圧VSSとの間の範囲に設定された第1型の演算増幅器VOPRを含み、第K+1〜第L−1のインピーダンス変換回路は、その動作範囲が第1の電源電圧VDDよりも低い第3の電圧V3と、第1の電源電圧VDDよりも低く第2の電源電圧VSSよりも高い第4の電圧V4との間の範囲に設定された第2型の演算増幅器VOPを含む。

(もっと読む)

1 - 20 / 40

[ Back to top ]