Fターム[5H420NC02]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 基準生成部、出力部以外/全体の構成 (1,615) | 中間部/全体の構成 (531) | カレントミラー回路 (369)

Fターム[5H420NC02]に分類される特許

1 - 20 / 369

半導体集積回路、および、半導体記憶装置

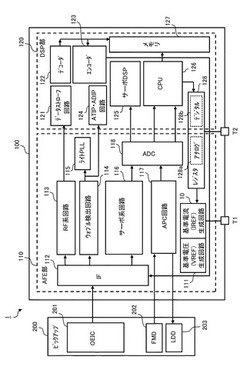

半導体装置、光ディスク装置及び半導体装置のテスト方法

【課題】コストの低減を図りつつ、かつ、精度よく基準電流を生成することが可能な半導体装置、光ディスク装置及び半導体装置のテスト方法を提供する。

【解決手段】半導体装置100は、基準電流を生成する電流生成回路と、記生成された基準電流をテスタ300へ出力する外部端子T1と、基準電流の電流値を制御するための電流制御データを、外部端子T1から出力された基準電流に応じてテスタ300により設定される外部端子T2と、テスタ300により設定された電流制御データにしたがって、電流生成回路により生成される基準電流が所定値となるように調整する電流制御部14と、を備える半導体装置。

(もっと読む)

バンドギャップ参照電源回路および非接触型デバイス

【課題】バンドギャップ参照電源回路の応答を速くすること。

【解決手段】温度係数が正の絶対温度比例電流を生成する絶対温度比例電流生成回路と、前記絶対温度比例電流のミラー電流を生成するミラー電流生成部と、前記ミラー電流に基づいて生成される温度係数が正の絶対温度比例電圧及び係数が負の相補的電圧から温度係数の絶対値が前記絶対温度比例電圧より小さいバンドギャップ参照電圧を生成するバンドギャップ参照電圧生成部とを有し、前記ミラー電流生成部と前記バンドギャップ参照電圧生成部の間の接続ノードから共通の出力ノードに接続され、当該出力ノードから前記バンドギャップ参照電圧を出力する複数のバンドギャップ参照電圧出力回路とを有し、前記複数のバンドギャップ参照電圧出力回路のうちの一部の回路は、前記ミラー電流生成部と前記接続ノードの間及びバンドギャップ参照電圧生成部と前記接続ノードの間それぞれに設けられた1及び第2のスイッチ回路を有すること。

(もっと読む)

定電流回路

【課題】付加する起動回路を小面積とし、高電源電圧でも低消費電流を実現した定電流回路を提供すること。

【解決手段】PNP型のトランジスタQ1,Q2からなる第1のカレントミラー回路と、NPN型のトランジスタQ3,Q4、抵抗R1からなる第2のカレントミラー回路より構成された起動回路において、PNP型のバイポーラトランジスタQ5とN型のJFETトランジスタJ1からなる起動回路を設けた。

(もっと読む)

過電流保護回路及びこれを用いたスイッチング電源装置

【課題】過電流保護値に適切な負の温度特性を持たせる。

【解決手段】過電流保護回路18は、抵抗値の異なる抵抗A1、A2を含む抵抗部Aと、抵抗A1、A2に現れる電圧V1、V2を比較して過電流保護信号S1を生成する比較部Bと、抵抗A1、A2にスイッチ素子12の降下電圧(SW−PGND)を印加する入力部Cと、電流値の等しい電流I1、I2を生成して抵抗A1、A2に供給する電流生成部Dとを有し、電流生成部Dは、抵抗A1、A2と同一の温度特性を有しており、温度特性のフラットな基準電圧BGから基準電流Ixを生成する抵抗D10と;スイッチ素子12と同一の温度特性を有しており、基準電流Ixから基準電圧Vxを生成する抵抗D7と;負の温度特性を有しており、基準電圧Vxから基準電流Iyを生成する抵抗D8と;基準電流Iyから電流I1、I2を生成するカレントミラー(D1〜D4)と;を含む。

(もっと読む)

起動回路

【課題】低消費電流で電源電圧の状態に関係なく安定した動作を確保することができる起動回路を提供する。

【解決手段】本発明は、低電源電位を基準として動作するバイアス回路の電流源(電源電圧VE)と並列に配置されて起動電流を流すためのPチャネルトランジスタMP1と、PチャネルトランジスタMP1のゲートと高電位電源との間に配置された第1のスイッチS1と、PチャネルトランジスタMP1のゲートと低電位電源との間に直列に配置された抵抗R3と第2のスイッチS2と、を備え、第1のスイッチS1は定電流源のバイアス電圧でオン/オフし、第2のスイッチS2はシステム電源の起動に関する電源起動信号でオン/オフする。

(もっと読む)

基準電圧回路及び半導体基板

【課題】電源電位が接地電位に対して変動するハイサイド回路又はローサイド回路において、電源電位の変動の影響を回避し、安定した基準電圧を出力することができる基準電圧回路及び半導体基板を提供する。

【解決手段】本発明は、P型半導体基板20上のNウェル層21内に形成したハイサイド回路中において、Nウェル層21をコレクタとし、Nウェル層21内に形成したP領域23をベースとし、ベースの上層に形成したN領域24をエミッタとし、ハイサイド回路素子22を構成する基板を、コレクタとしてのNウェル層21とで共通化した。

(もっと読む)

定電流回路及び基準電圧回路

【課題】高温時でもエンハンスメント型Nチャネルトランジスタが弱反転状態で動作できる定電流回路を提供する。

【解決手段】カレントミラー回路と定電流生成ブロック回路とオフリーク回路を備えた定電流回路において、オフリーク回路は、ゲートとソースが接地端子に接続され、ドレインが定電流回路の出力に接続される第一のエンハンスメント型Nチャネルトランジスタで構成される。これにより、定電流を生成するエンハンスメント型Nチャネルトランジスタのゲート−ソース間電圧の上昇を抑えることで、弱反転状態での動作を保つ。

(もっと読む)

定電流回路の出力設定装置

【課題】電流値の設定が容易であり、且つ、装置構成を簡素化することが可能な定電流回路の出力設定装置を提供する。

【解決手段】基準電流Irefを流す基準電流発生回路11と、基準電流Irefに比例した電流を流すカレントミラー回路を少なくとも一つ備えた、4個のカレントミラー回路群、即ち、第1〜第4のカレントミラー回路群21〜24を備える。そして、各カレントミラー回路群21〜24は、それぞれ、基準電流Irefに対してα倍、2α倍、4α倍、8α倍となる電流を出力する。そして、各カレントミラー回路群を適宜選択して負荷に接続することにより、該負荷に供給する電流値が所望の電流値となるように設定することが可能となる。このため、操作性を容易とし、且つ、装置構成を簡素化することが可能となる。

(もっと読む)

基準電圧回路

【課題】出力電圧における温度補償をする際の抵抗のばらつきの影響を低減する。

【解決手段】基準電圧(Vref)を生成して出力端から出力するバンドギャップリファレンス回路(1)と、基準電圧の分割電圧(ノードAの電圧)とダイオード(36)の順方向電圧との差電圧に応じて差電圧を電流に変換する電圧電流変換回路(3に相当)と、を備え、電圧電流変換回路は、変換された電流(19)を出力端にフィードバックする。

(もっと読む)

過電流検出回路

【課題】温度変化の影響を受けにくい過電流検出回路を提供する。

【解決手段】ダイオード列55を設け、ダイオード列55のアノード端をデプレッション型トランジスタDNM1のソース端子に接続するとともに、ダイオード列55のカソード端とデプレッション型トランジスタDNM1の基板を基準電位に接続する。ダイオード列55を構成する各ダイオードの順方向電圧をVf、ダイオード列55を構成するダイオードの数をm(mは1以上の整数)とすると、デプレッション型トランジスタDNM1の基板バイアス電圧Vbは、Vb=m×Vfとなる。ダイオードの順方向電圧Vfは負の温度係数をもつから、基板バイアス電圧Vbも負の温度係数をもつ。これにより閾値電圧に負の温度係数をもたせて、ドレイン電流IDの温度特性と相殺させる。

(もっと読む)

基準電圧発生回路

【課題】高温環境下又は低温環境下であっても温度依存性を効果的に抑制し得る基準電圧発生回路をより簡易に実現する。

【解決手段】基準電圧発生回路1は、基準電圧Vrefを生成すると共に、環境温度が所定の温度範囲のときに環境温度が上昇するにつれて基準電圧Vrefが減少側に変化しようとする特性を有する基準電圧回路3と、ダイオードVf1(基準素子)の特性の変化に基づいて素子温度に応じた出力が生成される温度検知部4と、温度検知部4からの出力に基づいて基準電圧Vrefを補正する基準電圧補正部5とを備えている。そして、基準電圧補正部5は、環境温度が所定の温度範囲のときに、環境温度が上昇するほど、その上昇に応じて基準電圧Vrefが減少側に変化することを抑制する量を大きくするように、温度検知部4からの出力に基づいて基準電圧回路3における所定電流経路の電流量を変化させている。

(もっと読む)

スイッチング電源回路

【課題】バイパス容量の容量値を大きくすることなく、供給電流の変動を抑制する。

【解決手段】負荷の状態に応じて予め設定したピースワイズリニア信号に基づき、負荷が重負荷のとき所定の電流値、軽負荷のとき零となり、重負荷と軽負荷との間で切り替わるとき前記所定の電流値と零との間で線形に変化する電流Im12を入力電圧Vinから生成する。また、前記ピースワイズリニア信号に基づき、負荷が前記重負荷のとき零、前記軽負荷であるとき前記所定の電流値となり、重負荷と軽負荷との間で切り替わるとき零と前記所定の電流値との間で線形に変化する電流Im13を出力電圧Voutから生成する。前記電流Im12と前記電流Im13との和を供給電流Isup1とし、これを制御回路Ctrl1に供給する。

(もっと読む)

基準電圧回路

【課題】プロセス変動によるバラつき要因が少ない基準電圧回路の提供。

【解決手段】第1のMOSトランジスタと、ゲート端子が第1のMOSトランジスタのゲート端子に接続され、第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、第1のMOSトランジスタと第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、カレントミラー回路の電流を流す第3のMOSトランジスタと、第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、カレントミラー回路の電流を流す第4のMOSトランジスタを備え、第3のMOSトランジスタと第4のMOSトランジスタのしきい値の絶対値とK値の差に基づく定電圧を基準電圧として出力する、構成とした。

(もっと読む)

半導体集積回路

【課題】クランプ電圧を正確な値に設定できる半導体集積回路を提供することを目的とする。

【解決手段】第1の電圧である電源を供給されて定電流を発生する定電流部60と、定電流部60で発生された定電流を供給されて第1の電圧より低い第2の電圧を発生し、第1の電圧の電源を第2の電圧にクランプするクランプ部71と、クランプ部71でクランプされた電源を供給されて基準電圧を発生する基準電圧発生部72とを有し、クランプ部71は、ゲートとドレインに接続され縦型接続された複数段のMOSトランジスタM11−1〜M11−nである。

(もっと読む)

電圧発生回路、定電圧回路および電圧発生回路の電流検出方法

【課題】低消費電流で低電圧な定電圧を安定して得られる定電圧回路を提供すること。

【解決手段】定電圧回路Aは、閾値電圧が極小でゲート長が特大のMOSトランジスタN1を用いて低電流を作り出し、基準電圧VREFを発生するMOSトランジスタN2、これと対を成してカレントミラー回路を構成する各MOSトランジスタN3、N4、N7、及びその他の各MOSトランジスタN5、N6の何れについても低閾値電圧タイプとし、且つMOSトランジスタN2、N3、N4、N7のゲート長LをMOSトランジスタP1、P2のゲート長Lよりも増大させている。これにより、各MOSトランジスタN2〜N7のドレイン電極−ソース電極間の電圧Vdsが0.1V以上の飽和領域で動作する電圧値を保ち、所望の低い基準電圧VREFを発生でき、カレントミラー回路を構成する際に正常動作が可能となり、定電圧出力端子4から低消費電流で低電圧な定電圧が得られる。

(もっと読む)

基準電圧回路

【課題】温度依存性が少ない低電圧(1.25V以下)の定電圧を発生する、基準電圧回路を提供すること。

【解決手段】二つのPN接合を有し、いずれかのPN接合に基づいた電圧Vkと、二つのPN接合の電圧の差に基づいた電流Ikと、を出力するバンドギャップ電圧発生回路と、電圧Vkを分圧する分圧回路と、を備え、分圧回路は入力する電流Ikにより分圧電圧を補正して、基準電圧として出力する、構成とした。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

電圧生成回路およびパワーオンリセット回路

【課題】電源電圧が一時的に低下した場合であっても、その後電源電圧が上昇すれば基準電圧を素早く出力できるようにした電圧生成回路、および、リセット信号を素早く出力できるようにしたパワーオンリセット回路を提供する。

【解決手段】トランジスタMP5およびMP6が第1電源線N1およびノードN6間に直列接続されている。トランジスタMP5が起動電流Isをセンシングし、トランジスタMP6が基準電流Ipをセンシングする。電源電圧VDDが低下したとしても、両トランジスタMP5およびMP6には閾値電圧以上となる電圧がゲートソース間に与えられる虞がなくなり、充電回路8には充電電流Ioが充電されにくくなる。したがって、電源電圧VDDが再復帰して電源電圧が上昇したときには、トランジスタMP4が起動電流IsをノードN5に素早く供給でき、電流生成回路6は基準電流Ipを素早く生成できる。

(もっと読む)

バンドギャップ基準電圧回路及びこれを用いたパワーオンリセット回路

【課題】バンドギャップ基準電圧回路100を確実に起動させることができる。

【解決手段】電源電圧がpMOSトランジスタP1のゲート電圧の閾値に到達する前には、pMOSトランジスタP6により電源VddとpMOSトランジスタP4のソース端子との間を開放させている。このため、電源電圧がpMOSトランジスタP1のゲート電圧の閾値に到達する前に、抵抗素子R3aによってコンデンサC1から電荷を放出させて、コンデンサC1のプラス電極の電位をpMOSトランジスタP4のゲート端子の電位の閾値よりも低くすることができる。電源電圧が上昇してpMOSトランジスタP6が電源VddとpMOSトランジスタP4のソース端子との間を接続すると、pMOSトランジスタP4がオンして、電源VddからpMOSトランジスタP6、P4を通してスタートアップ電流をnMOSトランジスタN1、N2のゲート端子に流すことができる。

(もっと読む)

1 - 20 / 369

[ Back to top ]