Fターム[5H730AA10]の内容

DC−DCコンバータ (106,849) | 目的 (10,886) | スイッチング速度の向上、高周波化 (133)

Fターム[5H730AA10]に分類される特許

41 - 60 / 133

スイッチングレギュレータ

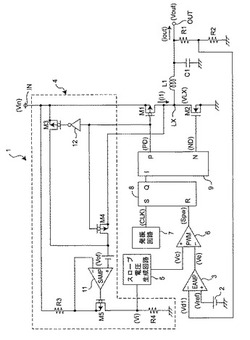

【課題】スイッチング周波数の高周波化を図ることができる電流モード制御方式のスイッチングレギュレータを得る。

【解決手段】演算増幅回路からなるセンスアンプ11は、反転入力端の電圧が入力電圧VinよりもオフセットVof分だけ小さくなるように動作するため、PMOSトランジスタM5がオフせずに、入力電圧Vinと接地電圧との間に直列に接続された抵抗R3、PMOSトランジスタM5及び抵抗R4にオフセットVofに応じた電流を流すようにし、このような状態からスイッチングトランジスタM1がオンし、電流センス回路4が電流検出を開始すると、すでにPMOSトランジスタM5がオンしているため、スイッチングトランジスタM1に流れる電流i1の立ち上がりに追従して電流センス回路4の出力電圧Viも上昇するようにした。

(もっと読む)

DC/DCコンバータ装置

【課題】同期スイッチング制御においてDC/DCコンバータ装置の制御性を向上させるDC/DCコンバータ装置を提供する。

【解決手段】DC/DCコンバータ装置50のコンバータ制御部48は、各スイッチング周期全体において、DC/DCコンバータ装置50が降圧状態のみである場合と判断したとき、昇圧用スイッチング素子82に対する駆動信号ULの出力期間にデッドタイムdtを全て割り付け、昇圧状態のみである場合と判断したとき、降圧用スイッチング素子81に対する駆動信号UHの出力期間にデッドタイムdtを全て割り付け、降圧状態及び昇圧状態の両方が現れる場合と判断したとき、駆動信号UH、ULそれぞれの出力期間にデッドタイムdtを割り付ける。

(もっと読む)

半導体装置及び電力変換装置

【課題】静電容量と抵抗の値が異なる複数のスナバ回路を用意する必要がなく、且つ逆バイアス時に還流ダイオードに発生する振動現象の収束時間を短縮できる半導体装置及び電力変換装置を提供する。

【解決手段】アノード端子300とカソード端子400からなる一対の接続端子と、一対の接続端子間に接続されたユニポーラ動作する還流ダイオード100と、一対の接続端子間に還流ダイオード100と並列接続され、少なくともキャパシタ210と抵抗220を含む半導体スナバ回路200と備え、半導体スナバ回路200のキャパシタ210と抵抗220の値が可変である。

(もっと読む)

電源装置、およびその駆動方法、電源装置を備えた光源装置、電子機器

【課題】負荷追従性と回路効率とを両立した電源装置を提供すること。

【解決手段】電源装置100は、AC/DC回路5、DC/DCコンバーター1、検出回路2、デジタルIC101、ゲートドライバー106などから構成されている。また、デジタルIC101のメモリー104には、複数の駆動周波数ごとに位相を補償するための制御式が記憶されている。電源装置100によれば、起動時には駆動周波数の高い駆動信号で駆動することによって素早く目標電圧を得ることができる。また、目標電圧に達した後は、駆動周波数の低い駆動信号に切り替えることによって回路効率を高めることができる。

(もっと読む)

パルス電源

【課題】負荷条件や動作条件の変更にも、キックバックエネルギーの回生処理を確実にし、しかもパルス発生の高速化を図ることができる。

【解決手段】磁気圧縮回路300A,300Bは、二段構成とし、それぞれにはピーキングコンデンサCPと初段コンデンサC1,C2との間にパルストランスTR1,TR2を設け、電流検出器CT1,CT2が可飽和リアクトルSR1,SR3の電流検出値から検出し、半導体スイッチIGBT1,IGBT2のオフ制御を行うことで、負荷400からのキックバックエネルギーを初段コンデンサに直接に回生させる。

また、このオフ制御に、可飽和リアクトルの電圧または初段コンデンサの電圧から判定、または初段コンデンサの電圧と可飽和リアクトルのVt積から判定する。パルストランスの一方の巻線のダイオードD2,D4を省く構成も含む。

(もっと読む)

DC/DCコンバータ装置

【課題】同期スイッチング制御においてDC/DCコンバータ装置の制御性を向上させるDC/DCコンバータ装置を提供する。

【解決手段】演算部120は、各スイッチング周期Tsw全体においてDC/DCコンバータ装置50が降圧状態のみである場合と判断したとき、駆動デューティに基づいて決定される降圧用スイッチング素子81の駆動期間が、実際に降圧用スイッチング素子81を駆動させたい期間にデッドタイムdt分の期間を付加した期間となるように駆動デューティを設定し、各スイッチング周期Tsw全体においてDC/DCコンバータ装置50が昇圧状態のみである場合と判断したとき、駆動デューティに基づいて決定される昇圧用スイッチング素子82の駆動期間が、実際に昇圧用スイッチング素子82を駆動させたい期間にデッドタイムdt分の期間を付加した期間となるように駆動デューティを設定する。

(もっと読む)

DC−DCコンバータの制御回路、DC−DCコンバータ及び電子機器

【課題】応答特性を向上することができるDC−DCコンバータの制御回路、DC−DCコンバータ及び電子機器を提供すること。

【解決手段】発振器20は、第1の周波数の基本クロック信号Ckを分周回路21を介して分周して、第2の周波数の分周クロック信号Ckdとしてデジタル回路22に出力する。また、発振器20は、基本クロック信号Ckに同期した同じ第1の周波数の三角波信号Stをアナログ回路23に出力する。デジタル回路22は、出力電圧Voに基づいて、分周クロック信号Ckdに同期してPID制御する。アナログ回路23は、制御信号Sc及び三角波信号Stに基づいてPWM制御してスイッチング回路14のスイッチング動作を制御する。

(もっと読む)

画像形成装置

【課題】 トランスをスイッチングすることで得られる高電圧を印加して画像形成する装置において、

紙間での高圧出力切換等を想定した、切換速度が速い高圧回路を備えた画像形成装置を提供することである。

【解決手段】 出力切換時には目標出力を想定した固定パルスでトランスを駆動し、通常時には出力検出結果に基づいたフィードバック制御を行い、

また、切換時に使う固定パルスは環境状態と装置の稼働状態に応じて自動で切換わることにより、装置の状態に基づいた最適な高速切換ができるようにした。

(もっと読む)

スイッチングレギュレータ

【課題】出力電流の急増時にも出力電圧の低下を抑制することができるスイッチングレギュレータを提供する。

【解決手段】誤差増幅器AMP1は、電流源I1の電流値を誤差電圧に比例するように制御する。A/D変換回路14は、スイッチングレギュレータの出力電流値をデジタル電流値に変換する。分周制御回路13は、分周回路12が分周する基準クロックの分周比をデジタル電流値が高いほど低くなるように制御する。電流比較器CMP1は、電流源I1 の電流値の所定数(R1/R2)倍に対して、トランジスタQ1のコレクタ電流が上回るとフリップフロップFFのリセット信号を出力する。フリップフロップFFは、分周回路12の出力でセットされ、電流比較器CMP1の出力でリセットされる。トランジスタQ1は、フリップフロップFFの出力Qに対応してオン/オフする。

(もっと読む)

バッテリー充電器

【課題】垂下特性を得られるようにして充電時間を短縮する。

【解決手段】スイッチング用MOSFET30のゲート端子Gに接続されたシャント用トランジスタ40のトリガ回路SLのコンデンサC4を、前記FET30のドレイン電流を検出する電流検出抵抗R4と接続する。こうして、トリガ回路SLを構成するコンデンサC4を充電する電圧がドレイン電流Idの増加で持ち上がり、前記シャント用トランジスタ40が速くONするようにして、前記FETのON時間を短くする。そして、二次側出力電圧の低下に伴う出力(充電)電流の増加分を規制することで、垂下特性を得られるようにして充電時間を短縮する。

(もっと読む)

単方向金属酸化膜半導体電界効果トランジスターとその応用

【課題】単方向金属酸化膜半導体電界効果トランジスターとその応用を提供する。

【解決手段】本発明は、金属酸化膜半導体電界効果トランジスター(MOS)、電流検出回路、および、快速ターンオフ回路、からなる単方向金属酸化膜半導体電界効果トランジスター(UMOS)を提供する。電流検出回路は、MOSを流れる電流の方向を検出する。順方向電流が検出される時、快速ターンオフ回路は機能せず、MOSのチャネルが形成される。逆電流が検出される時、快速ターンオフ回路は有効で、MOSのチャネルは形成されない。このUMOSは、同期整流器に応用されて(これに限定されるものではない)、逆電流、又は、シュートスルー電流を検出することができ、快速的にMOSのチャネルをオフにすることができる。

(もっと読む)

スイッチング電源回路の制御回路

【課題】 軽負荷における制御の応答性を向上させると同時に重負荷時における制御の安定性を実現し得るスイッチング電源回路の制御回路を提供する。

【解決手段】 負荷電流IOUTが相対的に小さい軽負荷モードと、相対的に大きい重負荷モードの2種類の負荷モードの何れかで駆動されるスイッチング電源回路の制御回路であって、エラーアンプ1の位相補償用のコンデンサC1と、スイッチング素子SW1を介してコンデンサC1と並列に接続されたコンデンサC2と、コンデンサC2のチャージ電圧がコンデンサC1のチャージ電圧に等しくなるように調整する電圧調整手段Iと、軽負荷モード乃至重負荷モードの何れであるかを検出し、軽負荷モードの時にはスイッチング素子SW1をオフしてコンデンサC1による位相補償を行わせる一方、重負荷モードの時にはスイッチング素子SW1をオンしてコンデンサC1とコンデンサC2とによる位相補償を行わせる状態判定回路8とを有する。

(もっと読む)

ゲート駆動回路

【課題】部品点数が少ない回路構成で、制御用電源電圧よりもオン電圧が高いパワートランジスタを確実に駆動することのできるゲート駆動回路を提供すること。

【解決手段】ゲート駆動回路10は、ダイオード21とコンデンサ22とを備えたチャージポンプ回路20で入力信号を昇圧することによりスイッチング素子1のゲートを駆動する。ゲート駆動回路10は、ダイオード21のカソードとコンデンサ22の一端とを直列接続し、コンデンサ22の他端から入力されるパルス信号Pinを、ダイオード21のアノードに入力された制御電源Vinの電圧値だけオフセットしたオフセットパルス信号を出力するチャージポンプ回路20と、ダイオード21およびコンデンサ22の接続点とスイッチング素子1との間に配設され、パルス信号Pinに同期して開閉動作することでオフセットパルス信号を昇圧パルス信号に変換する第1スイッチ30と、を備える。

(もっと読む)

昇降圧コンバータの駆動制御装置

【課題】昇圧動作と降圧動作の切替点付近における応答性の向上と、充電領域及び放電領域における良好な制御性の確保との両立を図った昇降圧コンバータの駆動制御装置を提供することを課題とする。

【解決手段】昇降圧コンバータの駆動制御装置は、蓄電器と、力行運転及び回生運転の双方を行う負荷との間に接続され、前記蓄電器の充放電制御を行う昇降圧コンバータの駆動制御装置であって、前記負荷と前記昇降圧コンバータとの間のDCバスの電圧値と目標電圧値との偏差に基づくPI制御により、前記昇降圧コンバータを駆動するためのPWMデューティ値を演算するPWMデューティ演算部と、該演算されたPWMデューティ値に対応して、第1及び第2ゲインを切り替えて設定するゲイン設定部とを含む。

(もっと読む)

スイッチングレギュレータおよび電子機器

【課題】 供給される電源の電圧が低電圧の状態から上昇し、スイッチング動作を開始するときの移行時間を短縮することができるスイッチングレギュレータおよび電子機器を提供する。

【解決手段】 スイッチングレギュレータ1は、電源電圧VBが基準電圧源102の電圧以下になったとき、電流源25が誤差増幅器22に供給する動作電流を増加する。電源電圧VBが上昇し、基準電圧源102の電圧になったとき、低電圧時MOSオン回路10によるMOSFET15の強制的オンは停止される。MOSFET915がオフになると、出力端子19の電圧Voutは低下する。出力端子19の電圧Voutが低下し、抵抗素子20,21によって分圧された電圧が、基準電圧入力端子24に入力される電圧になると、動作電流が増加されている誤差増幅器22の出力電圧Verrは、動作電流が増加されていないときよりも速く上昇する。

(もっと読む)

降圧型スイッチングレギュレータ

【課題】高電圧入力が可能で、しかもチップ面積を小さくすることができ、応答速度も速くすることができる降圧型スイッチングレギュレータを得る。

【解決手段】スイッチングトランジスタM1のオン/オフ制御を行う第1ドライブ回路3及び同期整流用トランジスタM2のオン/オフ制御を行う第2ドライブ回路4の各正側電源入力端にダイオードD1を介して第1電源回路5からの電源電圧VLをそれぞれ入力すると共に、第1ドライブ回路3の負側電源入力端を接続部LXに、第2ドライブ回路4の負側電源入力端を接地電圧にそれぞれ接続し、更に第1ドライブ回路3及び第2ドライブ回路4の各正側電源入力端と接続部LXとの間にブートストラップコンデンサC1を接続するようにした。

(もっと読む)

半導体装置及びDC−DCコンバータ

【課題】ターンオフ時のソースドレイン電圧の跳ね上がりを抑えることができる半導体装置及びこの半導体装置を用いたDC−DCコンバータを提供する。

【解決手段】半導体装置1において、MOSFET領域AMOSFETにトレンチ16を形成し、その内部にトレンチゲート電極18を埋設する。また、キャパシタ領域ACapacitorにトレンチ26を形成し、その内部にトレンチソース電極28を埋設する。トレンチソース電極28の形状はストライプ状であり、その長手方向の一部分を介して、ソース電極21に接続されている。

(もっと読む)

スイッチングレギュレータ

【課題】本発明は、入力変動や負荷変動に伴う出力変動を抑えつつ、高速動作が可能なスイッチングレギュレータを提供することを目的とする。

【解決手段】本発明に係るスイッチングレギュレータにおいて、DC−DCコンバータのスイッチング素子3、4をオン/オフ制御するための制御信号VQを生成して、これをドライバ論理回路2に出力する制御信号生成回路1は、出力電圧VOと基準電圧VREFを比較する比較器10と、比較器10の出力によってセットされるフリップフロップ12と、フリップフロップ12がセットされてから所定のオン期間が経過するとフリップフロップ12をリセットするパルス制御回路13と、出力電圧VOをモニタし、その電圧レベルが所望の目標電圧VTARGETと一致するように、基準電圧VREFを可変制御する基準電圧制御回路14(アンプAMP2)と、を有して成る。

(もっと読む)

チャージポンプ昇圧回路

【課題】一般にチャージポンプ昇圧回路は駆動電源として昇圧電圧自体を用いるため、停止状態から昇圧動作を起動するときには、必要な駆動電位を昇圧出力端子に供給する必要がある。従来は、チャージポンプ昇圧回路を短時間に起動できないという課題があった。

【解決手段】本発明のチャージポンプ昇圧回路は、昇圧動作を停止しているときなどに昇圧出力端子に所定の電源電位供給しておくスイッチ手段を設けており、昇圧出力端子に所定の電源電位を予め供給しておくから、チャージポンプ昇圧回路を短時間に起動することができる。

(もっと読む)

チャージポンプ回路

【課題】昇圧時間を短縮させるとともに、最終的に得られる昇圧電圧の低下を防止することができるチャージポンプ回路を提供する。

【解決手段】昇圧動作の開始前に、初期充電用の整流素子3およびトランジスタ4を介して容量素子1を初期充電する。昇圧動作の開始後には、初期充電用のトランジスタ4のゲートに電源電圧より高い電圧が印加されるので、初期充電用のトランジスタ4のオフリーク電流が減少する。この結果、最終的に得られる昇圧電圧の低下を防止することができる。

(もっと読む)

41 - 60 / 133

[ Back to top ]