Fターム[5H730DD28]の内容

DC−DCコンバータ (106,849) | スイッチング部(主変換部の) (10,397) | スイッチング素子の駆動 (812) | 駆動トランジスタの使用 (661) | 2石以上 (88)

Fターム[5H730DD28]に分類される特許

1 - 20 / 88

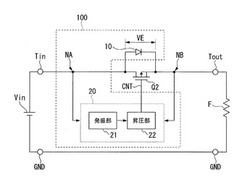

スイッチ素子駆動回路

【課題】グランド端子からグランド電位の供給を受けることなく、スイッチ素子をオン状態に維持することを可能とするスイッチ素子駆動回路を提供する。

【解決手段】本発明によるスイッチ素子駆動回路(100)は、電源と負荷との間に接続されたスイッチ素子を駆動するためのスイッチ素子駆動回路であって、前記電源と前記負荷との間に設けられた電圧降下素子(10)と、前記電圧降下素子の端子間に発生する電圧を動作電源として該電圧を昇圧し、該昇圧により得られた電圧から前記スイッチ素子を制御するための制御信号を生成する信号生成部(20)とを備える。

(もっと読む)

電源回路

【課題】主スイッチング素子の面積を大きくすることなく、ゲートの容量に蓄積された電荷を引き抜く引き抜き期間を短くすることができる電源回路を提供する。

【解決手段】Nチャネル型の主スイッチング素子10と、主スイッチング素子10を制御する駆動回路30と、主スイッチング素子10の第2電極端子に接続される負バイアス回路20とを備える。そして、負バイアス回路20を、接地された第1抵抗21と、当該第1抵抗21と第2電極端子との間に配置されて第2電極端子との接続点の電位を第1抵抗21との接続点の電位より低くする電位降下手段22、23とを有するものとする。また、駆動回路30を第1抵抗21と電位降下手段22、23との接続点に接続する。そして、主スイッチング素子10がオフされたとき、ゲートの容量に蓄積された電荷を駆動回路30および第1抵抗21と電位降下手段22、23との接続点を介して引き抜くようにする。

(もっと読む)

電源装置の駆動回路及び電源装置

【課題】遷移期間においてハイサイドトランジスタQ1がオンしないようにする。

【解決手段】高電位電源ラインと低電位電源ラインとの間に直列に接続されたハイサイドトランジスタとロウサイドトランジスタと,両トランジスタの接続ノードと出力端子との間に設けられたインダクタとを有する電源装置の前記両トランジスタを駆動する駆動回路であって,前記ハイサイドトランジスタのゲートを駆動する第1のゲートドライバと,前記ロウサイドトランジスタのゲートを駆動する第2のゲートドライバとを有し,前記ハイサイドトランジスタがオンでロウサイドトランジスタがオフの第1の状態から,前記ハイサイドトランジスタがオフでロウサイドトランジスタがオンの第2の状態に遷移する遷移期間で,前記第1のゲートドライバは前記ハイサイドトランジスタのゲートを前記低電位電源ラインの電位より低い第1の電圧に駆動する電源装置の駆動回路。

(もっと読む)

スイッチングレギュレータの制御回路、スイッチングレギュレータおよび電子機器、スイッチング電源装置、テレビ

【課題】搭載されるセットごとに効率とEMIのバランスを最適化可能なスイッチングレギュレータを提供する。

【解決手段】ハイサイド可変電流源22およびハイサイドトランジスタM2は、制御回路100の電源端子PVDDとスイッチングトランジスタM1のゲートとの間に直列に設けられる。ローサイド可変電流源24およびローサイドトランジスタM3は、スイッチングトランジスタM1のゲートと接地端子の間に直列に設けられる。スルーレート制御部30は、設定端子ADJの状態に応じて、ハイサイド可変電流源22およびローサイド可変電流源24の少なくとも一方の電流値を制御する。

(もっと読む)

トランジスタ駆動回路

【課題】より簡単な構成で、出力トランジスタを確実にオフ状態に維持できるトランジスタ駆動回路を提供する。

【解決手段】NチャネルMOSFET5とコイル2との共通接続点;出力端子OUTとグランドとの間にフライホイールダイオード3を接続する。FET5のゲートには、NPNトランジスタ6及びPNPトランジスタ7のプッシュプル回路により制御信号を出力し、トランジスタ7のベースとグランドとの間にNPNトランジスタ11を接続し、トランジスタ11のベースとグランドとの間にNチャネルMOSFET14を接続して、FET14にPWM信号を入力する。ダイオード13は、FET14がオフ状態になるとトランジスタ11のベースにベース電流を供給し、ダイオード15をダイオード13のアノードとトランジスタ6及び7のベースとの間に接続する。NPNトランジスタ22をFET5のゲートと出力端子との間に接続し、トランジスタ22をPWM信号に応じてFET5がオフする際にオンさせる。

(もっと読む)

スイッチング電源装置

【課題】低圧用のトランスを用い入力直流電圧の大きさに関係なく各スイッチング素子を動作できるスイッチング電源装置。

【解決手段】スイッチング素子Q11(Q12)のスイッチング状態に応じた第1(第2)パルス信号を出力するパルス発生回路を有し、第1パルス信号が印加される第1直列共振回路L1,C1に第1パルス信号に対して90°位相の遅れた電流が流れ、第1直列共振回路の電流でスイッチング素子Q21をオン/オフさせ、第2パルス信号が印加される第2直列共振回路L2,C2に第2パルス信号に対して90°位相の遅れた電流が流れ、第2直列共振回路の電流でスイッチング素子Q22をオン/オフさせるので、第2コンバータ4が第1コンバータ3に対して90°位相がずれた動作となり、パルス発生回路は第1パルス信号を出力する二次巻線Na3と第2パルス信号を出力する二次巻線Na4とを有しスイッチング素子Q11,Q12の駆動信号に同期した電圧が印加される第3トランスT3を有する。

(もっと読む)

スイッチング回路

【課題】スイッチング素子の動作に起因するノイズの大きさが低減された、小型で製造コストの低いスイッチング回路を提供する。

【解決手段】スイッチング素子と、一定周期でパルス波のドライバ信号を出力するドライバ信号出力回路と、ドライバ信号のパルス波の周期を複数含む一定期間内において駆動力を変化させながら、ドライバ信号の周期に同期してスイッチング素子を駆動する駆動回路とを備える。

(もっと読む)

直流電源装置

【課題】ワイドバンドギャップ半導体を用いたFETを使用した、非常に大きな電力を直流に変換する直流電源装置において、1つの駆動電源にて各FETに正と負の駆動電圧を与えることで、低価格で小型かつ高効率の直流電源装置を得る。

【解決手段】入力段に突入電流保護回路1を有し、各FET3〜6に対し独立した駆動回路D3〜D6を有する。高電圧側のFET3、5をドライブトランス14により駆動し、低電圧側のFET4、6においては、駆動電源17およびFET4、6に流れる電流で充電される負バイアス用コンデンサ24によりゲート電圧を供給可能に構成する。

(もっと読む)

照明装置

【課題】オンデューティが制限されず、エネルギ損失の少ない降圧動作を実現するLED照明装置が提供する。

【解決手段】一実施形態に係る照明装置は、降圧チョッパ方式の回路を用いてLEDを点灯する照明装置であって、交流電圧を変換して得られる直流電源に接続される第1スイッチ素子と;カソードが前記直流電源のグランドに接続されるLEDのアノードと前記第1スイッチ素子の間に接続される降圧用コイルと;前記第1スイッチ素子のオン/オフを制御するドライバICとを具備する。

(もっと読む)

力率改善回路およびその制御回路、それらを用いた電子機器

【課題】PFC回路の温度特性の改善にある。

【解決手段】第1V/I変換回路10は、PFC回路200に入力される全波整流波形を有する交流電圧VACに応じた第1電圧V1を、第1抵抗R1に印加することにより第1電流I1を生成する。第1誤差増幅回路18は、PFC回路200の出力電圧VDCに応じた第1検出電圧VSと所定の基準電圧VREFとの誤差を増幅し、第2電圧V2を生成する。第2V/I変換回路12は、第2電圧V2を第2抵抗R2に印加することにより第2電流I2を生成する。第3V/I変換回路14は、所定の電圧VBGRを第3抵抗R3に印加することにより第3電流I3を生成する。乗算器20は、第1電流I1と第2電流I2を乗算し、第3電流I3により除算した第4電流I4を生成し、第4電流I4を第4抵抗R4に流すことにより、第4電圧V4を生成する。

(もっと読む)

スイッチング電源及び画像形成装置

【課題】 スイッチング電源の一次側の電流検出抵抗によって生じる逆起電力によりスイッチング素子が発熱する。

【解決手段】 スイッチング手段に接続され、スイッチング手段に流れる電流を検出する電流検出抵抗に並列に接続され、電流検出抵抗によって生じるスイッチング手段の発熱を低減するスイッチング電源。

(もっと読む)

ゲート駆動回路及びスイッチング電源装置

【課題】コンデンサの容量を小さくでき安価にIC化できるゲート駆動回路。

【解決手段】直流電源V1の正極に起動抵抗R1を介して一端が接続された第1コンデンサC1と、第1電極と第2電極と第1制御電極とを有し第1コンデンサの一端に第1電極が接続され第2電極が直流電源の負極であるグランドに接続された第1スイッチQ3と、第3電極と第4電極と第2制御電極とを有し第3電極が第1スイッチの第2電極と直流電源の負極であるグランドに接続され第4電極が第1コンデンサの他端に接続された第2スイッチQ4と、第2スイッチの第3電極と第4電極とに並列に接続され一端が直流電源の負極であるグランドに接続された第2コンデンサC2と、パルス信号に基づきスイッチング素子のターンオフ時にスイッチング素子のゲートを第1コンデンサの他端及び第2コンデンサの他端に接続することによりスイッチング素子のゲートを負電圧にさせる負電圧制御部Q1,Q2とを有する。

(もっと読む)

電力供給回路及び該回路を備えた機器

【課題】 デバイスや回路の電気的状態を判定する電力供給回路、及びその回路を備えた機器を提供する。

【解決手段】 デバイスへ電力供給を行う電力供給回路であって、前記デバイスへ電力を供給する電力供給ラインに接続されたコンデンサと、前記電力供給ラインへ第1電圧を供給する電圧を生成する第1電圧生成手段と、前記第1電圧より低い第2電圧を生成し、前記第2電圧を前記電力供給ラインへ供給する第2電圧生成手段と、前記第2電圧生成回路へ電圧生成の開始指示を出力し、前記電力供給ラインの電圧と閾値電圧とを比較を行い、前記電力供給ラインの電圧が閾値電圧より高ければ前記第1電圧生成回路へ電圧生成の開始指示を出力し、前記出力部の電圧が閾値電圧より低ければ前記第1電圧生成回路へ電圧生成の停止指示を出力する制御を行う。

(もっと読む)

DC/DCコンバータ用半導体装置

【課題】半導体装置の電源電圧の変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

スイッチングレギュレータ

【課題】 小型・低雑音のスイッチングレギュレータを提供する。

【解決手段】 導通、遮断の2状態が交互に切り替わる複数のトランジスタで構成されたスイッチングレギュレータの出力段と、その出力段トランジスタを各々個別に駆動するための駆動回路から構成され、当該駆動回路は、各々出力段トランジスタにおける遮断から導通状態への遷移時間が、導通から遮断状態への遷移時間に比べて長くなるように立ち上がり、立ち下がり時の駆動能力をアンバランスに設定され、各々の遷移時間は、出力信号の電位があらかじめ設定された電位に達したことを判定して変化させることを特徴とするスイッチングレギュレータとして構成される。

(もっと読む)

コンバータの制御回路

【課題】高効率且つ低ノイズを実現するコンバータの制御回路を提供する。

【解決手段】実施形態によれば、コンバータの制御回路は、ハイサイドスイッチング素子のゲートに接続されハイサイドスイッチング素子のゲートを駆動するドライブ回路と、ドライブ回路と並列にハイサイドスイッチング素子のゲートに接続されたドライブスイッチと、ドライブスイッチに制御信号を供給してドライブスイッチをオンオフするドライブスイッチ制御回路とを備えている。ハイサイドスイッチング素子がドライブ回路によって駆動されている期間中、ハイサイドスイッチング素子のゲート電圧が所定の閾値に達すると、ドライブスイッチ制御回路はドライブスイッチに制御信号を供給してドライブスイッチをオンからオフに切り替える。

(もっと読む)

電力変換回路の制御装置

【課題】パワースイッチング素子Siのオン・オフ操作の繰り返しによってコイルを流れる電流の絶対値を増減させることで直流電源の電圧を変換して出力するに際し、オンすべき期間が短い場合に、オン時間の制御性が低下すること。

【解決手段】パワースイッチング素子Siのゲートには、コンデンサ58の電圧が印加される。コンデンサ58の電圧は、パワースイッチング素子Siを今回オン操作するに先立ち、今回のオン操作期間に流れる電流の最大値を予測し、この予測値が閾値以上であるか否かに応じて可変設定される。

(もっと読む)

スイッチングレギュレータ

【課題】大きなチップ面積を必要とせず、入力電力変換効率の高効率化を図ることができるスイッチングレギュレータを得る。

【解決手段】負荷10が軽負荷状態である場合は、コンバータ部2のみでスイッチング動作を行い、軽負荷条件における効率を高い状態に保つことができ、負荷10が重負荷状態である場合は、コンバータ部2に加えてコンバータ部3でもスイッチング動作を行わせて、重負荷条件における効率も高い状態にすることができるようにし、2つのコンバータ部2,3と、出力スイッチ制御回路部4と、コンバータ選択制御端子DRVSELを1チップに集約して、負荷電流の大きさを検出する回路等を備えていないため、チップ面積を増加させることなく、ユーザーに提供しやすいチップ面積を実現することできるようにした。

(もっと読む)

半導体装置およびDC−DCコンバータ

【課題】電力変換効率をより向上させる半導体装置を提供する。

【解決手段】第1のゲート配線に接続する第1のゲート電極および第1の閾値電圧を有する第1のスイッチング素子と、前記第1の閾値電圧よりも絶対値が大きい第2の閾値電圧を有し、第1のゲート配線の単位長さあたりの抵抗よりも大きい抵抗を有する第2のゲート配線に接続する第2のゲート電極を有する第2のスイッチング素子と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

電源装置

【課題】電源装置の実効的な瞬断耐力を向上し、負荷回路の電源遮断による負担を低減する。

【解決手段】入力された商用交流電力を整流する整流回路11と、整流回路11の出力電圧を昇圧して昇圧出力電圧を出力する昇圧回路12と、前記昇圧回路による昇圧後の電力の直流−直流電圧変換を行って外部の負荷に供給するDC/DCコンバータ回路13と、を備えた電源装置10において、昇圧出力電圧を検出し、所定の遮断判別電圧未満となった場合にDC/DCコンバーター回路13による負荷回路LCへの電力供給を遮断させる遮断制御回路14を備える。

(もっと読む)

1 - 20 / 88

[ Back to top ]